1.本说明书涉及通信技术领域,尤其涉及一种集成电路总线复用装置以及网络设备。

背景技术:

2.随着网络设备的密度提升,网络设备中插接的模块数量也逐渐上升,比如主控板、网板、业务板、电源以及风扇等。

3.为了对各个模块上所设置的器件(比如,网板、业务板上的端口以及温感等)或者对某些模块(比如电源或风扇等)上的数据进行获取,通常需要通过i2c(集成电路总线,inter-integrated circuit)总线实现芯片对器件或模块的连接。

4.尤其针对业务板或网板上的端口而言,由于数量较多,如何能够通过少量的芯片实现对于更多器件或模块的连接,成为本领域技术人员亟待解决的问题。

技术实现要素:

5.为克服相关技术中存在的问题,本说明书提供了一种i2c总线复用装置以及网络设备。

6.结合本说明书实施方式的第一方面,本技术提供了一种i2c总线复用装置,包括:第一复用芯片和第二复用芯片;

7.第一复用芯片,包括第一输入端、第一选路端、第二选路端以及至少两个输出端,第一复用芯片的每个输出端连接两条i2c总线的时钟线;

8.第二复用芯片,包括第二输入端、第三选路端、第四选路端以及至少两个输出端,第二复用芯片的每个输出端连接两条i2c总线的数据线;

9.其中,第一复用芯片的至少两个输出端所连接的时钟线按照序号排序分为两组,第二复用芯片的至少两个输出端所连接的数据线按照序号排序分为两组;

10.两组时钟线分别正序连接到第一复用芯片的至少两个输出端,两组数据线中的一组正序连接到第二复用芯片的至少两个输出端,两组数据线中的另一组倒序连接到第二复用芯片的至少两个输出端。

11.可选的,第一输入端、第一选路端、第二选路端连接于处理器;

12.第二输入端、第三选路端、第四选路端连接于处理器。

13.可选的,第一输入端、第一选路端、第二选路端连接于逻辑芯片;

14.第二输入端、第三选路端、第四选路端连接于逻辑芯片;

15.逻辑芯片连接于处理器。

16.结合本说明书实施方式的第二方面,本技术提供了一种网络设备,包括处理器、第一复用芯片、第二复用芯片以及目标器件;

17.第一复用芯片,包括第一输入端、第一选路端、第二选路端以及至少两个输出端,第一复用芯片的每个输出端连接两条i2c总线的时钟线;

18.第二复用芯片,包括第二输入端、第三选路端、第四选路端以及至少两个输出端,第二复用芯片的每个输出端连接两条i2c总线的数据线;

19.其中,第一复用芯片的至少两个输出端所连接的时钟线按照序号排序分为两组,第二复用芯片的至少两个输出端所连接的数据线按照序号排序分为两组;

20.两组时钟线分别正序连接到第一复用芯片的至少两个输出端,两组数据线中的一组正序连接到第二复用芯片的至少两个输出端,两组数据线中的另一组倒序连接到第二复用芯片的至少两个输出端;

21.处理器向第一复用芯片发送第一选路信号,向第二复用芯片发送第二选路信号,其中,第一选路信号用于选择第一复用芯片的至少两个输出端中的一个输出端,第二选路信号用于选择第二复用芯片的至少两个输出端中的一个输出端;

22.处理器通过第一输入端和第二输入端向所选择的第一复用芯片的输出端和所选择的第二复用芯片的输出端向所连接的同一序号的目标器件输出 i2c信号。

23.可选的,该网络设备,还包括主控板、网板和业务板;

24.处理器位于主控板,目标器件位于网板或业务板。

25.可选的,在处理器和第一复用芯片之间以及处理器和第二复用芯片之间连接器逻辑芯片。

26.可选的,逻辑芯片位于业务板。

27.可选的,目标器件为业务板或网板上的端口;

28.第一复用芯片的至少两个输出端以及第二复用芯片的至少两个输出端连接于业务板或网板的端口。

29.本说明书的实施方式提供的技术方案可以包括以下有益效果:

30.本说明书实施方式中,在复用芯片的一个输出端上连接两个目标器件所对应的时钟线或数据线,复用芯片的至少两个输出端上所连接的时钟线或数据线分为按照序号进行排序并分为两组,在一个复用芯片上时钟线或数据线中的一者,其两组分别正序连接到输出端,在另一个复用芯片上时钟线或数据线中的另一种,其两组中的一组正序连接到输出端,另一组倒序连接到输出端,形成i2c总线的复用矩阵,在两个复用芯片都选中同一目标器件时才进行数据,从而减少实现i2c总线的复用时所需的复用芯片数量,提升了复用效率。

31.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本说明书。

附图说明

32.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本说明书的实施方式,并与说明书一起用于解释本说明书的原理。

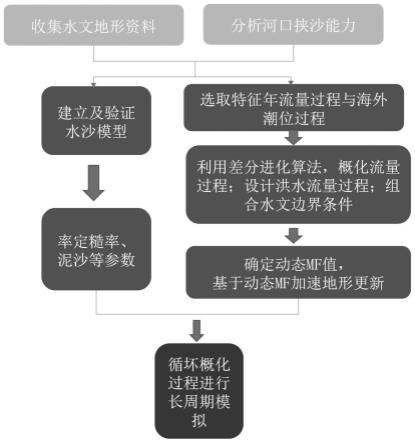

33.图1是本技术所涉及的一种i2c总线复用装置的结构示意图;

34.图2是本技术所涉及的一种网络设备的结构示意图。

具体实施方式

35.这里将详细地对示例性实施方式进行说明,其示例表示在附图中。下面的描述涉

及附图时,除非另有表示,不同附图中的相同数字表示相同或相似的要素。以下示例性实施方式中所描述的实施方式并不代表与本说明书相一致的所有实施方式。

36.本技术提供了一种i2c总线复用装置,包括:第一复用芯片和第二复用芯片。第一复用芯片和第二复用芯片可以选用相同的类型,也可以选用不同的类型。在复用芯片上,以两个8路复用芯片为例,可以包含输入端、两个选路端以及至少两个输出端。当然,在复用芯片上还可以包含有其他端,不做赘述。

37.以图1为例,第一复用芯片,用于连接i2c总线的时钟线scl,包括第一输入端a1、第一选路端、第二选路端以及至少两个输出端b11~b18,第一复用芯片的每个输出端连接两条i2c总线的时钟线。也就是说,i2c总线复用装置包含了至少两条i2c总线,这两条i2c总线用于连接目标器件,其中,目标器件可以是端口和传感器等,通过连接端口,i2c总线可以获取到该端口的状态信息,通过连接传感器,i2c总线可以获取到传感器所采集到的参数。举例来说,传感器可以是温度传感器、湿度传感器、转速传感器等等。

38.第二复用芯片,用于连接i2c总线的数据线sda,包括第二输入端a2、第三选路端、第四选路端以及至少两个输出端b21~b28,第二复用芯片的每个输出端连接两条i2c总线的数据线。

39.需要说明的是,一个选路端包含有至少两个引脚,在图1中,第一选路端包含有选路引脚s11、s12,第二选路端包含有位选引脚oe11、oe12,第三选路端包含有选路引脚s21、s22,第四选路端包含有位选引脚oe21、oe22。

40.输出端可以按照序号分为多个输出端组,比如4个输出端为一个输出端组。在图1中,第一复用芯片中,输出端b11~b14划为第一输出端组,输出端b15~b18 划分为第二输出端组;在图1中,第二复用芯片中,输出端b21~b24划为第一输出端组,输出端b25~b28划分为第二输出端组。

41.位选引脚可以用于选择输出端组。比如,针对第一复用芯片,两个位选引脚oe11、oe12的输入为01时,表示选择第一输出端组,两个位选引脚oe11、 oe12的输入为10时,表示选择第二输出端组。

42.选路引脚可以用于选择输出端组中的具体一个输出端。比如,当选择第一复用芯片的第一输出端组的情况下,两个选路引脚s11、s12的输入为00时,表示选择输出端b11;两个选路引脚s11、s12的输入为01时,表示选择输出端b12;两个选路引脚s11、s12的输入为10时,表示选择输出端b13;两个选路引脚s11、s12的输入为11时,表示选择输出端b14。比如,当选择第一复用芯片的第二输出端组的情况下,两个选路引脚s11、s12的输入为00时,表示选择输出端b15;两个选路引脚s11、s12的输入为01时,表示选择输出端 b16;两个选路引脚s11、s12的输入为10时,表示选择输出端b17;两个选路引脚s11、s12的输入为11时,表示选择输出端b18。

43.针对第二复用芯片,两个位选引脚oe21、oe22的输入为01时,表示选择第一输出端组,两个位选引脚oe21、oe22的输入为10时,表示选择第二输出端组。

44.当选择第二复用芯片的第一输出端组的情况下,两个选路引脚s21、s22的输入为00时,表示选择输出端b21;两个选路引脚s21、s22的输入为01时,表示选择输出端b22;两个选路引脚s21、s22的输入为10时,表示选择输出端b23;两个选路引脚s21、s22的输入为11时,表示选择输出端b24。当选择第二复用芯片的第二输出端组的情况下,两个选路引脚

s21、s22的输入为00 时,表示选择输出端b25;两个选路引脚s21、s22的输入为01时,表示选择输出端b26;两个选路引脚s21、s22的输入为10时,表示选择输出端b27;两个选路引脚s21、s22的输入为11时,表示选择输出端b28。

45.为了使用更少的复用芯片实现更多的复用,第一复用芯片的至少两个输出端b11~b18所连接的时钟线scl按照序号排序分为两组,第二复用芯片的至少两个输出端b21~b28所连接的数据线sda按照序号排序分为两组。即如图1 所示,时钟线scl划分为第一时钟线组和第二时钟线组,第一时钟线组中包含时钟线scl1~scl8,第二时钟线组中包含时钟线scl9~scl16,第一数据线组中包含数据线sda1~sda8,第二数据线组中包含数据线sda9~sda16。

46.两组时钟线(即第一时钟线组和第二时钟线组)分别正序连接到第一复用芯片的至少两个输出端,即时钟线scl1~scl8按照顺序连接到输出端b11~b18,并且时钟线scl9~scl16按照顺序连接到输出端b11~b18。

47.两组数据线中的一组(即第一数据线组)正序连接到第二复用芯片的至少两个输出端,即数据线sda1~sda8按照顺序连接到输出端b21~b28,两组数据线中的另一组(即第二数据线组)倒序连接到第二复用芯片的至少两个输出端,即数据线sda9~sda16倒序连接到输出端b21~b28,具体而言,数据线 sda16连接到输出端b21,数据线sda15连接到输出端b22,数据线sda14 连接到输出端b23,数据线sda13连接到输出端b24,数据线sda12连接到输出端b25,数据线sda11连接到输出端b26,数据线sda10连接到输出端b27,数据线sda9连接到输出端b28。

48.可选的,第一输入端、第一选路端、第二选路端连接于处理器;

49.第二输入端、第三选路端、第四选路端连接于处理器。

50.基于上述方式,i2c总线可以通过处理器向第一复用芯片和第二复用芯片下发选路信号,针对第一选路信号和第二选路信号可以相同也可以不同,需要根据实际的选路顺序来确定。

51.可选的,第一输入端、第一选路端、第二选路端连接于逻辑芯片;

52.第二输入端、第三选路端、第四选路端连接于逻辑芯片;

53.逻辑芯片连接于处理器。

54.基于上述方式,i2c总线还可以通过逻辑芯片向第一复用芯片和第二复用芯片下发选路信号,针对第一选路信号和第二选路信号可以相同也可以不同,需要根据实际的选路顺序来确定。该逻辑芯片接收处理器所下发的选择信号,并基于该选择信号生成相对于复用芯片的选路信号并下发给复用芯片。

55.本说明书实施方式中,在复用芯片的一个输出端上连接两个目标器件所对应的时钟线或数据线,复用芯片的至少两个输出端上所连接的时钟线或数据线分为按照序号进行排序并分为两组,在一个复用芯片上时钟线或数据线中的一者,其两组分别正序连接到输出端,在另一个复用芯片上时钟线或数据线中的另一种,其两组中的一组正序连接到输出端,另一组倒序连接到输出端,形成i2c总线的复用矩阵,在两个复用芯片都选中同一目标器件时才进行数据,从而减少实现i2c总线的复用时所需的复用芯片数量,提升了复用效率。

56.下面结合图2所示的情况对处理器进行选路的过程进行描述。其中,所选用的第一

复用芯片和第二复用芯片的结构与连接方式参见图1,包括一个输入端,两个选路端以及8个输出端。并且,两个复用芯片的输入端和两个选路端连接逻辑芯片,该逻辑芯片连接到处理器。

57.处理器可以通过逻辑芯片向复用芯片下发选路信号,从而使得对应的时钟线和数据线导通,并将输入端所接收到的时钟信号和数据信号输出到目标器件。该目标器件为业务板上所设置的端口,以业务板上设置有16个端口为例进行描述,分别为端口1~端口16。

58.在端口和复用芯片之间设置有16对i2c总线,包括时钟线scl1~scl16,数据线sda1~sda16。这些i2c总线连接在复用芯片的输出端和端口之间,具体而言,端口1~8通过时钟线scl1~scl8连接第一复用芯片的输出端b11~b18 和第二复用芯片的输出端b21~b28,端口9~16通过时钟线scl9~scl16按照第一复用芯片的输出端b11~b18的顺序连接,端口9~16通过数据线sda9~sda16 按照第二复用芯片的输出端b28~b21的顺序连接。

59.下表为位选引脚的输入、选路引脚的输入与被选择的输出端的对应关系表,其中,功能一栏指输出所对应的i2c总线,所输出的内容为输入端a1或输入端 a2所输入的数据:

[0060][0061][0062]

表1

[0063][0064]

表2

[0065]

下面分别以处理器选择导通端口1和端口16为例进行描述。处理器可以向逻辑芯片下发导通一路i2c总线的信号,逻辑芯片中可以预先存储有所下发的选择信号与对应的选路信号之间的对应关系。

[0066]

比如,在处理器下发需要导通第1对i2c总线的情况下,即向逻辑芯片下发导通第1对i2c总线的选路信号,此时,逻辑芯片在接收到选择信号后,基于上述表格所存储的对应

关系,可以确定出需要输出的选路信号为oe11=1,oe12=0, s11=0,s12=0,oe21=1,oe22=0,s21=0,s22=0,通过oe11和oe12,第一复用芯片可以从输出端b11至输出端b14之间选出输出端,并通过s11和s12 确定出输出端b11。第一复用芯片在接收到上述输入后,将输入端a1接收到的内容向第一复用芯片的输出端b11输出,即向通过时钟线scl1和时钟线scl9 分别向端口1和端口9输出i2c总线的时钟信号。通过oe21和oe22,第一复用芯片可以从输出端b21至输出端b24之间选出输出端,并通过s21和s22确定出输出端b21。第二复用芯片在接收到上述输入后,将输入端a2接收到的内容向第二复用芯片的输出端b21输出,即通过数据线sda1和数据线sda16分别向端口1和端口16输出i2c总线的数据信号。

[0067]

基于i2c总线协议,只有在目标器件(本实施方式中为端口)分别接收到了时钟信号和数据信号的情况下,触发目标器件接收并针对时钟信号和数据信号作出反馈,因此,对于端口9和端口16而言,仅接收到了时钟信号或者数据信号,不会对进行反馈,而端口1分别接收到了时钟信号和数据信号,才可以对基于时钟信号和数据信号进行反馈,从而完成基于i2c总线协议的通信。

[0068]

此处,将端口16作为目标器件进行i2c总线协议通信为例,在处理器下发需要导通第16对i2c总线的情况下,即向逻辑芯片下发导通第16对i2c总线的信号。此时,逻辑芯片基于所存储的对应关系,选路信号为oe11=0,oe12=1, s11=1,s12=1,oe21=1,oe22=0,s21=0,s22=0,通过oe11和oe12,第一复用芯片可以从输出端b15至输出端b18之间选出输出端,并通过s11和s12 确定出输出端b18。第一复用芯片在接收到上述输入后,将输入端a1接收到的内容向第一复用芯片的输出端b18输出,即向通过时钟线scl8和时钟线scl16 分别向端口8和端口16输出i2c总线的时钟信号。通过oe21和oe22,第二复用芯片可以从输出端b21至输出端b24之间选出输出端,并通过s21和s22确定出输出端b21。第二复用芯片在接收到上述输入后,将输入端a2接收到的内容向第二复用芯片的输出端b21输出,即通过数据线sda1和数据线sda16分别向端口1和端口16输出i2c总线的数据信号。

[0069]

基于i2c总线协议,只有在目标器件(本实施方式中为端口)分别接收到了时钟信号和数据信号的情况下,触发目标器件接收并针对时钟信号和数据信号作出反馈,因此,对于端口1和端口9而言,仅接收到了时钟信号或者数据信号,不会对进行反馈,而端口16分别接收到了时钟信号和数据信号,才可以对基于时钟信号和数据信号进行反馈,从而完成基于i2c总线协议的通信。

[0070]

对于处理器或处理器通过逻辑芯片导通对应的基于i2c总线的方式不做重复描述,在处理器中或者在逻辑芯片中存储需要向复用芯片下发的选路信号,在选择对应的i2c总线向目标器件发送i2c信号。

[0071]

需要说明的是,在复用芯片包含更多输出端和位选引脚的情况下,可以通过两个复用芯片连接更多的目标器件。比如,位选引脚为3个时,可以设置输出端为12个,相对应的,可以实现24个目标器件的连接,位选引脚为4个时,可以设置输出端为16个,相对应的,可以实现32个目标器件的连接,对此不做限制。

[0072]

并且,选路端的输入和被选择的输出端之间对应关系也不限于上述表1和表2所描述的对应关系,只需要实现二者不会同时选择2对i2c总线进行输出即可。

[0073]

结合本说明书实施方式的第二方面,本技术提供了一种网络设备,如图2 所示,包括处理器、第一复用芯片、第二复用芯片以及目标器件;

[0074]

第一复用芯片,包括第一输入端、第一选路端、第二选路端以及至少两个输出端,第一复用芯片的每个输出端连接两条i2c总线的时钟线;

[0075]

第二复用芯片,包括第二输入端、第三选路端、第四选路端以及至少两个输出端,第二复用芯片的每个输出端连接两条i2c总线的数据线;

[0076]

其中,第一复用芯片的至少两个输出端所连接的时钟线按照序号排序分为两组,第二复用芯片的至少两个输出端所连接的数据线按照序号排序分为两组;

[0077]

两组时钟线分别正序连接到第一复用芯片的至少两个输出端,两组数据线中的一组正序连接到第二复用芯片的至少两个输出端,两组数据线中的另一组倒序连接到第二复用芯片的至少两个输出端;

[0078]

处理器向第一复用芯片发送第一选路信号,向第二复用芯片发送第二选路信号,其中,第一选路信号用于选择第一复用芯片的至少两个输出端中的一个输出端,第二选路信号用于选择第二复用芯片的至少两个输出端中的一个输出端;

[0079]

处理器通过第一输入端和第二输入端向所选择的第一复用芯片的输出端和所选择的第二复用芯片的输出端向所连接的同一序号的目标器件输出i2c信号。

[0080]

可选的,该网络设备,还包括主控板、网板和业务板;

[0081]

处理器位于主控板,目标器件位于网板或业务板。需要说明的是,该目标器件,包括但不限于端口和传感器等。

[0082]

可选的,在处理器和第一复用芯片之间以及处理器和第二复用芯片之间连接器逻辑芯片。

[0083]

可选的,逻辑芯片位于业务板。

[0084]

可选的,目标器件为业务板或网板上的端口;

[0085]

第一复用芯片的至少两个输出端以及第二复用芯片的至少两个输出端连接于业务板或网板的端口。

[0086]

本说明书的实施方式提供的技术方案可以包括以下有益效果:

[0087]

本说明书实施方式中,在复用芯片的一个输出端上连接两个目标器件所对应的时钟线或数据线,复用芯片的至少两个输出端上所连接的时钟线或数据线分为按照序号进行排序并分为两组,在一个复用芯片上时钟线或数据线中的一者,其两组分别正序连接到输出端,在另一个复用芯片上时钟线或数据线中的另一种,其两组中的一组正序连接到输出端,另一组倒序连接到输出端,形成 i2c总线的复用矩阵,在两个复用芯片都选中同一目标器件时才进行数据,从而减少实现i2c总线的复用时所需的复用芯片数量,提升了复用效率。应当理解的是,本说明书并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。

[0088]

以上所述仅为本说明书的较佳实施方式而已,并不用以限制本说明书,凡在本说明书的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本说明书保护的范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。