1.本技术属于芯片封装技术领域,具体涉及一种复合型电子元件。

背景技术:

2.目前,复合型电子元件已大量应用于在电力仪表中,保护电力仪表设备避免损坏。为了方便生产,常用复合型电子元件的引线多为直线引线,由于各个引线引出位置不同,导致引线末端空间分布不规则。由于引线空间分布,这种结构的复合型电子元件不能进行编带包装,以至于无法适用于自动焊接,生产效率低。另外,在使用时,由于引线空间分布,会占据pcb板较大的面积,不利于器件的集成。因此,设计一种既能节约pcb板面积,且适用于自动焊接线的复合型电子元件迫在眉睫。

技术实现要素:

3.本技术的目的是提供一种复合型电子元件,其引线末端一字排列,不仅可以适用于自动生产线,还可以减小对pcb板的安装面积要求。

4.本技术实施例,提供了一种复合型电子元件,包括:

5.第一芯片,所述第一芯片具有相对的第一电极和第二电极;

6.第二芯片,所述第二芯片具有相对的第三电极和第四电极,所述第四电极和第二电极贴合连接,形成公共端;

7.第一引线,连接于所述第一电极;

8.第二引线,连接于所述第三电极;

9.第三引线,连接于所述公共端;

10.所述第一引线和所述第二引线包括弯折段和平直段,所述弯折段连接于引线与电极表面焊接连接处,两个所述平直段与所述第三引线平行且共面。

11.可选的,所述第三引线介于两个所述平直段之间。

12.可选的,所述第三引线与两个所述平直段的间距不同,根据距离的大小可以识别第一引线和第二引线。

13.可选的,所述第二引线的平直段与所述第三引线的间距大于所述第一引线的平直段和所述第三引线的间距,能够避免因第二芯片的两端出现高压,导致拉弧放电,损坏器件。

14.可选的,两个间距的差值大于0.5mm且小于5mm。

15.可选的,所述弯折段和相应平直段呈“z”字型设置。

16.可选的,所述弯折段包括第一转折段和第二转折段,所述第一转折段的一端连接于相应平直段,另一端连接于所述第二转折段。

17.可选的,两个所述平直段及所述第三引线的共面平面与所述公共端相平行。

18.可选的,所述第一芯片和所述第二芯片位于包封层内。

19.可选的,所述第一芯片为热敏电阻芯片,所述第二芯片为压敏电阻芯片。

20.本技术的上述技术方案具有如下有益的技术效果:

21.本技术实施例的复合型电子元件,通过将部分引线折弯,使各个引线末端可以一字排列,从而能够对引线末端进行编带包装,进行自动化焊接生产,有利于提高生产效率,降低生产成本。另外,由于引线末端一字排列,安装时,该复合型电子元件的引线可以焊接在一条直线上,不仅可以减小在电路板上的安装面积,而且安装面较为规则,有利于提高电路板上器件的集成度。

附图说明

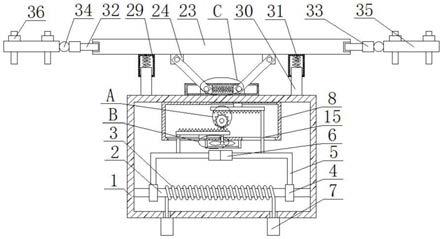

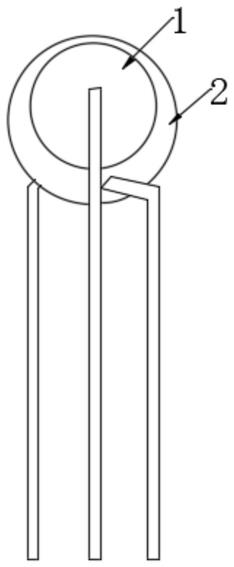

22.图1是相关技术中一种热敏压敏复合电阻的结构示意图;

23.图2是相关技术中一种热敏压敏复合电阻的封装示意图;

24.图3是图2的侧视图;

25.图4是本技术实施例中一种复合型电子元件的结构示意图;

26.图5是本技术实施例中一种复合型电子元件的封装示意图;

27.图6是图5的侧视图;

28.图7是本技术实施例中一种复合型电子元件的编带包装示意图。

29.图中,1、热敏电阻;2、压敏电阻;10、第一芯片;11、第二电极;20、第二芯片;21、第三电极;30、第一引线;40、第二引线;50、第三引线;60、包封层;70、纸带;100、弯折段;110、第一转折段;120、第二转折段;200、平直段。

具体实施方式

30.相关技术中,一种热敏压敏复合电阻,如图1-3所示,包括热敏电阻1和压敏电阻2,所述热敏电阻1的一面电极与压敏电阻2的一面电极连接在一起,形成公共端,通过引线引出;所述热敏电阻1的另一只引线与所述压敏电阻2的另一只引线分别单独引出;三个引线呈品字形分布。

31.为了节省成本与空间,工程师设计在印刷线路板(pcb)上的元件排布的越来越密;同样性能的电子元件占pcb板的面积小,更受欢迎。而上述结构的复合型电子元件的引线空间分布,安装过程中,会占据电路板上较大的面积,无法满足上述使用要求。

32.此外,随着自动化技术水平的快速发展,人工成本的增加,越来越多的企业采用适用于表面安装技术(smt)或者自动插件技术的电子元件。而上述结构的复合型电子元件由于引线空间分布,导致不能对其进行编带包装,从而无法适用于自动化的生产。

33.基于上述原因,本技术实施例提供一种新型复合型电子元件,通过将部分引线折弯,使各个引线末端可以一字排列,从而能够对引线末端进行编带包装,进行自动化焊接生产,有利于提高生产效率,降低生产成本。另外,由于引线末端一字排列,安装时,该复合型电子元件的引线可以焊接在一条直线上,不仅可以减小在电路板上的安装面积,而且安装面较为规则,有利于提高电路板上器件的集成度。

34.为使本技术的目的、技术方案和优点更加清楚明了,下面结合具体实施方式并参照附图,对本技术进一步详细说明。应该理解,这些描述只是示例性的,而并非要限制本技术的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本技术的概念。

35.在附图中示出了根据本技术实施例的层结构示意图。这些图并非是按比例绘制的,其中为了清楚的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

36.显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

37.在本技术的描述中,需要说明的是,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

38.此外,下面所描述的本技术不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

39.如图4-6所示,本技术实施例提供一种复合型电子元件,包括:

40.第一芯片10,所述第一芯片10具有相对的第一电极(图中未示出)和第二电极11;

41.第二芯片20,所述第二芯片20具有相对的第三电极21和第四电极(图中未示出),所述第四电极和第二电极11贴合连接,形成公共端;

42.第一引线30,连接于所述第一电极;

43.第二引线40,连接于所述第三电极21;

44.第三引线50,连接于所述公共端;

45.所述第一引线30和所述第二引线40包括弯折段100和平直段200,所述弯折段100连接于引线与电极表面焊接连接处,两个所述平直段200与所述第三引线50平行且共面。

46.具体的,该复合型电子元件的第一引线30和第二引线40连接电极的位置经过折弯处理,在焊接完成后,第一引线30、第二引线40和第三引线50的末端可以一字排列,且三个引线所在的平面与公共端所在的平面相平行,从而在安装时,该复合型电子元件的引线可以焊接在一条直线上,不仅可以减小在电路板上的安装面积,而且安装面较为规则,有利于提高电路板上器件的集成度。另外,由于产品的引线末端一字排列,还可以在焊接引线前先对引线进行编带包装,然后进行引线焊接,从而可以用于自动化焊接生产,有利于提高生产效率,降低生产成本。

47.在一些实施例中,该复合型电子元件还可以是折弯第一引线30与第三引线50,或者是折弯第二引线40和第三引线50。

48.在一些实施例中,所述第三引线50介于两个所述平直段200之间。

49.在一些实施例中,所述第三引线50与两个所述平直段200的间距不同。例如,所述第二引线40的平直段200与所述第三引线50的间距大于所述第一引线30的平直段200和所述第三引线50的间距,或者所述第二引线40的平直段200与所述第三引线50的间距小于所述第一引线30的平直段200和所述第三引线50的间距。需要注意的是,由于后期需要对器件进行封装,有可能不能准确识别引线,从而导致引线安装位置错误的问题,而两个不同的间距可以帮助区别第一引线30和第二引线40。例如,第二引线40的平直段200与第三引线50的间距大于第一引线30的平直段200和第三引线50的间距,那么距离第三引线50较远的一个引线就是第二引线40,距离第三引线50较近的一个引线就是第一引线30。

50.在一些实施例中,所述第二引线40的平直段200与所述第三引线50的间距大于所述第一引线30的平直段200和所述第三引线50的间距。这是由于压敏电阻在一定电流电压范围内电阻值随电压而变,若第二芯片10的两端出现高压,有可能会导致拉弧放电,损坏器件,因此,使第二引线40的平直段200与第三引线50的间距较大一些。

51.在一些实施例中,两个间距的差值应大于0.5mm且小于5mm。例如,两个间距的差值可以是1mm、2mm、3mm、4mm或5mm。需要注意的是,两个间距的差值主要是为了区分第一引线30和第二引线40,因此,差值的大小应满足人或机械能够识别的最小尺寸要求。

52.在一些实施例中,所述第一芯片10和所述第二芯片20均为圆片状,所述第一电极和所述第二电极11设于所述第一芯片10的轴向两端,所述第三电极21和所述第四电极设于所述第二芯片20的轴向两端。

53.在一些实施例中,所述第二芯片20的半径小于所述第一芯片10的半径,且所述第一芯片10的轴心与所述第二芯片20的轴心不重合。示例性的,第一芯片10半径小于第二芯片20半径,两者半径之差大于0.5mm且小于7.5mm,两者偏心连接,连接方式为采用锡膏或者焊锡焊接在一起。这是由于公共端连接的引线实际是连接在第二芯片20的第二电极11上,若第二芯片20和第一芯片10同轴设置,则第二电极11可与引线连接的面积就会大大减小。例如,第二芯片20的半径为6mm,第一芯片10的半径为3.5mm,第二芯片20与第一芯片10同轴连接后,第二电极11仅边缘1.25mm的宽度范围可供连接引线,而当第二芯片20与第一芯片10偏心连接时,第二电极11供引线连接的宽度范围最大可至2.5mm。

54.在一些实施例中,所述第三引线50连接于所述第四电极偏离所述第一芯片10的轴心的一侧。这是由于第二电极11偏离第一芯片10的轴心的一侧宽度最大,在该处焊接引线,可以保证引线与电极的有效连接。

55.在一些实施例中,所述弯折段100和相应平直段200呈“z”字型设置。

56.在一些实施例中,所述弯折段100包括第一转折段110和第二转折段120,所述第一转折段110的一端连接于相应平直段200,另一端连接于所述第二转折段120。

57.在一些实施例中,两个所述平直段200及所述第三引线50的共面平面与所述公共端相平行。

58.在一些实施例中,所述第一芯片10和所述第二芯片20位于包封层60内。其中,包封层通过绝缘材料涂封或者注塑形成,绝缘材料可以是机硅树脂、酚醛树脂和环氧树脂中的一种或多种。

59.在一些实施例中,所述第一引线30、第二引线40和第三引线50为圆引线或者扁平引线,引线的材质可以是镀锡铜包钢线、镀锡铜线、镀锡铁片或镀锡铜片等。

60.在一些实施例中,所述第一芯片10为热敏电阻芯片,所述第二芯片20为压敏电阻芯片。在其他实施例中,第一芯片10和第二芯片20还可以是其他复合型芯片组合。

61.为了进一步说明本技术实施例的技术方案,选用φ12*2.0mm压敏电阻芯片和φ7*5.0的热敏电阻芯片,对上述复合型电子元件的制作过程进行具体说明。

62.步骤一

63.采用镀锡铜包钢线作为复合型电子元件的引线,将引线裁成设定的长度并拉直,每三根为一组,按照设定的间距排列并编带包装方式进行包装,如图7所示,其中,每组引线中,第三引线50介于第一引线30和第二引线40之间,第一引线30与第三引线50的脚距为

5mm,第二引线40与第三引线50的脚距为3mm,包装所用的纸带70宽度为18mm、中心孔距为15mm。

64.步骤二

65.分别对每组引线中的第一引线30和第二引线40进行“z”字型弯折处理,得到件一。

66.步骤三

67.在压敏电阻芯片中一个电极面偏离中心的位置涂上适量锡膏,在压敏电阻芯片涂敷有锡膏的电极面上放置热敏电阻芯片,经过回流焊将两者焊接成为一体,得到件二。

68.步骤四

69.利用自动焊接生产设备对件一和件二进行自动化取件、焊接。

70.步骤五

71.焊接好后,进行有机硅树脂涂封并固化,将压敏电阻芯片和热敏电阻芯片封装在包封层内,即可得到前述实施例所述的复合型电子元件。

72.利用上述方法制备的复合型电子元件可以和纸带一起打包、运输,有助于提高打包效率,便于运输。

73.上面结合附图对本技术的实施例进行了描述,但是本技术并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本技术的启示下,在不脱离本技术宗旨和权利要求所保护的范围情况下,还可做出很多形式,均属于本技术的保护之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。