1.本发明涉及一种用于现场总线系统中的数据采集的输入/输出单元。本发明还涉及一种通过微控制器采集数字信号曲线的方法。

背景技术:

2.这类输入/输出单元以各种各样的方式应用于现场总线领域。现场总线系统应用于自动化技术、过程与工艺技术以及一般而言用于控制机器和设备,如机械手。现场总线系统在该处用于传感器的测量值采集,以及输出用于控制设备的开关信号。长期以来,特别是使用现场总线系统来在传感器中用数字传输技术替代此前常见的二进制信号的并行接线以及模拟信号传输。

3.现场总线领域的输入/输出单元通常配设有标准微控制器,其具有所谓的“通用输入/输出端(gpio-port)”。一个典型的i/o应用是,例如必须在极短的时间间隔内对数字输入端的状态进行采样,以读入数字数据。并非总是能够以所需的采样频率时间间隔来通过现场总线将这些数据传输至现场总线系统的控制器。针对这个情形,需要将“过采样”技术与数据打包相结合。其中,在所需的较短时间间隔内对信号进行采样,将采样值暂存在存储器中并且以较高的传输率以打包的方式和较大的时间间隔(取决于上级现场总线系统和其访问条件)循环地进行传输。为此,通常“传统地”对微控制器的cpu的gpio-ports的状态进行采样。每次当采样时间点到来时,对标准gpio-ports的状态进行采集,并且将逐个状态(逐位)暂存在寄存器中。在此过程中,需要调入“繁琐的”位移位例程来收集各状态,从而将这些状态打包发送。通常借助于计时器模块,通过产生相应的时钟信号来预设采样时间点。同样针对某些位移位或字移位操作为计时器编程,这些计时器在预定的时间后产生计时器中断,通过这个计时器中断来调入cpu所执行的中断服务例程(isr)。

4.由文档de10 2014 209 625 a1已知,在微控制器中使用spi接口,此微控制器同样配设有存储器直接访问控制器(dma控制器)。通过spi接口,使用dma控制器将数据在微控制器与外部存储器之间来回传输。

5.文档us 2009 024 776 a1揭示过一种微控制器,其同样配设有spi接口和dma控制器。dma控制器将从spi接口接收的数据传输至cpu核心。

6.john mangino于2007年1月所著主题为spi和dma控制器的评论文章《使用dma与高性能外设来最大限度地利用系统性能》(wwtms470 catalog applications,spna 105)同样揭示过,在通过spi接口进行数据传输时,使用dma控制器来为cpu减压。其中,外部dma控制器将spi所接收的数据写入存储器。

7.但已知解决方案具有以下缺点:使用用于暂存的处理器寄存器来将数据从i/o单元转移至工作存储器。首先,处理器将数据读入其内部寄存器,以便随后在另一步骤中将其移入工作存储器。为此,需要执行通过计时器模块触发的例程,这些例程需要多个时钟循环,在这些时钟循环中,处理器不用于执行其他指令,因此,运行的程序的执行速度下降。在通过存储器直接访问将数据从spi接口转移至存储器的已知解决方案中,不考虑通过现场

总线输出数据。

8.因此,需要一种避免上述缺点的用于现场总线系统的改进型输入/输出单元。这一点可以在本发明范围内达成。

技术实现要素:

9.本发明用以达成该目的的解决方案为根据权利要求1所述的一种用于现场总线系统中的数据采集的输入/输出单元、根据权利要求9所述的一种通过微控制器采集数字信号曲线的方法,以及根据权利要求11所述的一种微控制器。

10.从属权利要求包含本发明根据对这些措施的以下描述的有利进一步方案和改进方案参阅。

11.本发明的解决方案为一种用于现场总线系统中的数据采集的输入/输出单元,所述输入/输出单元具有标准微控制器,所述标准微控制器具有至少一个集成式同步串行接口和用于存储器直接访问的控制单元。该解决方案的特征在于,所述至少一个同步串行接口的数据输入端可以连接数字信号的信号源,且所述同步串行接口以第一时钟频率读入数据输入端上的数据。优选地,读入数据的时钟频率相当于同步串行接口的数据传输率。这样就能大幅简化将各个状态(逐位)收集和配置成数据包的过程,因为无需实施位移位例程和为此所需的计时器中断。此外,该解决方案还在于,用于存储器直接访问的控制单元将读入的数据字传输至暂存器,并且不时地从该暂存器提取出来,并传输至第二同步串行接口或另一现场总线接口,其中该第二同步串行接口或该另一总线接口连接现场总线接口,且在数据采集中以高于第一时钟频率的时钟频率通过第一同步串行接口输出读入的数据字。该解决方案的优点在于,无需调入cpu密集型例程来采集数字输入端上的数据以及将数据打包并通过现场总线传输。cpu被从数据采集和传输过程中释放出来,可以执行其他任务。同样可以使用cpu性能较低的微控制器,从而降低输入/输出单元的成本。

12.另一有利的措施在于,以打包的方式从暂存器提取数据字。可以为dma控制器相应地编程,使得cpu同样无需为此执行任何例程。

13.特别有利地,可以以至少两个同步串行接口的类型为spi接口(即串行外设接口)的微控制器来实现本发明。这个接口被广泛使用,且通常用于微控制器。

14.在一个优选方案中,如此地设计输入/输出单元,使得数据输入端连接第一spi接口的miso输入端(即主机输入,从机输出),且第一spi接口的输出端sclk、mosi和cs(即串行时钟、主机输出从机输入和片选)不连接或接地。因此,第一spi接口以非传统的方式作为主机运行,但其中该接口并非与同样包含spi接口的其他芯片连接。

15.同样极为有利地,如此地为输入/输出单元编程,使得第二时钟频率至少以某个系数高于第一时钟频率,从而使得该第二时钟频率对应于第一时钟频率的时钟频率的倍数,其中该倍数由数据字的字长决定。这个措施确保能够通过现场总线以打包的方式传输采集到的数据。

16.在一个扩展实施方式中,作为接地或不连接的替代方案,片选信号连接一或多个其他spi接口,因此,从多个spi接口中选出一或多个其他spi接口,在这些接口中以第一时钟频率读入数据输入端(miso)上的数据并且传输至暂存器。这样就能以相同的方式对多个数字输入端进行采集并且通过现场总线输出。

17.在一种有利实施方式中,输入/输出站所生成的数据包具有一个传输格式,包括头部、传输部分数据域和用户数据域,其中头部中包含地址信息,传输部分数据域中包含序列号和/或时间戳,用户数据域中包含多个编译成数据包的数据字。这样就能在上级控制控制器中简单地重新获得数字信号采集的数据包的时间顺序。为数据包单独编号。其中,包编号以序列号形式分配,从而随着传输至现场总线接口的每个新的数据包而增加。

18.其他有利方案涉及一种输入/输入单元,其中其他总线接口为uart型、usart型、i2c型总线接口或usb接口。这些接口已集成在一些标准微控制器中。

19.本发明的另一技术方案涉及一种通过微控制器采集数字信号曲线的方法,所述标准微控制器具有至少一个带全双工功能的集成式同步串行总线接口。在所述方法中,微控制器以某个时钟频率读入集成式同步串行总线接口的数字数据输入端上的数字信号,该时钟频率相当于该同步串行总线接口的数据传输率。其特别之处在于,通常与连接数据输入端的信号源连接在一起以实现全双工运行的同步串行总线接口的数据输出端未与数据源连接在一起来建立全双工连接。这样就能以节省cpu资源的方式采集数字信号。

20.其中,该集成式同步串行总线接口优选以主机运行模式运行,在该模式下,该总线接口自行预设读入数字信号的时钟。如果该时钟频率足够高,就能采集到具有相应的良好分辨率的数字信号。

21.本发明的另一技术方案涉及一种具有至少一个带全双工功能的集成式同步串行总线接口的微控制器,所述微控制器的特征在于,所述微控制器被调整为实施本发明的方法。一方面通过相应的集成式同步串行接口的输入和输出端的相应布线,另一方面通过软件来调整微控制器,使用该软件时,集成式同步串行接口的数据输出端不运行。

附图说明

22.附图示出本发明的多个实施例并且在下文中结合附图对其进行详细说明。

23.其中:

24.图1为具有两个组件,即i/o单元和控制器的现场总线系统;

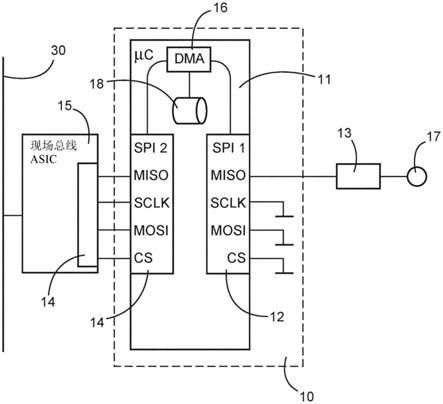

25.图2为可以用于现场总线系统的电子组件的标准微控制器的框图;

26.图3为包含i/o单元的第一框图,其中以本发明的第一方式使用标准微控制器;

27.图4为用于说明读入数字信号时的“过采样”技术的信号图;以及

28.图5为在将读入的数字信号从第二总线接口输出至现场总线接口时的数据传输过程,以及

29.图6为包含i/o单元的第二框图,其中以本发明的第二方式使用标准微控制器。

具体实施方式

30.本说明书对本发明的揭示内容的原理进行说明。可以理解的是,本领域技术人员能够设计不同的布置方案,这些布置方案在此未明确描述但体现了本发明揭示内容的原理,其范围同样应受到保护。

31.图1示出仅具有两个组件的简单现场总线系统。用参考符号10表示输入/输出单元(i/o单元)。用参考符号20、30表示控制器和现场总线本身。i/o单元以各种各样的方式应用且用于采集测量值。通常对传感器信号进行采集。用参考符号17表示传感器。可以使用不同

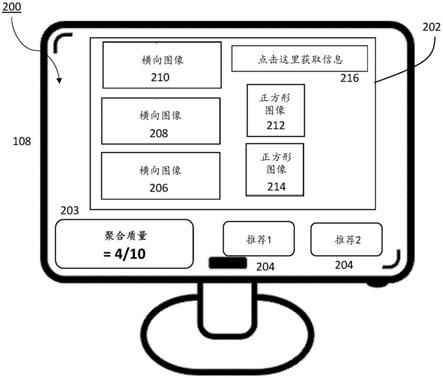

类型的传感器,将这些传感器应用于自动化领域、过程与工艺技术或者其他机器控制器。传感器包括转速传感器、温度传感器、光传感器、红外传感器、触摸传感器、麦克风、摄像机等,这并非详尽列举。现场总线系统的原理是,在车间通过i/o单元在机器或设备的不同传感器中实施测量值采集,但机器或设备的控制在集中布置的控制单元20,例如plc控制器中实施。通过现场总线30将i/o数据传输至控制单元20。考虑采用不同的已知现场总线方案作为现场总线。现场总线系统例如为联系总线、过程现场总线、工业以太网、以太网、ethercat、can总线、hart等。

32.除了用于采集传感器信号的i/o单元之外,还可以使用以下i/o单元:将之后接通特定执行器的控制信号发送至这些i/o单元。例如执行元件、泵、阀门、电动机等。

33.在i/o单元的应用中,必须以极短的时间间隔对信号,例如数字或模拟输入信号的状态进行采样。为此,通常在i/o单元中使用标准微控制器,其具有所谓的通用输入/输出端(gpio)。这样就能周期性地采集/输出数字或模拟信号。由于所连接的同样传输其他各种各样的数据的现场总线30上的通信量增大且具有相应的总线分配冲突,因此,无法总是以相同的方式在读入数据时以对应于期望的采样频率的所需时间间隔将读入的数据传输至控制器。针对这个情形,应用所谓的“过采样”技术,但该技术不应与a/d转换或d/a转换中的同名技术混淆。其中,正如控制器所需要的那样,在所需的较短时间间隔内对信号进行采样。将这些数据暂存起来,并且以较高的传输率逐块地以较大的时间间隔(取决于上级现场总线系统)循环地进行传输。也就是说,数据总是逐块地到达控制器。如果将快速传输的数据放回所需的时间网格,那么这些数据正如被读入i/o单元中那样重新存在于控制器中。

34.图2示出这种标准微控制器的框图。其涉及的是intel公司的l8051xc1型微控制器。微控制器用参考符号100表示。该微控制器包含以下组件:cpu 110、计时器模块112、实时时钟114、监控电路116、中断控制器118、协处理器120、串行接口122、通用i/o单元124、spi接口126、pc接口128、调试单元130和供电单元132。读入数字数据时的技术原理如下。

35.为此,通常“传统地”对数字输入端,例如gpio输入端的状态进行采样。每次当采样时间点到来时,对标准gpio输入端124的状态进行采集,并且将逐个状态(逐位)暂存在缓冲存储器中。在图2中,暂存器被分配在外部连接的存储模块140中。但替代地,也可以设置一个内部暂存器。但在这两种情形下cpu 110均需要调入“繁琐的”位移位例程来存储各个位状态,从而以成块收集的形式发送这些状态。通常以某种方式通过微控制器100的计时器模块112来预设期望的gpio输入端124的采样时间点,使得在预定的时间后,计时器中断调入相应的例程。这一点在从暂存器读出数据时同样适用。cpu110必须将数据编译成数据包,随后通过外部总线134传输至现场总线接口150。在此同样需要调入相应的例程来从存储模块140读取数据并且配置成数据包。但这样会导致cpu 110负载过高。

36.图3示出本发明的解决方案的第一实施例,其中示出如何用标准微控制器实施节省cpu资源的i/o操作。图3示出另一标准微控制器11。这个微控制器例如可以为以下市售的codex mx型,x为自然数[0,1,2,

…

]。例如制造商stmicroelectronics的stm32t103xc、stm32t103xd或stm32t103xe型市售微控制器。微控制器配设有内部存储器,也可以将暂存器18分配在该处。用参考符号12表示第一spi接口,用参考符号14表示第二spi接口。可以通过使用用于i/o过程的spi接口12、14来实现节省cpu资源的i/o操作。spi接口12、14相当于如今标准化的spi总线的外设模块,该外设模块在大多数微控制器中部分地双重或三重地

存在。但这些外设模块以不同于预设的方式应用。在其最初预设的工作方式中未产生任何可信的数据。但可以借助于在此所描述的构思以简单的方式实现所需的过采样。其前提是,标准微控制器具有至少一个spi接口。在所示示例中,该标准微控制器具有两个spi接口12、14。

[0037]

spi接口(serial peripheral interface,串行外设接口)为标准化的。其涉及的是同步的串行数据总线,可以根据主从原则用该数据总线将数字电路连接在一起。spi接口的其他细节参阅美国专利us 4 816 996,详细揭示内容明确参考该专利。

[0038]

设有连接每个节点的三个共用导线:

[0039]

1.sclk(串行时钟),从主机输出这个时钟以用于同步。

[0040]

2.mosi(主机输出,从机输入),作为主机运行时为输出端,作为从机运行时为输入端。

[0041]

3.miso(主机输入,从机输出),作为主机运行时为输入端,作为从机运行时为输出端。

[0042]

还可以设有第四共用导线。所谓的片选信号。

[0043]

4.cs(片选)。

[0044]

在多从机系统中,spi可以通过cs信号选择从机。原本的数字输入端“过采样”不需要片选信号。

[0045]

但同样可以用这个信号“触发”spi从机中的特定过程,使得在数据传输开始时,也就是在串行时钟信号开始同步的时间点上就已经有数据可供使用。

[0046]

替代地,也可以如此地使用这个信号,使得在具有多个数字输入端的i/o单元中通过片选信号例如“八选一”地选出数字输入端,应在该输入端上实施“过采样”。替代地,也可以视微控制器的具体“性能”“8选2”、“8选3”地选择数字输入端,在这些输入端上应用“过采样”技术。

[0047]

第一spi接口12用于读入数据。这个spi接口12在spi主机模式中运行。输入/输出端sclk和mosi(主机输出,从机输入)上的信号“进入虚空”。在所示情形下,信号简单地接地。仅输入/输出端miso(主机输入,从机输出)与信号源17(发出数字信号的传感器)连接。因此,该输入/输出端用作“数字输入端”。目前从在spi主机模式中工作的spi接口12读入的数据为在以相应的电平匹配电路13实施过电平匹配后,数字信号源17的状态。以相当于spi主机12的数据传输率的采样率对数据进行采样并将其读入。可以设计不同的sclk频率。可以在传统spi接口中设定的频率范围在数khz至数mhz之间。通过第二spi接口14将这些数据传输至现场总线接口15。为此,用于现场总线接口15的模块同样包含spi接口14。

[0048]

现还借助于图4对“过采样”技术进行更加详细的说明。该处所示处于上行中的数字信号从信号源17发出。这类信号源的典型示例为产生数字输出信号的传感器。其例如可以指光障。应对这个数字信号进行采集。用spi接口12来进行采集。这个接口以主机模式运行,并且设定一个时钟频率,该时钟频率足以实施数字信号的过采样。用来进行采样的sclk时钟信号在图4中处于中间行。其下方的行中给出采样值。每8个采样值合并成一个数据字。这些数据字在最下行中以十六进制给出。在传统方案中,一次采样过程就足以读入相应的数字状态。在“过采样”中,每个数字状态被多次读入。

[0049]

这样就能大幅简化将读入的各个位状态(逐位)收集和配置成数据字的过程,因为

无需实施导致cpu负载过高的位移位例程和为此所需的计时器中断。使用微控制器11的芯片上的dma模块16来从spi接口12提取数据字。这个模块可以在无cpu(未示出)参与的情况下将数据写入暂存器18。

[0050]

通过第二spi接口14将数据输出至连接该接口的现场总线接口15。为此,如此地为dma模块16编程,使其立即以正确的数据包大小从暂存器18提取数据,并且输出至第二spi接口14。其中,如此地为第二spi接口14编程,使其以更快的数据速率,也就是更高的sclk时钟频率将所提取的数据包在时间上有序地传输至现场总线接口15。这样就为cpu大幅减压,并且能够提供用于其他任务的计算能力,因为spi模块12、14和dma控制器16在后台工作。有利地,除了读入的数据字之外,还一起传输与现场总线相关的管理数据。为了简单地控制上级控制器20中的数字信号数据包的时间顺序,可以添加时间戳或包编号。包编号以序列号形式分配,并且随着传输至现场总线接口15的每个新的数据包而增加。时间戳同样可以已经被输入。替代地,也可以在将数据包输出至现场总线时由现场总线接口15更新时间戳。图5示出数据包dp的结构。在数据包格式的第一部分也就是头部hd中包含管理数据,也就是例如目标地址和发送者地址。在中间部分也就是传输部分数据域tf中包含时间戳和包编号。随后是原本的用户数据域pl以及数据字。用户数据域pl中例如可以有8个数据字。同样示出数据包之间的时间间隔。

[0051]

图6示出以本发明的方式用标准微控制器实现节省cpu资源的i/o操作的第二实施例。其中,相同的附图标记表示与图3相同的组件。其区别在于,在微控制器11中,不使用第二spi接口,而是用另一串行或并行总线接口来将所读入的数据字输出至现场总线接口15。如图所示,使用形式为uart接口的串行接口。相应地,在用于现场总线接口的模块15中使用uart模块19,该模块例如通过tx和rx线与uart模块19连接。

[0052]

在其他实施例中,可以使用其他串行或并行接口。例如可以使用usart接口、rs232接口、l2c接口、usb接口或firewire接口。

[0053]

这应被理解为,所提出的方法和对应的装置可以以不同形式的硬件、软件、固件、专用处理器或其组合来实施。在一个优选方案中,使用具有集成式ram存储器和集成式i/o接口的微控制器。处理器可以包括专用集成电路(asics)、精简指令集计算机(risc)和/或现场可编程逻辑门阵列(fpgas)。所提出的方法和装置优选实施为硬件和软件的组合。该软件优选作为应用程序安装在程序存储装置上。其通常是指基于计算机平台的机器,具有硬件,例如一或多个中央处理器(cpu)、一个随机存取存储器(ram)以及一或多个输入/输出(i/o)接口。计算机平台上通常还装有操作系统。在此所描述的不同过程和功能可以为应用程序的部分,或者为通过操作系统执行的部分。

[0054]

揭示内容不局限于在此所描述的实施例。存在用于本领域技术人员基于其专业知识而认为同样属于揭示内容的各种调整和变更的空间。

[0055]

附图标记说明

[0056]

输入/输出单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10

[0057]

标准微控制器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11

[0058]

第一spi接口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12

[0059]

电平匹配电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

13

[0060]

第二spi接口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

14

[0061]

现场总线接口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

15

[0062]

dma控制器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

16

[0063]

数据输入端

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

17

[0064]

暂存器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

18

[0065]

uart接口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

19

[0066]

控制单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20

[0067]

现场总线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

30

[0068]

标准微控制器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

100

[0069]

cpu

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110

[0070]

计时器模块

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

112

[0071]

实时时钟模块

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

114

[0072]

监控电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

116

[0073]

中断控制器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

118

[0074]

协处理器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

120

[0075]

串行接口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

122

[0076]

gpio-ports

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

124

[0077]

spi接口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

126

[0078]

pc接口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

128

[0079]

调试单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

130

[0080]

供电单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

132

[0081]

系统总线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

134

[0082]

外部存储器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

140

[0083]

现场总线接口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

150

[0084]

第一数据引脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

miso

[0085]

时钟信号引脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

sclk

[0086]

第二数据引脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

mosi

[0087]

选择引脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

cs

[0088]

数据包

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

dp

[0089]

头部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

hd

[0090]

传输部分数据域

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

tf

[0091]

用户数据域

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

pl

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。