1.本发明涉及真空电子技术领域。更具体地,涉及一种微通道板的制备方法及由该制备方法制备得到的微通道板。

背景技术:

2.微通道板是一种二维通道型电子倍增器,具有高增益、高分辨力、低噪声、低功耗、长寿命优点,广泛用于微光像管、光电倍增管、阴极射线管、摄像管和x射线探测器等。

3.传统微通道板制备主体基于玻璃管拉伸技术:采用铅硅酸盐玻璃管作为通道玻璃,在玻璃管内部插入可酸溶解的玻璃棒芯,将玻璃管密排并横向压缩、纵向拉伸后切成薄片成为板坯,板坯经过研磨和抛光,通过酸腐蚀溶解玻璃棒芯形成微通道板基体,对基体通氢气加热,将硅酸盐玻璃基体中的铅还原,在微玻璃管内壁形成导电层和发射层,最后在微通道板基体两端蒸镀金属形成输入、输出电极完成制作。在微通道板两端加电压,输入端电子在微通道内不断撞击发射层产生增额二次电子,从而对微弱的二维电子图像进行倍增或放大。

4.然而,传统的微通道板工艺,材料相对固定,存在铅硅酸盐玻璃材料多纤维拉制和氢还原处理相互牵制的矛盾,使其难以在使用寿命、动态范围、空间分辨能力和信噪比方面深度挖潜,限制了它在很多方向特别是空间探测、微光夜视、大屏幕显示领域的应用。

5.随着微电子机械系统技术的发展,使用微加工技术制备微通道板成为可能,美国专利us 5086248和us 5997713分别提出基于硅材料制备微通道板的微加工工艺方法,其基本工艺流程如图1所示:首先应用干法深反应离子刻蚀(drie)技术,或者电化学和光电化学腐蚀技术,在硅片上制备密排高长径比通孔作为电子传输通道202,未去除硅材料形成微通道板基体201;而后通过热氧化或化学气相沉积(cvd),在半导体硅微通道板基体201表面包括外表面及电子传输通道202内壁形成氧化绝缘层203,或者对201彻底热氧化形成整体绝缘;然后再通过化学气相沉积(cvd)或原子层沉积(ald)方法,在氧化绝缘层203表面包括外表面及电子传输通道202内壁制作电子倍增层204;最后通过薄膜沉积方法,仅在形成基材结构上下两端面制作输入电极205和输出电极206完成制备。

6.上述专利方法制备硅基微通道板,工艺流程兼容微加工技术,容易实现各种不同形状和尺寸的高长径比微通道阵列结构,具有较好的工艺重复性和批量制作能力;并且该方法将微通道基底与电子倍增实行材料和工艺双分离,一方面解决了玻璃多纤维拉制和氢还原处理相互牵制矛盾,一方面也给采用新材料和新工艺制作二次电子发射层提供了条件。因而该方法制备硅基微通道板,相对传统玻璃方法具有通道孔径小、工作面积大、动态范围宽、光谱响应范围宽、耐高温等优点。

7.然而,上述专利方法制备硅基微通道板,也存在固有缺点,影响其性能提高,集中表现在:

8.1)使用深反应离子刻蚀(drie)技术制备微通道通孔,大深宽比孔(harp)结构刻蚀

大部工艺流程处于深窄盲孔中,气体和气态生成物的输运仅有深度方向一个自由度,气体运动阻力随孔的深度增加急剧增大,会导致刻蚀过程中速度越来越慢,出现严重纵向条带式不均匀分布,通道中下部非均匀性严重,并存在尺寸效应等,使得drie工艺极具挑战。

9.2)微通道板要求很好耐高电压性能,需要对硅基基体进行绝缘处理。然而低气压化学气相沉积(lpcvd)在硅表面制作二氧化硅或氮化硅绝缘薄膜耐压值通常300-400v,不能满足要求。而热氧化方法完全氧化硅基材或制作几微米以上厚度二氧化硅,则需要在1100℃温度至少保持几十小时,很容易使得微通道板产生形变导致制备失败,并且面积越大、基体越薄、则形变越严重。

10.3)在微通道通孔内壁制作电子倍增材料层,采用化学气相沉积(cvd)方法,难以在大深宽比细管内壁实现均匀膜层覆盖,以及各微管之间一致性;而使用原子层沉积(ald)方法,虽然可以得到均匀膜层,但该方法适用前提是需要合适的前驱体,只能限定少量特定材料,大大限制了可用材料的种类。

11.针对上述情况,本发明提供了一种微通道板制备方法,解决了上述硅基微通道板微加工专利存在的深硅刻蚀大深宽比孔微孔不均匀、高温长时间氧化导致微通道板基材变形,以及微通道通孔内壁制作膜层不均匀和材料限制等问题。

技术实现要素:

12.基于以上事实,本发明的目的在于提供一种微通道板的制备方法及由该方法制备得到的微通道板,以解决现有技术中微通道板的制备过程中存在的大深宽比孔微孔刻蚀、基材高温长时间处理变形以及微通道内壁薄膜材料均匀制作难的问题。

13.一方面,本发明提供一种微通道板的制备方法,该制备方法包括如下步骤:

14.提供基底;

15.在基底的一个表面上的预选位置形成柱形阵列;

16.在所述基底和柱形阵列的表面上沉积电子倍增材料,形成电子倍增层;

17.在电子倍增层上施加绝缘材料至完全覆盖柱形阵列,形成绝缘层;

18.对得到的结构中绝缘层所在的表面进行磨平、抛光,直至露出柱形阵列的顶端;

19.去除基底并对该结构中与基底相结合的表面进行研磨、抛光,至露出柱形阵列的底端;

20.去除柱形阵列,得到具有通孔且通孔上包覆有电子倍增层的绝缘层结构;

21.分别在该绝缘层结构的上下表面上除通孔外的地方沉积导电材料,形成输入电极和输出电极;

22.得到所述微通道板。

23.进一步地,形成柱形阵列的方式为微加工。

24.进一步地,所述柱形阵列的形状为圆柱、方柱或六棱柱。

25.进一步地,所述柱形阵列中,柱体间隙为4-6微米,单个柱体的直径或对边长度为6-40微米,柱体高度为160-400微米,柱体的高宽比为10-40。

26.进一步地,所述柱形阵列的材料与基底相同或选自厚光刻胶。

27.进一步地,所述电子倍增材料选自掺杂/非掺杂多晶硅、金属氧化物中的一种或几种。

28.进一步地,所述电子倍增层的厚度为10-100nm。

29.进一步地,所述绝缘材料为耐高电场击穿的绝缘材料。

30.进一步地,施加绝缘材料的方式选自填充固化、填充烧结、化学气相沉积、真空镀膜中的一种。

31.进一步地,所述基底为表面光滑平整的硅片、金属片或玻璃片。

32.进一步地,所述基底的厚度为400-2000微米。

33.进一步地,去除基底的方法选自腐蚀或研磨、抛光。

34.进一步地,去除柱形阵列的方法为腐蚀。

35.进一步地,沉积导电材料的方法为薄膜沉积法。

36.进一步地,所述导电材料选自铬镍、钛镍、铬金、钛金中的一种。

37.进一步地,所述输入电极和输出电极的厚度各自独立地选自100-300nm。

38.又一方面,本发明提供如上所述的制备方法制备得到的微通道板。

39.本发明的有益效果如下:

40.本发明的制备方法中,使用了预制模具而后加工微通道板的方法,有效地克服了现有微通道板微加工方法只能依赖硅材料、以及硅材料特定工艺流程的制约的问题,本发明制备方法中,不仅工艺简单、成本低,而且理论上避免了材料限定性,以及材料特性差异导致制备工艺之间的相互影响,材料和加工工艺具有多样性选择,能够实现更优良结构及器件性能。

附图说明

41.下面结合附图对本发明的具体实施方式作进一步详细的说明。

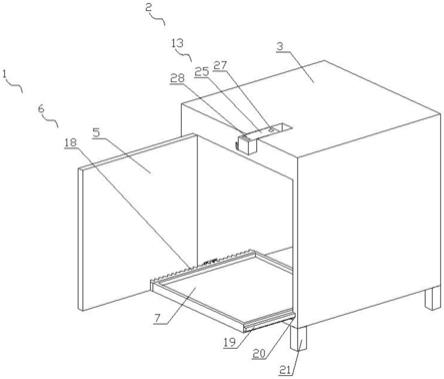

42.图1示出现有硅微通道板制备工艺流程图。

43.其中,201-微通道板基体、202-电子传输通道、203-氧化绝缘层、204-电子倍增层、205-输入电极、206-输出电极。

44.图2a-图2c分别示出深反应离子刻蚀深孔、深反应离子刻蚀高柱、厚胶光刻高柱微加工大深宽比孔结构和微加工大深宽比柱结构对比。

45.图3a-图3f示出本发明的微通道板制备工艺流程图。

46.其中,301-基片、302-柱形阵列、401-电子倍增层、402-微通道板基体(也即绝缘层)、403-电子传输通道(也即通孔)、404-输入电极、405-输出电极。

47.图3g示出本发明的微通道板的结构示意图。

具体实施方式

48.为了更清楚地说明本发明,下面结合优选实施例和附图对本发明做进一步的说明。附图中相似的部件以相同的附图标记进行表示。本领域技术人员应当理解,下面所具体描述的内容是说明性的而非限制性的,不应以此限制本发明的保护范围。

49.在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上;术语“上”、“下”、“左”、“右”、“内”、“外”、“前端”、“后端”、“头部”、“尾部”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对

本发明的限制。

50.根据本发明的一个具体实施方式,提供一种微通道板的制备方法,如图3a-3f中所示,包括如下步骤:

51.1)提供基底301。

52.适用于本实施方式中的基底301可为光滑平整的基片,示例性的基底301包括但不限于表面抛光硅片、金属片、玻璃片或平整度和粗糙度满足微加工特别是光刻工艺要求的其他材料。

53.基底301的尺寸优选为微加工标准尺寸,例如2吋、3吋、4吋、6吋或者微加工能够实现的大于6吋标准基片和非标准基片。

54.基底301的合适厚度优选为400-2000微米。

55.2)在基底301的一个表面上的预选位置形成柱形阵列302,如图3a所示。

56.柱形阵列302的大小和形状对应最终要制备得到的微通道板中的通孔(也即微通道板中的有效实用面积)的大小和形状。柱形阵列302中,柱体外形对应微通道板的内孔,柱体间隙对应微通道板的通道壁厚,柱体高度对应微通道板的厚度。

57.柱形阵列302的形状包括但不限于为圆柱、方柱或六棱柱等。

58.柱形阵列302中,柱体间隙优选为4微米左右,单个柱体的直径或对边长度优选为6-40微米,柱体高度优选为160-400微米,柱体的高宽比优选为10-40。

59.形成柱形阵列302的材料与基底301相同或选自厚光刻胶(例如如su8和kmpr)或者适合形成大深宽比柱形结构的其他材料。

60.形成柱形阵列302的方法可为微加工法。具体的,可为深反应离子刻蚀(drie,加工硅),厚胶光刻技术(加工厚胶su8或kmpr),或者其他适用微加工技术如飞秒激光等。

61.柱形阵列302的图形,可根据需要设计尺寸范围,或者将柱形阵列302的图形密布整个基片,完成制备后根据需要切割成适合尺寸。

62.和现有硅微通道板微加工方法相比,本发明的制备方法中有更多加工技术可选如厚胶光刻等。即便同样使用深反应离子刻蚀技术加工微通道阵列,但由于加工结构由深孔加工变更为高柱加工,相应大深宽比孔(harp)结构刻蚀变更为大深宽比槽(hart)结构刻蚀,气体和气态生成物的输运由仅有深度方向1个自由度变更为深度和柱形间隙横向2个自由度,极大提高了结构加工质量,也即柱结构加工质量优于孔加工。图2a为现有技术中,深反应离子刻蚀得到的微加工大深宽比孔结构,图2b为本实施方式中深反应离子刻蚀的微加工大深宽比柱结构,以及图2c为本实施方式中厚胶光刻的微加工大深宽比柱结构。从图2a中可知,现有技术得到的大深宽比孔深度不一致、均匀性差。且由于处理过程中涉及高温,材料易于高温变形。从图2b和2c中可知,本技术中先制备得到高度均匀的大深宽比柱结构,在此基础上后续形成外包材料后,再去除该大深宽比柱结构得到的通孔自然高度一致且均匀性好。且本实施方式的方法中,不涉及高温过程,不存在变形,因此,更有利于制备得到高度一致且均匀的通孔。

63.3)在所述基底301和柱形阵列302的表面上沉积电子倍增材料,形成电子倍增层401,如图3b所示。

64.沉积电子倍增材料的方法可为薄膜沉积法。具体可包括但不限于溶液超声沉淀法、溶胶凝胶法、真空镀膜法、化学气相沉积法等。

65.通过沉积,可知,在基底301的上表面和柱形阵列302的外表面上均沉积的有电子倍增材料。

66.电子倍增材料为传统掺杂/非掺杂多晶硅、金属氧化物或其他兼具导电和电子倍增特性的新型材料等;其中,金属氧化物优选包括但不限于氧化镁、氧化铟锡、氧化锑锡等。

67.所述电子倍增层401的厚度优选为10-100nm。

68.本实施方式的制备方法中,将电子倍增层制备工艺流程,从现有的大深宽比管道内壁涂覆变更为结构外表面施加,大大降低了工艺难度,有利于选择更多材料种类,实现更好的涂覆均匀性和一致性,提高微通道板性能。

69.4)在电子倍增层401上施加绝缘材料至完全覆盖柱形阵列302,形成绝缘层402(也即微通道板基体),如图3c所示。

70.施加绝缘材料的方式优选为填充固化、填充烧结、化学气相沉积、真空镀膜中的一种。

71.施加绝缘材料的方式可为在基底301上的柱形阵列302间隙内填充/沉积绝缘材料,直至完全掩盖柱形阵列302图形结构,该绝缘材料用作后续形成微通道板基体结构材料。

72.施加的绝缘材料完全掩盖柱形阵列302图形结构,使得绝缘层402的厚度大于柱形阵列302的高度。

73.为了易于致密成型、强度牢靠、能耐受高电场击穿的绝缘材料包括但不限于树脂、玻璃、石英、陶瓷等。

74.直接使用绝缘材料制备微通道板基体,避免了现有硅微通道板微加工方法高温长时间氧化过程,以及由此带来的基体变形;即便使用高温工艺,由于基片和微通道结构互不相关,也能够通过增加基片厚度有效减弱变形程度。

75.5)对得到的结构中绝缘层402所在的表面进行磨平、抛光,直至露出柱形阵列302的顶端,如图3d所示。

76.可以理解,通过磨平、抛光,依次去除了部分厚度的绝缘层402以及位于柱形阵列302顶端的全部电子倍增层401部分,进而使得经过磨平、抛光后得到的表面上刚好露出柱形阵列302的顶端。

77.磨平、抛光的方法优选为化学机械抛光(cmp)。

78.通过该方法,实现了绝缘层402(微通道板基体)和电子倍增材料的分离,克服了传统微通道板管材拉伸技术制备方法存在铅硅酸盐玻璃材料多纤维拉制和氢还原处理相互牵制的矛盾,材料选择多样性还有利于提高微通道板性能。

79.6)去除基底301并对该结构中与基底301相结合的表面进行研磨、抛光,至露出柱形阵列302的底端;以及,进一步去除柱形阵列302,得到具有通孔403(也即电子传输通道)且通孔403上包覆有电子倍增层401的绝缘层结构,如图3e所示。

80.去除基底301的方法包括但不限于腐蚀或研磨、抛光。

81.对该结构中与基底301相结合的表面进行研磨、抛光也即去除与基底301相结合的电子倍增层401部分。

82.其中,上述研磨、抛光的方法优选为化学机械抛光(cmp)。

83.进一步去除柱形阵列302的方法可为腐蚀,腐蚀的方法为湿法化学腐蚀,根据基底

301和柱形阵列302材料相同/不同,选择相同/不同化学腐蚀液,该腐蚀液应对其他材料具良好腐蚀选择性,也即该腐蚀去除过程不能损伤微通道板绝缘基体和电子倍增层401。

84.7)分别在该绝缘层结构的上下表面上除通孔403外的地方沉积导电材料,形成输入电极404和输出电极405,如图3f所示。

85.沉积导电材料的方法优选为薄膜沉积法。示例性的薄膜沉积的方法,为微通道板绕端面法线自转、掠角沉积、方向性良好的真空蒸发镀膜方法。为保证沉积层仅位于微通道板上下端面而不进入电子通道,使蒸发源远离并和微通道板端面保持很小的掠角进行倾斜蒸镀。同时为保证均匀性,蒸镀过程中微通道板绕端面法线自转。

86.为兼具结合牢靠性和良好导电性,所述导电材料包括但不限于选自铬镍、钛镍、铬金、钛金中的一种。

87.所述输入电极404和输出电极405的厚度各自独立地选自100-300nm。

88.本发明的又一个具体实施方式提供一种如上述方法制备得到的微通道板,其结构如图3g所示。

89.实施例1

90.一种微通道板,如图3所示,包括电子倍增层401,微通道板基体402,电子传输通道403,输入电极404和输出电极405。

91.其制备方法包括如下步骤:

92.1)选用《100》晶向抛光硅片作为基底301,硅片直径4英寸、厚度500微米、表面平整度和翘曲度优于10微米;硅片表面热氧化0.5微米二氧化硅和磁控溅射1微米金属铝,通过标准光刻、刻蚀二氧化硅和金属铝为掩蔽层;使用sts公司bosch专利深硅刻蚀技术,刻蚀硅基片形成柱形阵列302;刻蚀功率600w/15w,刻蚀速率1.5μm/min,刻蚀时间200min,刻蚀深度300微米;根据设计图形,在硅片上得到密布六边形柱形阵列302,柱形对边距离15微米,柱型间隙4-6微米,柱形高度300微米,柱形高宽比20。

93.2)使用磁控溅射方法,氩气和氧气为放电气体,同时沉积镁和金,得到氧化镁/金复合膜层作为电子倍增层401,其中氧化镁层用作电子倍增,金层增强导电性。衬底加热500℃,氩气流量25sccm,氧气流量5sccm,镁靶功率100w、金靶功率7w,膜层沉积速率约为10nm/min,沉积10分钟得到电子倍增层401厚度约为100nm。

94.3)使用电子束蒸发方法,向基片和柱形阵列间隙蒸镀95%氧化铝陶瓷,形成微通道板基体402。蒸发功率2kw,蒸发速率2μm/min,蒸发时间160min,得到氧化铝陶瓷微通道板基体402厚度约320μm,完全覆盖高度300μm的柱形阵列302。

95.4)采用化学机械抛光方法,以金刚石粉为磨料,对氧化铝陶瓷微通道板基体402实施磨平、抛光。初始采用粒度10微米磨料、200rpm转速快速研磨,将氧化铝陶瓷基体厚度降低至300微米;然后采用1微米磨料、60rpm转速慢速抛光,直至磨透硅基柱形阵列302顶部氧化铝陶瓷基体402和氧化镁/金复合电子倍增层401,露出硅材料。

96.5)用氢氧化钾溶液腐蚀硅材料,完全去除基底301和柱形阵列302,并对下表面研磨、抛光电子倍增层401,直至露出氧化铝陶瓷微通道板基体402。使用氢氧化钾溶液浓度30%,腐蚀温度80℃,硅材料腐蚀速率约为1μm/min;对该结构采用200微米基片301和300微米柱形阵列302,实行300分钟过腐蚀(双面腐蚀),确保去除所有硅材料(柱形阵列存在细窄通道包覆去除有难度),在原来柱形阵列302位置由于材料去除,形成了电子传输通道403。

由此得到了由电子倍增层401,微通道板基体402和电子传输通道403组成的微通道板结构。蜂窝状电子传输通道403形状对应柱形阵列,六边形通孔对边距离15微米,壁厚4微米,深度300微米。

97.6)通过电子束蒸发沉积方法,在微通道板上端面沉积导电材料制作输入电极404。蒸发时靶源远离微通道板,和端面呈15度入射掠角,同时微通道板沿端面法线方向自转,保证蒸发物均匀沉积在表面而不进入电子传输通道403。输入电极404为20nm钛和100nm镍的复合膜层。同样方法在微通道板下端面制备输出电极405。

98.实施例2

99.一种微通道板,包括电子倍增层401,微通道板基体402,电子传输通道403,输入电极404和输出电极405。

100.其制备方法同实施例1,不同之处在于:

101.步骤1)中选用《100》晶向抛光硅片作为基底301,硅片直径4英寸、厚度500微米、表面平整度和翘曲度优于10微米;用800rpm转速在基底301表面旋涂300微米厚度su8-2150光刻胶,95℃前烘60分钟,根据设计图形600mj/cm2剂量曝光,95℃后烘60分钟,su8 developer显影45分钟,在硅片上得到密布六边形柱形阵列302,柱形对边距离15微米,柱型间隙4微米,柱形高度300微米,柱形高宽比20。

102.步骤3)中使用化学气相沉积方法,向基片和柱形阵列间隙沉积二氧化硅,形成微通道板基体402。得到氧化铝陶瓷微通道板基体402厚度约320μm,完全覆盖高度300μm的柱形阵列302。

103.步骤5)中使用氢氧化钾溶液腐蚀去除基底301,并对下表面研磨、抛光电子倍增层401,直至露出氧化铝陶瓷微通道板基体402。使用去胶剂去除柱形阵列302。使用氢氧化钾溶液浓度30%,腐蚀温度80℃,硅材料腐蚀速率约为1μm/min,大约500分钟完全去除厚度500微米基底301;使用su8专用去胶剂remover pg,确保去除所有su8-2150光刻胶,在原来柱形阵列302位置由于材料去除,形成了电子传输通道403。由此得到了由电子倍增层401,微通道板基体402和电子传输通道403组成的微通道板结构。蜂窝状电子传输通道403形状对应柱形阵列,六边形通孔对边距离15微米,壁厚4微米,深度300微米。

104.结论:本发明意外地发现,使用预制模具后加工方法制备微通道板,不仅工艺简单、成本低,而且理论上避免了材料限定性,以及材料特性差异导致制备工艺之间相互影响,能最大程度以优化工艺方法得到高质量结果。本发明提出的方法简便易行、成本较低、可选材料范围宽,适应科学研究和实用化的迫切需要。

105.显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定,对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动,这里无法对所有的实施方式予以穷举,凡是属于本发明的技术方案所引伸出的显而易见的变化或变动仍处于本发明的保护范围之列。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。