e1链路的随路时钟抖动抑制方法、装置及电子设备

技术领域

1.本技术涉及数据通信技术领域,具体而言,涉及一种e1链路的随路时钟抖动抑制方法、装置及电子设备。

背景技术:

2.在数据通信,尤其在路由器sdh oc3 155m接口的cpos广域板卡中,cpos广域卡中有63个2048khz的低速e1物理信道。e1链路的时钟是随路时钟(时钟隐含在数据中),而从sdh中提取的e1链路的随路时钟抖动非常大,即随路时钟的时钟频率在随机地不断变化,且变化幅度比较大,继而导致各个e1链路对应的寄存器中的数据的移出速率随机地不断变化,且变化幅度特别大,从而需要进行抖动抑制。

技术实现要素:

3.鉴于此,本技术实施例的目的在于提供一种e1链路的随路时钟抖动抑制方法、装置及电子设备,以解决上述问题。

4.第一方面,本技术实施例提供一种e1链路的随路时钟抖动抑制方法,应用于fpga,所述方法包括:在从数据队列读取预设字节的数据到寄存器之后,获取表征所述数据队列中所存储数据的数据量的信号;根据所述信号,确定出对应的时钟频率;根据所述对应的时钟频率,将所述寄存器中的数据移出所述寄存器。

5.在上述实现过程中,在从数据队列读取预设字节的数据到寄存器之后,根据表征所述数据队列中所存储数据的数据量的信号,确定出对应的时钟频率,可以理解的是,时钟频率是和数据队列中所存储数据的数据量呈一定关系的,继而能根据所述对应的时钟频率,以与所述对应的时钟频率对应的速率稳定地将所述寄存器中的数据移出所述寄存器,从而解决了现有技术中由于sdh携带的e1链路的随路时钟抖动非常大而导致数据的移出速率随机地不断变化,且变化幅度特别大的问题。

6.基于第一方面,在一种可能的设计中,所述根据所述信号,确定出对应的时钟频率,包括:根据所述信号确定出所述数据量;根据所述数据量和预先确定的数据大小的范围划分准则,确定出与所述数据量对应的数据范围;从预先确定的数据范围与时钟频率的对应关系中,查找出与所述对应的数据范围对应的时钟频率。

7.由于数据队列中所存储的数据的数据量的大小可能在不断地发生变化,若不同的数据量所对应不同的时钟频率不合理,则无法很好地解决数据移出的速率抖动大的问题,因此,为了能够快速、准确、合理地确定出所述信号对应的时钟频率,以更好地解决数据移出的速率抖动大的问题,在上述实现过程中,通过预先建立数据范围和时钟频率的对应关系,并根据所述信号确定出的数据量,继而根据所述数据量和预先确定的数据大小的范围划分准则,准确地确定出与所述数据量对应的数据范围,从而能从数据范围与时钟频率的对应关系中,快速、准确地查找出与所述对应的数据范围对应的时钟频率,可以理解的是,由于一个数据量范围对应一个时钟频率,因此,即使数据队列中所存储的数据的数据量的

大小在不断地发生变化,既能保证数据队列中所存储的数据不会被读空或者发生溢出,也能保证数据从寄存器中平稳地移出。

8.基于第一方面,在一种可能的设计中,在所述查找出与所述对应的数据范围对应的时钟频率之前,所述方法还包括:根据预先确定的e1链路的标准时钟的大小,确定出所述对应关系。

9.虽然sdh携带的e1链路的随路时钟抖动比较大,但是e1链路的随路时钟在进入sdh前是符合e1链路的标准时钟的,因此,在上述实现过程中,根据预先确定的e1链路的标准时钟的大小,确定出所述对应关系中的时钟频率,由于对应关系中的各个时钟频率与所述标准时钟相关,继而能够保证对应关系中的时钟频率的合理性。

10.基于第一方面,在一种可能的设计中,所述根据预先确定的e1链路的标准时钟的大小,确定出所述对应关系,包括:根据所述标准时钟的大小和预先确定的参考时钟的大小,确定所述对应关系。

11.在上述实现过程中,通过利用参考时钟的大小和标准时钟的大小,就可以得到所述对应关系中的各个时钟频率的时钟,继而无需利用额外的时钟来控制寄存器中的数据移出速率,简化fpga的设计难度。

12.基于第一方面,在一种可能的设计中,在从数据队列读取预设字节的数据到寄存器之前,所述方法还包括:在确定所述寄存器中未存储数据时,从所述数据队列中读取所述预设字节的数据到所述寄存器。

13.在上述实现过程中,在确定所述寄存器中未存储数据时,才从所述数据队列中读取所述预设字节的数据,以保证所述预设字节的数据能够被一次性读取到寄存器中,继而避免所述寄存器中还未移出的数据被覆盖,也确保将所述预设字节的数据按照某个选定的时钟频率均匀移出。

14.基于第一方面,在一种可能的设计中,所述方法还包括:在每次检测到所述数据队列中被写入数据或者被读取数据之后,确定出当前时刻所述数据队列中所存储数据的数据数量;根据所述数据量,更新所述信号。

15.在上述实现过程中,通过这种方式能够及时对表征所述数据队列中的数据量的信号进行更新,以确保后续能够以准确地时钟频率移出寄存器中存储的数据。

16.第二方面,本技术实施例提供一种e1链路的随路时钟抖动抑制装置,应用于fpga,所述装置包括:信号获取单元,用于在从数据队列读取预设字节的数据到寄存器之后,获取表征所述数据队列中所存储数据的数据量的信号;时钟频率确定单元,用于根据所述信号,确定出对应的时钟频率;移出单元,用于根据所述对应的时钟频率,将所述寄存器中的数据移出所述寄存器。

17.基于第二方面,在一种可能的设计中,所述时钟频率确定单元,具体用于根据所述信号确定出所述数据量;以及根据所述数据量和预先确定的数据大小的范围划分准则,确定出与所述数据量对应的数据范围;从预先确定的数据范围与时钟频率的对应关系中,查找出与所述对应的数据范围对应的时钟频率。

18.基于第二方面,在一种可能的设计中,所述装置还包括:对应关系确定单元,用于根据预先确定的e1链路的标准时钟的大小,确定出所述对应关系。

19.基于第二方面,在一种可能的设计中,所述对应关系确定单元,具体用于根据所述

标准时钟的大小和预先确定的参考时钟的大小,确定所述对应关系。

20.基于第二方面,在一种可能的设计中,所述装置还包括:读取单元,用于在确定所述寄存器中未存储数据时,从所述数据队列中读取所述预设字节的数据到所述寄存器。

21.基于第二方面,在一种可能的设计中,所述装置还包括:更新单元,用于在每次检测到所述数据队列中被写入数据或者被读取数据之后,确定出当前时刻所述数据队列中所存储数据的数据数量;以及根据所述数据量,更新所述信号。

22.第三方面,本技术实施例提供一种电子设备,包括处理器以及与所述处理器连接的存储器,所述存储器内存储计算机程序,当所述计算机程序被所述处理器执行时,使得所述电子设备执行第一方面所述的方法。

23.第四方面,本技术实施例提供一种计算机可读取存储介质,所述存储介质中存储有计算机程序,当所述计算机程序在计算机上运行时,使得所述计算机执行第一方面所述的方法。

24.本技术的其他特征和优点将在随后的说明书阐述,并且,部分地从说明书中变得显而易见,或者通过实施本技术实施例了解。本技术的目的和其他优点可通过在所写的说明书、权利要求书、以及附图中所特别指出的结构来实现和获得。

附图说明

25.为了更清楚地说明本技术实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本技术的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

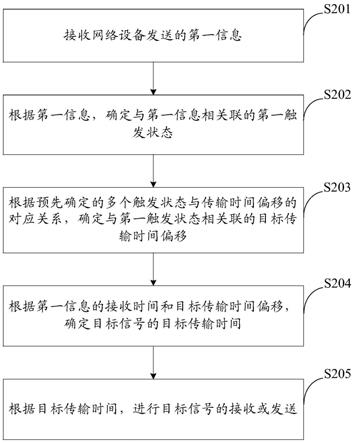

26.图1为本技术实施例提供的e1链路的随路时钟抖动抑制方法的流程示意图。

27.图2为本技术实施例提供的e1链路的随路时钟抖动抑制装置的结构示意图。

28.图3为本技术实施例提供的电子设备的结构示意图。

29.图标:200-e1链路的随路时钟抖动抑制装置;210-信号获取单元;220-时钟频率确定单元;230-移出单元;300-电子设备;301-处理器;302-存储器;303-寄存器。

具体实施方式

30.下面将结合本技术实施例中附图,对本技术实施例中的技术方案进行描述。

31.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。同时,在本技术的描述中,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

32.请参照图1,图1为本技术实施例提供的一种e1链路的随路时钟抖动抑制方法的流程图,所述方法应用于fpga,下面将对图1所示的流程进行详细阐述,所述方法包括步骤:s11、s12和s13。

33.s11:在从数据队列读取预设字节的数据到寄存器之后,获取表征所述数据队列中所存储数据的数据量的信号。

34.s12:根据所述信号,确定出对应的时钟频率。

35.s13:根据所述对应的时钟频率,将所述寄存器中的数据移出所述寄存器。

36.下面对上述方法进行详细介绍。

37.作为一种实施方式,所述方法还包括:在每次获取到一个sdh信号之后,根据该sdh信号的帧结构,对该sdh信号进行解析,得到63个e1链路的数据,其中,每个e1链路的数据中包括:8bit的e1数据、写使能信号和通道号;其中,不同的e1链路所对应的通道号不同,e1链路和通道号是一一对应的关系;针对每个e1链路的数据,按照该e1链路的数据中的通道号和写使能信号,将该e1链路中的e1数据写入与所述通道号对应的数据队列中,其中,通道号与数据队列为一一对应的关系。

38.其中,写使能信号可以理解为指示将e1数据写入数据队列的时间的提示信息。

39.针对每个数据队列,利用一个表征所述数据队列所存储数据的数据量的信号来表征该数据队列的状态。

40.其中,所述信号中携带的信息可以是所述数据量,也可以是表征所述数据量大小的水位信息;其中,水位信息的种类为至少两种;在本实施例中,所述水位信息的种类为三种,分别是低水位、中水位和高水位,在其他实施例中,所述水位信息的种类也可以为两种、四种等,根据实际需求设定。

41.值的一提的是,水位信息根据预先确定的水位信息确定准则确定。

42.其中,在本实施例中,水位信息确定准则可以是:在确定所述数据量小于等于第一预设值时,确定所述水位信息为低水位;在所述数据量大于所述第一预设值小于等于第二预设值时,确定所述等级信息为中水位;在确定所述数据量大于所述第二预设值时,确定所述等级信息为高水位。

43.其中,所述第一预设值、所述第二预设值和所述第三预设值根据实际需求设定,在此不再限制。

44.在其他实施例中,所述水位信息确定准则也可以为其他。

45.作为一种实施方式,所述方法还包括步骤:a1和a2。

46.a1:在每次检测到所述数据队列中被写入数据或者被读取数据之后,确定出当前时刻所述数据队列中所存储数据的数据数量。

47.在实际实施过程中,a1可以按照如下方式实施,在每次检测到所述数据队列中被写入至少一个字节的数据或者被读取至少一个字节的数据之后,获取当前时刻所述数据队列中所存储的数据的数据量。

48.a2:根据所述数据量,更新所述信号。

49.在实际实施过程中,a2可以按照如下方式实施,利用所述数据量,更新与所述数据队列对应的信号中携带的数据量信息。

50.作为一种实施方式,在所述信号中携带的是水位信息时,根据所述数据量,以及所述水位信息确定准则,确定出所述数据量所对应的水位信息。

51.作为一种实施方式,在s11之前,所述方法还包括步骤:b1。

52.b1:在确定所述寄存器中未存储数据时,从所述数据队列中读取所述预设字节的数据到所述寄存器。

53.其中,一个数据队列对应至少一个寄存器,一个寄存器对应一个数据队列,在本实施例中,一个数据队列对应两个寄存器。

54.在实际实施过程中,b1可以按照如下方式实施,针对每个寄存器,实时获取该寄存

器的状态信息,在确定该寄存器的状态信息为空闲状态时,表征该寄存器中未存储数据,此时,从与该寄存器对应的数据队列中按照先进先出的原则并行地读取预设字节的数据到所述寄存器中。

55.其中,所述预设字节为至少一个字节,在本实施例中,所述预设字节为一个字节,在其他实施例中,所述预设字节也可为两个字节、三个字节等,所述预设字节根据寄存器中能够存储的数据量的大小决定,其中,所述预设字节小于等于所述寄存器中能够存储的数据量的大小。

56.s11:在从数据队列读取预设字节的数据到寄存器之后,获取表征所述数据队列中所存储数据的数据量的信号。

57.其中,数据队列的数量可以为一个、两个或多个,只要保证数据队列的数量与e1链路的数量一致即可。在本实施例中,数据队列的数量为63个。

58.其中,所述信号中携带的信息可以是所述数据量,也可以是表征所述数据量大小的水位信息。

59.可以理解的是,随着数据队列中的数据被不断地读取或者被不断写入,表征该数据队列中所存储数据的数据量的信号也会不断地被更新。

60.在实际实施过程中,s11可以按照如下方式实施,在数据队列为至少两个时,针对每个数据队列,在从该数据队列读取预设字节的数据到寄存器之后,查找出与该数据队列对应的表征所述数据队列中所存储数据的数量的信号,以保证后续能够准确地确定出将所述预设字节的数据从该寄存器移出的移出速率。

61.作为一种实施方式,s11可以按照如下方式实施,在数据队列为一个时,在从数据队列读取预设字节的数据到寄存器之后,直接获取表征所述数据队列中所存储数据的数据量的信号,以保证后续能准确地确定出将所述预设字节的数据从该寄存器移出的移出速率。

62.在获取到所述信号之后,执行步骤s12。

63.s12:根据所述信号,确定出对应的时钟频率。

64.作为一种实施方式,s12包括步骤:c1、c2和c3。

65.c1:根据所述信号确定出所述数据量。

66.在实际实施过程中,c1可以按照如下方式实施,在所述信号中携带的信息为数据量时,从所述信号中提取出所述数据量。

67.c2:根据所述数据量和预先确定的数据大小的范围划分准则,确定出与所述数据量对应的数据范围。

68.在实际实施过程中,c2可以按照如下方式实施,通过将所述数据量与按照所述范围划分准则划分的至少两个数据范围进行比较,确定出所述数据量所处的数据范围,即与所述数据量对应的数据范围。

69.其中,所述范围划分准则根据实际需求设定,根据所述范围划分准则划分的数据范围与预先确定的数据范围与时钟频率的对应关系中的数据范围一致。

70.作为一种实施方式,确定所述对应关系的步骤包括:根据预先确定的e1链路的标准时钟的大小,确定出所述对应关系。

71.根据预先确定的数据范围划分准则,确定出至少两个数据范围,并根据所述标准

时钟的大小,以及所述至少两个数据范围,确定出数据范围与时钟频率之间的一一对应关系,其中,数据范围中的均值较大的数据范围所对应的时钟频率,大于均值较小的数据范围所对应的时钟频率;数据范围的数量与时钟频率的数量一致;

72.其中,所述对应关系中的每个时钟频率与所述标准时钟的大小之间的差值小于等于预设值;其中,所述预设值根据实际需求设定,在本实施例中,所述预设值为0.054,在其他实施例中,所述预设值可以为0.001、0.002、0.008等,其中,所述预设值越小,时钟频率越接近所述标准时钟的大小。

73.例如,在所述标准时钟为2.048mhz时,假设所述至少两个数据范围的数量为三个,则时钟频率可以分别为1.99mhz,2.046mhz和2.102mhz;时钟频率也可以分别为2.033mhz,2.048mhz和2.101mhz。

74.作为另一种实施方式,确定所述对应关系的步骤包括:根据所述标准时钟的大小和预先确定的参考时钟的大小,确定所述对应关系。

75.根据预先确定的数据范围划分准则,确定出至少两个数据范围,并根据所述标准时钟的大小和所述参考时钟的大小,以及所述至少两个数据范围,确定出数据范围与时钟频率之间的一一对应关系,其中,数据范围中的均值较大的数据范围所对应的时钟频率,大于均值较小的数据范围所对应的时钟频率;数据范围的数量与时钟频率的数量一致;

76.其中,所述对应关系中的每个时钟频率与所述标准时钟的大小之间的差值小于等于预设值;其中,所述预设值根据实际需求设定,在本实施例中,所述预设值为0.054,在其他实施例中,所述预设值可以为0.001、0.002、0.008等,其中,所述预设值越小,时钟频率越接近所述标准时钟的大小。

77.例如,在所述标准时钟为2.048mhz、所述参考时钟为77.76mhz时,假设所述至少两个数据范围的数量为三个,则可以利用参考时钟的1/39,1/38和1/37来得到时钟速率分别为1.99mhz,2.046mhz和2.102mhz的时钟,继而确定所述对应关系中的时钟频率分别为1.99mhz,2.046mhz和2.102mhz。

78.在确定出所述对应的数据范围之后,执行步骤c3。

79.c3:从预先确定的数据范围与时钟频率的对应关系中,查找出与所述对应的数据范围对应的时钟频率。

80.在实际实施过程中,c3可以按照如下方式实施,根据所述对应的数据范围,从预先确定的数据范围与时钟频率的对应关系中,查找出与所述对应的数据范围对应的时钟频率。

81.在所述信号中携带的信息属于水位信息时,作为一种实施方式,s12包括步骤:d1、d2和d3。

82.d1:根据所述信号确定出水位信息。

83.在实际实施过程中,d1可以按照如下方式实施,从所述信号中提取出所述目标水位信息。

84.d2:从预先确定的水位信息和时钟频率的对应关系中,查找出与所述目标水位信息对应的时钟频率。

85.在实际实施过程中,d2可以按照如下方式实施,根据所述目标水位信息,从预先确定的水位信息和时钟频率的对应关系中,查找出与所述目标水位信息对应的时钟频率。

86.作为一种实施方式,确定水位信息和时钟频率的对应关系的步骤包括:根据预先确定的e1链路的标准时钟的大小,确定出所述对应关系。

87.根据预先确定的e1链路的标准时钟的大小,以及预先确定的水位信息的种类的数量,确定出与所述种类的数量相同的至少两个不同的时钟频率,继而根据水位信息的种类,确定出水位信息与时钟频率之间的一一对应关系,其中,水位高的水位信息所对应的时钟频率,大于水位低的水位信息所对应的时钟频率。

88.其中,水位信息和时钟频率的对应关系中的每个时钟频率与所述标准时钟的大小的差值小于等于预设值,其中,所述预设值根据实际需求设定,在本实施例中,所述预设值为0.054,在其他实施例中,所述预设值可以为其他。

89.例如,在所述标准时钟为2.048mhz时,假设所述水位信息的种类为三个,则时钟频率可以分别为1.99mhz,2.046mhz和2.102mhz;时钟频率也可以分别为2.033,2.048和2.101mhz。

90.作为另一种实施方式,确定水位信息和时钟频率的对应关系的步骤包括:根据所述标准时钟的大小和预先确定的参考时钟的大小,确定所述对应关系。

91.根据所述标准时钟的大小和所述参考时钟的大小,以及预先确定的水位信息的种类,确定出水位信息与时钟频率之间的一一对应关系,其中,水位高的水位信息所对应的时钟频率,大于水位低的水位信息所对应的时钟频率;

92.其中,水位信息与时钟频率的对应关系中的每个时钟频率与所述标准时钟的大小之间的差值小于等于预设值;其中,所述预设值根据实际需求设定,在本实施例中,所述预设值为0.054,在其他实施例中,所述预设值可以为0.001、0.002、0.008等,其中,所述预设值越小,时钟频率越接近所述标准时钟的大小。

93.例如,在所述标准时钟为2.048mhz、所述参考时钟为77.76mhz时,假设水位信息种类的数量为三个,则可以利用参考时钟的1/39,1/38和1/37来得到时钟速率分别为1.99mhz,2.046mhz和2.102mhz的时钟,继而确定水位信息与时钟频率的对应关系中的时钟频率分别为1.99mhz,2.046mhz和2.102mhz。

94.在确定出所述对应的时钟频率之后,执行步骤s13。

95.s13:根据所述对应的时钟频率,将所述寄存器中的数据移出所述寄存器。

96.利用时钟频率为所述对应的时钟频率的时钟,并以bit为单位,将所述寄存器中的数据串行地移出所述寄存器,可以理解的是,一次只将寄存器中的1个bit的数据移出寄存器。

97.请参照图2,图2是本技术实施例提供的一种e1链路的随路时钟抖动抑制装置200的结构框图,所述装置应用于fpga。下面将对图2所示的结构框图进行阐述,所示装置包括:

98.信号获取单元210,用于在从数据队列读取预设字节的数据到寄存器之后,获取表征所述数据队列中所存储数据的数据量的信号;

99.时钟频率确定单元220,用于根据所述信号,确定出对应的时钟频率;

100.移出单元230,用于根据所述对应的时钟频率,将所述寄存器中的数据移出所述寄存器。

101.作为一种实施方式,所述时钟频率确定单元220,具体用于根据所述信号确定出所述数据量;以及根据所述数据量和预先确定的数据大小的范围划分准则,确定出与所述数

据量对应的数据范围;从预先确定的数据范围与时钟频率的对应关系中,查找出与所述对应的数据范围对应的时钟频率。

102.作为一种实施方式,所述装置还包括:对应关系确定单元,用于根据预先确定的e1链路的标准时钟的大小,确定出所述对应关系。

103.作为一种实施方式,所述对应关系确定单元,具体用于根据所述标准时钟的大小和预先确定的参考时钟的大小,确定所述对应关系。

104.作为一种实施方式,所述装置还包括:读取单元,用于在确定所述寄存器中未存储数据时,从所述数据队列中读取所述预设字节的数据到所述寄存器。

105.作为一种实施方式,所述装置还包括:更新单元,用于在每次检测到所述数据队列中被写入数据或者被读取数据之后,确定出当前时刻所述数据队列中所存储数据的数据数量;以及根据所述数据量,更新所述信号。

106.本实施例对的各功能单元实现各自功能的过程,请参见上述图1所示实施例中描述的内容,此处不再赘述。

107.请参照图3,图3为本技术实施例提供的一种电子设备300的结构示意图,电子设备300可以是个人电脑(personal computer,pc)、平板电脑、智能手机、个人数字助理(personal digital assistant,pda)等。

108.电子设备300可以包括:存储器302、处理器301、寄存器303和通信总线,通信总线用于实现这些组件的连接通信。

109.所述存储器302用于存储本技术实施例提供的e1链路的随路时钟抖动抑制方法和装置对应的计算程序指令等各种数据,其中,存储器302可以是,但不限于,随机存取存储器(random access memory,ram),只读存储器(read only memory,rom),可编程只读存储器(programmable read-only memory,prom),可擦除只读存储器(erasable programmable read-only memory,eprom),电可擦除只读存储器(electric erasable programmable read-only memory,eeprom)等。

110.处理器301用于在从数据队列读取预设字节的数据到寄存器之后,获取表征所述数据队列中所存储数据的数据量的信号;根据所述信号,确定出对应的时钟频率;根据所述对应的时钟频率,将所述寄存器中的数据移出所述寄存器。

111.其中,处理器301可能是一种集成电路芯片,具有信号的处理能力。上述的处理器301可以是通用处理器,包括中央处理器(central processing unit,cpu)、网络处理器(network processor,np)等;还可以是数字信号处理器(dsp)、专用集成电路(asic)、现场可编程门阵列(fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。可以实现或者执行本技术实施例中的公开的各方法、步骤及逻辑框图。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。

112.寄存器303,用于存储数据。

113.此外,本技术实施例还提供了一种计算机可读取存储介质,在该存储介质中存储有计算机程序,当所述计算机程序在计算机上运行时,使得所述计算机执行本技术任一项实施方式所提供的方法。

114.综上所述,本技术各实施例提出的e1链路的随路时钟抖动抑制方法、装置及电子设备,在从数据队列读取预设字节的数据到寄存器时,根据表征所述数据队列中所存储数

据的数据量的信号,确定出对应的时钟频率,可以理解的是,时钟频率是和数据队列中所存储数据的数据量呈一定关系的,继而根据所述对应的时钟频率,能稳定地将所述寄存器中的数据移出所述寄存器,从而解决了现有技术中由于sdh携带的e1链路的随路时钟抖动非常大而导致数据的移出速率抖动特别大的问题。

115.在本技术所提供的实施例中,应该理解到,所揭露的装置和方法,也可以通过其它的方式实现。以上所描述的装置实施例仅仅是示意性的,例如,附图中的流程图和框图显示了根据本技术的多个实施例的装置、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段或代码的一部分,所述模块、程序段或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现方式中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个连续的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或动作的专用的基于硬件的装置来实现,或者可以用专用硬件与计算机指令的组合来实现。

116.另外,在本技术各个实施例中的各功能模块可以集成在一起形成一个独立的部分,也可以是各个模块单独存在,也可以两个或两个以上模块集成形成一个独立的部分。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。