技术特征:

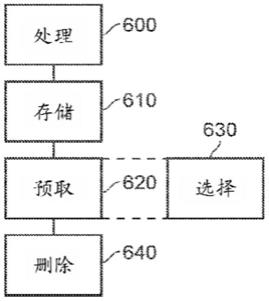

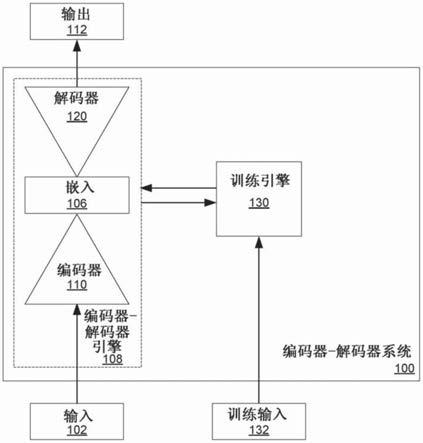

1.一种电路,包括:处理电路,所述处理电路用于处理程序指令,其中所述程序指令由存储电路存储并且所述处理电路包括被配置成执行所述存储电路中的所述程序指令的就地执行处理电路;预取缓冲器,所述预取缓冲器用于存储由所述处理电路执行的程序指令;预取电路,所述预取电路用于控制将程序指令预取到所述预取缓冲器以及选择供预取的下一指令;以及替换电路,所述替换电路用于控制从所述预取缓冲器删除指令以为新预取的程序指令提供存储空间;其中,所述预取电路和所述替换电路中的一者或两者被配置成使得所述预取电路的对供预取的下一程序指令的选择操作和所述替换电路从所述预取缓冲器删除指令的删除操作中的一者或两者取决于先前执行的程序指令和对将要执行的后续程序指令的预测。2.根据权利要求1所述的电路,其中:所述预取电路被配置成从所述处理电路接收程序流程预测信息,所述程序流程预测信息至少指示预测的下一指令地址;以及所述预取电路被配置成选择性地控制从开始于所述预测的下一指令地址的一个或多个地址的集合中预取程序指令。3.根据权利要求2所述的电路,其中,所述程序流程预测信息包括以下信息中的一者或多者:指示转移目标地址的转移预测信息;以及指示一个或多个接下来的连续程序指令的程序计数器信息。4.根据权利要求2所述的电路,其中:所述处理电路包括高速缓存内存;所述预取电路被配置成从所述处理电路接收高速缓存操作信息,所述高速缓存操作信息至少指示所述高速缓存内存的操作的子集;以及所述预取电路被配置成根据所述高速缓存操作信息选择性地控制从一个或多个地址的集合中预取程序指令。5.根据权利要求4所述的电路,其中,所述高速缓存操作信息指示以下项中的至少一者:所述处理电路的未成功高速缓存检索操作;用于驱逐所述高速缓存内存的当前存储内容的高速缓存驱逐操作;所述处理电路的成功高速缓存检索操作;以及高速缓存替换控制状态。6.根据权利要求5所述的电路,其中,所述预取电路被配置成为至少以下程序指令中的每一者生成相应的权重:(i)用于基于所述程序流程预测信息进行预取的第一候选下一程序指令;和(ii)用于基于所述高速缓存操作信息进行预取的第二候选下一程序指令,以及根据所述相应的权重选择性地控制取决于供预取的所述第一候选下一程序指令和所述第二候选下一程序指令中的一者的预取。7.根据权利要求6所述的电路,包括:区域控制器,所述区域控制器用于根据以下信息中的一者或两者来生成当前地址区

域,所述当前地址区域至少具有包含一个或多个下一程序指令的阈值概率:所述高速缓存操作信息;以及所述程序流程信息。8.根据权利要求7所述的电路,其中:所述区域控制器被配置成生成第一概率值,所述第一概率值指示所述当前地址区域响应于给定预取操作而改变的概率;以及所述区域控制器被配置成根据所述第一概率值来改变与供预取的所述第一候选下一程序指令和所述第二候选下一程序指令相关联的相应权重。9.根据权利要求8所述的电路,其中,所述区域控制器被配置成响应于所述程序流程预测信息和所述高速缓存操作信息的当前实例而调节适用于下一预取操作的所述第一概率值。10.根据权利要求7所述的电路,其中:所述区域控制器被配置成生成第二概率值,所述第二概率值指示新预取的程序指令和从高速缓存中驱逐的程序指令中的一者或两者位于所述当前地址区域内的概率;以及所述区域控制器被配置成根据所述第二概率值来改变与供预取的所述第一候选下一程序指令和所述第二候选下一程序指令相关联的相应权重。11.根据权利要求10所述的电路,其中,所述区域控制器被配置成响应于所述程序流程预测信息和所述高速缓存操作信息的当前实例而调节适用于下一预取操作的所述第二概率值。12.根据权利要求4所述的电路,其中:所述高速缓存内存被配置成将程序指令作为程序指令组进行存储和驱逐;以及所述预取电路被配置成预取作为程序指令组的程序指令。13.根据权利要求7所述的电路,其中,所述区域控制器被配置成将所述第一概率值和所述第二概率值中的一者或两者提供给所述高速缓存内存;以及所述高速缓存内存被配置成响应于接收到的所述第一概率值和所述第二概率值中的一者或两者而改变其操作。14.根据权利要求13所述的电路,其中,对于至少为阈值概率的第二概率值,所述高速缓存内存被配置成不在所述当前地址区域中缓存程序指令。15.根据权利要求13所述的电路,其中,所述高速缓存内存被配置成响应于所述第一概率值而改变用于控制存储在所述高速缓存内存中的程序指令的替换的替换算法。16.根据权利要求1所述的电路,其中,所述存储电路是非易失性存储电路。17.一种电路,包括:处理电路,所述处理电路用于处理程序指令,其中所述程序指令由存储电路存储并且所述处理电路包括被配置成执行所述存储电路中的所述程序指令的就地执行处理电路;预取缓冲器,所述预取缓冲器用于存储由所述处理电路执行的程序指令;预取电路,所述预取电路用于控制将程序指令预取到所述预取缓冲器;以及替换电路,所述替换电路用于控制从所述预取缓冲器删除指令以为新预取的程序指令提供存储空间;其中:

所述处理电路包括高速缓存内存;所述预取电路被配置成从所述处理电路接收高速缓存操作信息,所述高速缓存操作信息至少指示所述高速缓存内存的操作的子集;以及所述预取电路和所述替换电路中的一者或两者被配置成使得所述预取电路的对供预取的下一程序指令的选择操作和所述替换电路从所述预取缓冲器删除指令的删除操作中的一者或两者取决于所述高速缓存操作信息。18.一种方法,包括:处理程序指令,其中所述程序指令由存储电路存储并且该处理步骤包括就地执行所述存储电路中的所述程序指令;在预取缓冲器中存储由所述处理步骤执行的程序指令;将程序指令预取到所述预取缓冲器,该预取步骤包括选择供预取的下一指令;以及从所述预取缓冲器中删除指令以为新预取的程序指令提供存储空间;其中,选择步骤和删除步骤中的一者或两者取决于先前执行的程序指令和对将要执行的后续程序指令的预测。19.一种方法,包括:处理程序指令,其中所述程序指令由存储电路存储,并且该处理步骤包括就地执行所述存储电路中的所述程序指令以及将用于执行的程序指令存储在高速缓存内存中;在预取缓冲器中存储由所述处理步骤执行的程序指令;将程序指令预取到所述预取缓冲器,该预取步骤包括选择性地控制从一个或多个地址的集合中预取程序指令;以及从所述预取缓冲器中删除指令以为新预取的程序指令提供存储空间;其中:预取步骤包括接收至少指示所述高速缓存内存的操作的子集的高速缓存操作信息;以及所述预取步骤和删除步骤中的一者或两者取决于所述高速缓存操作信息。

技术总结

一种电路,包括:用于处理由存储电路存储的程序指令的处理电路,并且处理电路包括被配置成执行程序指令的就地执行处理电路;用于存储由处理电路执行的程序指令的预取缓冲器;预取电路,其用于控制将程序指令预取到预取缓冲器以及选择供预取的下一指令;以及替换电路,其用于控制从预取缓冲器删除指令以为新预取的程序指令提供存储空间;其中,预取电路和替换电路中的一者或两者被配置成使得预取电路的对供预取的下一程序指令的选择操作和替换电路从预取缓冲器删除指令的删除操作中的一者或两者取决于先前执行的程序指令和对将要执行的后续程序指令的预测。执行的后续程序指令的预测。执行的后续程序指令的预测。

技术研发人员:李齐民 赖吉昌

受保护的技术使用者:安谋科技(中国)有限公司

技术研发日:2020.09.24

技术公布日:2022/5/6

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。