1.本发明涉及芯片技术领域,具体地涉及一种芯片的低功耗系统、低功耗管理方法、控制装置及存储介质。

背景技术:

2.随着芯片技术的快速发展和一些特殊场景的应用,低功耗技术越来越受到重视。在多种低功耗技术中,功耗控制和寄存器保持(retention)技术是较为常用的低功耗技术。

3.现有技术中,可通过低功耗设计流程,以及统一功耗格式(uniform power format,upf)设计的方式,将芯片系统中不同模块划分为不同的电源域(power domain)。例如,功耗管理单元(power management unit)可以划分在pd_top域中,始终保持供电状态;数字模块可以划分在pd_sw域中,可由功耗管理单元控制,在休眠模式时下电;寄存器和ram模块可以划分在pd_ret域中,可以在进入休眠模式时进入保持状态,退出休眠模式时恢复之前存储的数据。

4.然而,在芯片系统进入休眠模式后,控制寄存器进入保持状态,虽节省了一部分功耗,但处于保持状态的寄存器仍需使用另一路电源供电,仍会消耗一部分功耗。

技术实现要素:

5.本发明实施例的目的是提供一种芯片的低功耗系统,该芯片的低功耗系统可以降低芯片系统功耗。

6.为了实现上述目的,本发明实施例提供一种芯片的低功耗系统,其特征在于,所述芯片的低功耗系统包括:功耗管理单元,被配置在第一电源域,用于根据所接收的休眠控制信号或唤醒控制信号,控制所述芯片进入休眠模式或唤醒模式;寄存器组,被配置在第二电源域,用于存储所述芯片的模拟元件的参数数据;存储单元,被配置在第三电源域,用于在所述芯片进入所述休眠模式后,进入保持状态;传输模块,被配置在所述第二电源域,用于根据所述功耗管理单元控制,在所述芯片进入所述休眠模式前,将所述寄存器组中存储的所述参数数据传输到所述存储单元中保存;在所述芯片进入所述唤醒模式后,将所述存储单元中保存的所述参数数据传输回所述寄存器组。

7.可选的,所述第一电源域保持供电状态。

8.可选的,所述功耗管理单元还用于:在所述将所述寄存器组中存储的所述参数数据传输到所述存储单元中保存之后,控制所述第二电源域掉电;在接收到所述唤醒控制信号之后,控制所述第二电源域上电。

9.可选的,所述功耗管理单元还用于:在所述芯片进入所述休眠模式后,输出休眠标记信号;在所述芯片进入所述唤醒模式后,输出唤醒标记信号。

10.可选的,所述存储单元为随机存取存储器ram、或状态随机存取存储器ddr。

11.可选的,所述传输模块还用于:接收所述功耗管理单元发送的休眠请求信号,以及在所述存储单元进入所述保持状态后,向所述功耗管理单元发送休眠应答信号;接收所述

功耗管理单元发送的唤醒请求信号,以及在所述存储单元进入恢复状态后,向所述功耗管理单元发送唤醒应答信号。

12.可选的,所述传输模块通过其接口模块连接所述寄存器组和所述存储单元,其中,所述接口模块通过模块化设计,适应于不同类型的所述寄存器组和所述存储单元的数据传输模式。

13.本发明实施例还提供一种芯片的低功耗管理方法,所述芯片的低功耗管理方法包括:当接收到休眠控制信号时,将寄存器组中存储的参数数据传输到存储单元中保存;控制所述存储单元进入保持状态,控制所述寄存器组所在的第二电源域掉电;输出休眠标记信号;当接收到唤醒控制信号时,控制所述第二电源域上电,控制所述存储单元进入恢复状态;将所述存储单元中保存的所述参数数据传输回所述寄存器组;输出唤醒标记信号。

14.本发明实施例还提供一种控制装置,所述控制装置包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序,以实现根据上述的芯片的低功耗管理方法。

15.本发明实施例还提供一种机器可读存储介质,该机器可读存储介质上存储有指令,该指令使得机器执行上述的芯片的低功耗管理方法。

16.本发明实施例还提供另一种芯片的低功耗系统,所述芯片的低功耗系统包括:功耗管理单元,被配置在第一电源域,用于根据所接收的休眠控制信号或唤醒控制信号,控制所述芯片进入休眠模式或唤醒模式;寄存器组,被配置在第二电源域,用于存储所述芯片的模拟元件的参数数据;存储单元,被配置在所述第二电源域;传输模块,被配置在所述第二电源域,用于根据所述功耗管理单元控制,在所述芯片进入所述休眠模式前,将所述寄存器组中存储的所述参数数据传输到所述存储单元中保存;在所述芯片进入所述唤醒模式后,将所述存储单元中保存的所述参数数据传输回所述寄存器组。

17.可选的,所述第一电源域保持供电状态。

18.可选的,所述功耗管理单元还用于:在所述将所述寄存器组中存储的所述参数数据传输到所述存储单元中保存之后,控制所述第二电源域掉电;在接收到所述唤醒控制信号之后,控制所述第二电源域上电。

19.可选的,所述功耗管理单元还用于:在所述芯片进入所述休眠模式后,输出休眠标记信号;在所述芯片进入所述唤醒模式后,输出唤醒标记信号。

20.可选的,所述存储单元为闪存flash。

21.可选的,所述传输模块还用于:接收所述功耗管理单元发送的休眠请求信号,以及在所述存储单元进入所述保持状态状态后,向所述功耗管理单元发送休眠应答信号;接收所述功耗管理单元发送的唤醒请求信号,以及在所述存储单元进入恢复状态后,向所述功耗管理单元发送唤醒应答信号。

22.可选的,所述传输模块通过其接口模块连接所述寄存器组和所述存储单元,其中,所述接口模块通过模块化设计,适应于不同类型的所述寄存器组和所述存储单元的数据传输模式。

23.本发明实施例还提供一种芯片的低功耗管理方法,所述芯片的低功耗管理方法包括:当接收到休眠控制信号时,将寄存器组中存储的参数数据传输到存储单元中保存;控制所述存储单元所在的第二电源域掉电;输出休眠标记信号;当接收到唤醒控制信号时,控制

所述第二电源域上电;将所述存储单元中保存的所述参数数据传输回所述寄存器组;输出唤醒标记信号。

24.本发明实施例还提供一种控制装置,所述控制装置包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序,以实现上述的芯片的低功耗管理方法。

25.本发明实施例还提供一种机器可读存储介质,该机器可读存储介质上存储有指令,该指令使得机器执行上述的芯片的低功耗管理方法。

26.通过上述技术方案,在芯片系统进入所述休眠模式前,将所述寄存器组中存储的所述参数数据传输到所述存储单元中保存;在芯片系统进入所述唤醒模式后,将所述存储单元中保存的所述参数数据传输回所述寄存器组,即寄存器组在芯片系统进入休眠模式后,可以完全关断电源,减少休眠模式下寄存器组的功耗,从而进一步降低整个芯片系统的功耗。

27.本发明实施例的其它特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

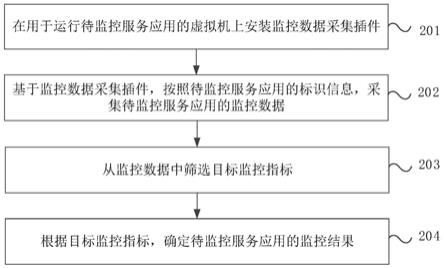

28.附图是用来提供对本发明实施例的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本发明实施例,但并不构成对本发明实施例的限制。在附图中:图1是现有低功耗设计结构示意图;图2是本发明实施例提供的芯片的低功耗系统的结构设计示意图;图3是图2低功耗系统的一示例结构设计示意图;图4是图2低功耗系统的另一示例结构设计示意图;图5是本发明实施例提供的芯片的低功耗管理方法流程示意图;图6是本发明另一实施例提供的芯片的低功耗系统的结构设计示意图;图7是图6低功耗系统的示例结构设计示意图;图8是本发明另一实施例提供的芯片的低功耗管理方法流程示意图。

29.附图标记说明11 第一电源域;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12功耗管理单元;13 第二电源域;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

14传输模块;15寄存器组;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

16第三电源域;17存储单元。

具体实施方式

30.以下结合附图对本发明实施例的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明实施例,并不用于限制本发明实施例。

31.在详细解释本发明实施例之前,先对现有技术及其缺陷进行说明。

32.图1是现有低功耗设计结构示意图,请参考图1,可以根据低功耗设计流程,以及upf设计的方式,将芯片系统中不同模块可以划分为不同的电源域。例如,功耗管理单元可以划分在pd_top域中,始终保持供电状态;数字模块划分在pd_sw域中,可以由功耗管理单

元控制,在休眠模式时下电;寄存器和ram模块划分在pd_ret域中,可以在进入休眠模式时进入保持状态,退出休眠模式时恢复之前存储的数据。

33.现有技术中,将一些关键寄存器划分到pd_ret域中,在芯片系统进入休眠模式后,进入保持状态,虽节省了一部分功耗,但处于保持状态的寄存器仍需使用另一路电源供电,仍会消耗一部分功耗。

34.图2是本发明实施例提供的芯片的低功耗系统的结构设计示意图,请参考图2,该芯片的低功耗系统可以包括:功耗管理单元12,被配置在第一电源域11,用于根据所接收的休眠控制信号或唤醒控制信号,控制所述芯片进入休眠模式或唤醒模式;寄存器组15,被配置在第二电源域13,用于存储所述芯片的模拟元件的参数数据;存储单元17,被配置在第三电源域16,用于在所述芯片进入所述休眠模式后,进入保持状态;传输模块14,被配置在所述第二电源域13,用于根据所述功耗管理单元控制11,在所述芯片进入所述休眠模式前,将所述寄存器组15中存储的所述参数数据传输到所述存储单元17中保存;在所述芯片进入所述唤醒模式后,将所述存储单元17中保存的所述参数数据传输回所述寄存器组15。

35.优选的,所述第一电源域11保持供电状态。

36.优选的,所述功耗管理单元12还用于:在所述将所述寄存器组15中存储的所述参数数据传输到所述存储单元17中保存之后,控制所述第二电源域13掉电;在接收到所述唤醒控制信号之后,控制所述第二电源域13上电。优选的,所述功耗管理单元12还用于:在所述芯片进入所述休眠模式后,输出休眠标记信号;在所述芯片进入所述唤醒模式后,输出唤醒标记信号。

37.图3、图4是图2低功耗系统的示例结构设计示意图,请结合图2、图3和图4,每一个电源域可以简单理解为供电逻辑的划分,在该逻辑划分中既包含了设计的物理实体(module),同时也包含了电源线间的连接关系。在基于upf标准的低功耗设计过程中,必须存在至少一个电源域,并且顶层的电源域或本发明实施例的第一电源域(例如,pd_top域)必须在进行任何与电源相关的分析或者综合之前预先定义出来,同时还需要将电源域定义在层次化模块之上。不同的电源域之间的信号连接需要插入隔离单元(isolation cell)或电压转换单元(level-shifter)等器件。

38.其中,第二电源域(例如,pd_sw域),寄存器组、传输模块以及数字模块划分在其中,可由功耗管理单元控制,在休眠模式时下电;第三电源域(例如pd_ret域),ram(或其他类型存储器)划分在其中,可在进入休眠模式时进入保持状态,进入唤醒模式时恢复之前存储的数据。

39.以示例说明,功耗管理单元12可以划分在第一电源域(例如,pd_top域)11中,通过接收休眠控制信号和唤醒控制信号,控制芯片系统休眠模式的进入和唤醒模式的进入。输入休眠控制信号、唤醒控制信号,对应输出休眠标记信号、唤醒标记信号。并向传输模块14发送休眠请求信号、唤醒请求信号,可以接收传输模块14的应答信号。

40.优选的,所述传输模块14还用于:接收所述功耗管理单元12发送的休眠请求信号,以及在所述存储单元17进入所述保持状态后,向所述功耗管理单元12发送休眠应答信号;接收所述功耗管理单元12发送的唤醒请求信号,以及在所述存储单元17进入恢复状态后,向所述功耗管理单元12发送唤醒应答信号。

41.承接上述示例,传输模块14可以划分在第二电源域(例如,pd_sw域)13中,受功耗

管理单元的控制11,连接寄存器组15与存储单元17。芯片系统进入休眠模式前,功耗管理单元12控制传输模块14,将寄存器组15中存储的参数数据传输到存储单元17中保存;芯片系统进入唤醒模式后,功耗管理单元12控制传输模块14,将存储单元17中保存的参数数据传输回寄存器组15中。

42.寄存器组15划分在第二电源域(例如,pd_sw域)13中,保存芯片系统中一些模拟元件的重要参数数据,例如模拟trim值等。

43.优选的,所述传输模块14通过其接口模块连接所述寄存器组15和所述存储单元17,其中,所述接口模块通过模块化设计,适应于不同类型的所述寄存器组15和所述存储单元17的数据传输模式。

44.传输模块14的接口模块为模块化设计,针对不同的数据存储元件(寄存器组15和存储单元17),只需更改相应的传输接口rtl代码,可适应不同的数据存储元件。

45.优选的,所述存储单元17可以为随机存取存储器ram、或状态随机存取存储器ddr。

46.以示例说明,存储单元17划分在第三电源域(例如,pd_ret域)16中,可以通过两路电源供电,可以在芯片系统进入休眠模式后,进入保持状态,在芯片系统进入唤醒模式后,实现之前保存的数据不丢失。且如果存储单元17(例如,ram)设计的空间足够大,也可以同时用于软件保存现场和恢复现场。存储单元17的设计不只局限于使用ram,也可为其他存取速度较快,并带有掉电保持功能的数据存储元件,例如,状态随机存取存储器ddr等。

47.图5是本发明实施例提供的芯片的低功耗管理方法流程示意图,请参考图5,该芯片的低功耗管理方法可以包括以下步骤:步骤s110:当接收到休眠控制信号时,将寄存器组中存储的参数数据传输到存储单元中保存。

48.以示例说明,功耗管理单元当接收到休眠控制信号时,可以控制传输模块将寄存器组中存储的参数数据传输到存储单元(例如,ram)中保存。

49.步骤s120:控制所述存储单元进入保持状态,控制所述寄存器组所在的第二电源域掉电。

50.在所述将所述寄存器组中存储的所述参数数据传输到所述存储单元(例如,ram)中保存之后,控制所述存储单元(例如,ram)进入保持状态,控制所述第二电源域(例如,pd_sw域)掉电,以降低功耗。

51.步骤s130:输出休眠标记信号。

52.在芯片进入所述休眠模式后,输出休眠标记信号。

53.步骤s140:当接收到唤醒控制信号时,控制所述第二电源域上电,控制所述存储单元进入恢复状态。

54.功耗管理单元当接收到唤醒控制信号时,控制所述第二电源域(例如,pd_sw域)上电,控制所述存储单元(例如,ram)进入恢复状态。

55.步骤s150:将所述存储单元中保存的所述参数数据传输回所述寄存器组。

56.芯片系统进入唤醒模式后,功耗管理单元控制传输模块,将存储单元(例如,ram)中保存的参数数据传输回寄存器组中,实现之前保存的数据不丢失。

57.步骤s160:输出唤醒标记信号。

58.在芯片进入所述唤醒模式后,输出唤醒标记信号。

59.进一步地,本发明实施例还提供了一种控制装置,所述控制装置包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序,以实现根据步骤s110-s160所述的芯片的低功耗管理方法。

60.处理器中包含内核,由内核去存储器中调取相应的程序单元。内核可以设置一个或以上,通过调整内核参数来实现芯片的低功耗管理。

61.存储器可能包括计算机可读介质中的非永久性存储器,随机存取存储器(ram)和/或非易失性内存等形式,如只读存储器(rom)或闪存(flash ram),存储器包括至少一个存储芯片。

62.本发明实施例还提供一种机器可读存储介质,该机器可读存储介质上存储有指令,该指令使得机器执行根据步骤s110-s160所述的芯片的低功耗管理方法。

63.图6是本发明另一实施例提供的芯片的低功耗系统的结构设计示意图,请参考图6,所述芯片的低功耗系统可以包括:功耗管理单元22,被配置在第一电源域21,用于根据所接收的休眠控制信号或唤醒控制信号,控制所述芯片进入休眠模式或唤醒模式;寄存器组25,被配置在第二电源域23,用于存储所述芯片的模拟元件的参数数据;存储单元26,被配置在所述第二电源域23;传输模块24,被配置在所述第二电源域23,用于根据所述功耗管理单元22控制,在所述芯片进入所述休眠模式前,将所述寄存器组25中存储的所述参数数据传输到所述存储单元26中保存;在所述芯片进入所述唤醒模式后,将所述存储单元26中保存的所述参数数据传输回所述寄存器组25。

64.优选的,所述第一电源域21保持供电状态。

65.优选的,所述功耗管理单元22还用于:在所述将所述寄存器组25中存储的所述参数数据传输到所述存储单元26中保存之后,控制所述第二电源域23掉电;在接收到所述唤醒控制信号之后,控制所述第二电源域23上电。

66.优选的,所述功耗管理单元22还用于:在所述芯片进入所述休眠模式后,输出休眠标记信号;在所述芯片进入所述唤醒模式后,输出唤醒标记信号。

67.图7是图6低功耗系统的示例结构设计示意图,请结合图6和图7,以示例说明,功耗管理单元22可以划分在第一电源域(例如,pd_top域)21中,通过接收休眠控制信号和唤醒控制信号,控制芯片系统休眠模式的进入和唤醒模式的进入。输入休眠控制信号、唤醒控制信号,对应输出休眠标记信号、唤醒标记信号。并向传输模块24发送休眠请求信号、唤醒请求信号,可以接收传输模块24的应答信号。

68.优选的,所述传输模块24还用于:接收所述功耗管理单元22发送的休眠请求信号,以及在所述存储单元26进入所述保持状态状态后,向所述功耗管理单元22发送休眠应答信号;接收所述功耗管理单元22发送的唤醒请求信号,以及在所述存储单元26进入恢复状态后,向所述功耗管理单元22发送唤醒应答信号。

69.承接上述示例,传输模块24可以划分在第二电源域(例如,pd_sw域)23中,受功耗管理单元的控制22,连接寄存器组25与存储单元26。芯片系统进入休眠模式前,功耗管理单元22控制传输模块24,将寄存器组25中存储的参数数据传输到存储单元26中保存;芯片系统进入唤醒模式后,功耗管理单元22控制传输模块24,将存储单元26中保存的参数数据传输回寄存器组25中。

70.寄存器组25划分在第二电源域(例如,pd_sw域)23中,保存芯片系统中一些模拟元

件的重要参数数据,例如模拟trim值等。

71.优选的,所述传输模块24通过其接口模块连接所述寄存器组25和所述存储单元26,其中,所述接口模块通过模块化设计,适应于不同类型的所述寄存器组25和所述存储单元26的数据传输模式。

72.传输模块14的接口模块为模块化设计,针对不同的数据存储元件(寄存器组25和存储单元26),只需更改相应的传输接口rtl代码,可适应不同的数据存储元件。

73.优选的,所述存储单元26可以为闪存flash。

74.以示例说明,由于flash掉电数据不丢失的特性,可以将flash划分到第二电源域(例如,pd_sw域)23。存储单元17的设计不只局限于使用flash,也可为其他存取速度较快,并带有掉电数据不丢失特性的数据存储元件。

75.图8是本发明另一实施例提供的芯片的低功耗管理方法流程示意图,请参考图8,该芯片的低功耗管理方法可以包括以下步骤:步骤s210:当接收到休眠控制信号时,将寄存器组中存储的参数数据传输到存储单元中保存.以示例说明,功耗管理单元当接收到休眠控制信号时,可以控制传输模块将寄存器组中存储的参数数据传输到存储单元(例如,flash)中保存。

76.步骤s220:控制所述存储单元所在的第二电源域掉电。

77.在所述将所述寄存器组中存储的所述参数数据传输到所述存储单元(例如,flash)中保存之后,控制所述第二电源域(例如,pd_sw域)掉电,以降低功耗。

78.步骤s230:输出休眠标记信号。

79.在芯片进入所述休眠模式后,输出休眠标记信号。

80.步骤s240:当接收到唤醒控制信号时,控制所述第二电源域上电。

81.功耗管理单元当接收到唤醒控制信号时,控制所述第二电源域(例如,pd_sw域)上电。

82.步骤s250:将所述存储单元中保存的所述参数数据传输回所述寄存器组。

83.芯片系统进入唤醒模式后,功耗管理单元控制传输模块,将存储单元(例如,flash)中保存的参数数据传输回寄存器组中,实现之前保存的数据不丢失。

84.步骤s260:输出唤醒标记信号。

85.在芯片进入所述唤醒模式后,输出唤醒标记信号。

86.进一步地,本发明实施例还提供了一种控制装置,所述控制装置包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序,以实现根据步骤s210-s260所述的芯片的低功耗管理方法。

87.处理器中包含内核,由内核去存储器中调取相应的程序单元。内核可以设置一个或以上,通过调整内核参数来实现芯片的低功耗管理。

88.存储器可能包括计算机可读介质中的非永久性存储器,随机存取存储器(ram)和/或非易失性内存等形式,如只读存储器(rom)或闪存(flash ram),存储器包括至少一个存储芯片。

89.本发明实施例还提供一种机器可读存储介质,该机器可读存储介质上存储有指令,该指令使得机器执行根据步骤s210-s260所述的芯片的低功耗管理方法。

90.综上所述,为进一步减少芯片系统进入休眠模式后,寄存器组的功耗,本发明实施例在芯片系统进入所述休眠模式前,将所述寄存器组中存储的所述参数数据传输到所述存储单元中保存;在芯片系统进入所述唤醒模式后,将所述存储单元中保存的所述参数数据传输回所述寄存器组,即寄存器组在芯片系统进入休眠模式后,可以完全关断电源,减少休眠模式下寄存器组的功耗,从而进一步降低整个芯片系统的功耗。

91.本领域内的技术人员应明白,本技术的实施例可提供为方法、系统、或计算机程序产品。因此,本技术可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本技术可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

92.本技术是参照根据本技术实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

93.这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

94.这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

95.在一个典型的配置中,计算设备包括一个或多个处理器 (cpu)、输入/输出接口、网络接口和内存。

96.存储器可能包括计算机可读介质中的非永久性存储器,随机存取存储器(ram)和/或非易失性内存等形式,如只读存储器(rom)或闪存(flash ram)。存储器是计算机可读介质的示例。

97.计算机可读介质包括永久性和非永久性、可移动和非可移动媒体可以由任何方法或技术来实现信息存储。信息可以是计算机可读指令、数据结构、程序的模块或其他数据。计算机的存储介质的例子包括,但不限于相变内存 (pram)、静态随机存取存储器 (sram)、动态随机存取存储器 (dram)、其他类型的随机存取存储器 (ram)、只读存储器 (rom)、电可擦除可编程只读存储器 (eeprom)、快闪记忆体或其他内存技术、只读光盘只读存储器 (cd-rom)、数字多功能光盘 (dvd) 或其他光学存储、磁盒式磁带,磁带磁磁盘存储或其他磁性存储设备或任何其他非传输介质,可用于存储可以被计算设备访问的信息。按照本文中的界定,计算机可读介质不包括暂存电脑可读媒体 (transitory media),如调制的数据信号和载波。

98.还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的

包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括要素的过程、方法、商品或者设备中还存在另外的相同要素。

99.以上仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。