1.本发明涉及芯片技术领域,尤其涉及一种基于多维仲裁器的数据处理系统和芯片。

背景技术:

2.现有的芯片中,通常存在对多路输入数据进行处理的情况,现有技术通常通过设置一个仲裁器(arbiter),从多路输入数据中选择一路存入接收端fifo(first input first output,先进先出队列)中进行后续处理。当接收端fifo存满时,将会造成多路数据的堵塞。如果接收端设置多个接收端fifo将多路数据分类存储,虽然可以适当缓解发送端多路输入数据的堵塞状况,但是如果采用一个仲裁器,则很有可能造成部分输入通道死锁,如果对于每一个接收端fifo设置一个仲裁器,又会造成芯片面积过大,增加芯片功耗。由此可知,如何在不增加芯片面积的情况下,缓解多路输入通道堵塞,且能避免输入通道死锁,提高数据处理效率成为亟待解决的技术问题。

技术实现要素:

3.本发明目的在于,提供一种基于多维仲裁器的数据处理系统和芯片,能够在不增加芯片面积的情况下,缓解多路输入通道堵塞,且能避免多路输入通道死锁,提高了芯片的数据处理效率。

4.根据本发明第一方面,提供了一种基于多维仲裁器的数据处理系统,包括多维仲裁器和n个输出端fifo,每个输出端fifo用于存储一种数据类型的输入数据,所述多维仲裁器与每一输出端fifo相连接,所述多维仲裁器中配置有多个优先级信息,每一优先级信息对应一种状态组合,所述状态组合为n个输出端fifo的状态组合,输出端fifo的状态包括存满状态和未存满状态,所述多个优先级信息相互独立;其中,所述多维仲裁器用于从m个输入通道获取输入数据,每一输入通道均能够向所述多维仲裁器发送n个数据类型中的至少一种数据类型的输入数据;所述多维仲裁器还用于获取n个输出端fifo的状态,并根据n个输出端fifo的状态组成的状态组合选择对应的优先级信息和目标数据类型,所述目标数据类型包括至少一个数据类型,根据所选择的优先级信息和目标数据类型进行仲裁,选择目标输入数据存入对应类型的输出端fifo,并更新所选择的优先级信息和所存入的输出端fifo的状态信息。

5.根据本发明第二方面,提供了一种芯片,包括所述基于多维仲裁器的数据处理系统。

6.本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明提供的一种基于多维仲裁器的数据处理系统和芯片可达到相当的技术进步性及实用性,并具有产业上的广泛利用价值,其至少具有下列优点:本发明设置了一个仲裁器、多个输出端fifo和多个独立的优先级信息,根据多个输出端fifo的状态组合选择对应的目标数据类型和对应的优先级信息,对多路输入数据进

行处理。本发明能够在不增加芯片面积的情况下,缓解多路输入通道堵塞,且能避免多路输入通道死锁,提高了芯片的数据处理效率。

7.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

附图说明

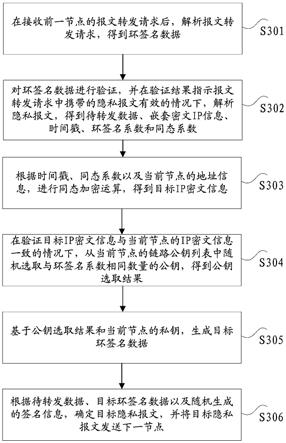

8.图1为本发明实施例提供的基于多维仲裁器的数据处理系统示意图。

具体实施方式

9.为更进一步阐述本发明为达成预定发明目的所采取的技术手段及功效,以下结合附图及较佳实施例,对依据本发明提出的一种基于多维仲裁器的数据处理系统和芯片的具体实施方式及其功效,详细说明如后。

10.本发明实施例提供了一种基于多维仲裁器的数据处理系统,如图1所示,包括多维仲裁器和n个输出端fifo,需要说明的是,本发明实施例中所述多维仲裁器指的是基于多个独立的优先级信息,针对多路输入通道进行仲裁的仲裁器。每个输出端fifo用于存储一种数据类型的输入数据,数据类型可以为data类型或ack(acknowledgement,确认字符)等类型,需要说明的时,根据data的不同,可以将data进一步分为多个数据类型,也可以根据ack的不同将ack分为多个数据类型,n个输出端fifo的深度和宽度具体可以根据所对应的数据类型来具体设置,n个输出端fifo的深度可以相同,也可以不同;n个输出端fifo的宽度,可以相同,也可以不同。

11.所述多维仲裁器与每一输出端fifo相连接,所述多维仲裁器中配置有多个优先级信息,每一优先级信息对应一种状态组合,所述状态组合为n个输出端fifo的状态组合,输出端fifo的状态包括存满状态和未存满状态,所述多个优先级信息相互独立。

12.作为一种实施例,所述状态组合包括2n种,所述多维仲裁器中包括2

n-1个优先级信息,每一优先级信息对应一个状态组合,优先级信息对应的状态组合不包括n个输出端fifo的全部为存满状态的组合。

13.以n=2为例,第一数据端fifo对应第一种数据类型,第二输出端fifo对应第二中数据类型,采用“0”表示输出端fifo为存满状态,“1

”ꢀ

表示输出端fifo为未存满状态,则状态组合如表1所示:第一输出端fifo0011第二输出端fifo0101表1需要说明的是,当状态组合为(0,0)时,说明两个输出端fifo全部为存满状态,此时,多维仲裁器需要暂时停止仲裁工作,因此,输出端fifo全部为0的状态组合不在优先级对应的状态组合中。

14.所述多维仲裁器用于从m个输入通道获取输入数据,每一输入通道均能够向所述多维仲裁器发送n个数据类型中的至少一种数据类型的输入数据。需要说明的是,m个输入通道中可以分别设置一个输入端fifo,每一输入通道中可以支持至少一种数据类型的输入

数据,优选的,所有输入通道可以支持所有数据类型的输入数据。这样,每个输入端fifo中输入的数据的数据类型可能是任意一种数据类型。

15.所述多维仲裁器还用于获取n个输出端fifo的状态,并根据n个输出端fifo的状态组成的状态组合选择对应的优先级信息和目标数据类型,所述目标数据类型包括至少一个数据类型,根据所选择的优先级信息和目标数据类型进行仲裁,选择目标输入数据存入对应类型的输出端fifo,并更新所选择的优先级信息和所存入的输出端fifo的状态信息。

16.需要说明是,将多路数据选择n个输出端fifo之后,具体的数据处理过程根据具体后续逻辑来定,本发明对具体的后续逻辑不做具体限定。

17.作为一种实施例,所述优先级信息包括当前最高优先级输入通道标识,需要说明的是,当前最高优先级输入通道标识即当前首个作为待选择的输入通道的标识。所述多维仲裁器具体用于:步骤s1、根据状态组合选择对应的优先级信息中的当前最高优先级输入通道标识px,将当前为未存满状态的输出端fifo对应的数据类型确定为目标数据类型;步骤s2、判断px对应的输入数据类型是否属于所述目标数据类型,若不属于,则执行步骤s3,否则执行步骤s4;步骤s3、若px位于为输入通道标识序列的末端,则将px更新为预设的输入通道标识序列的首个输入通道标识,否则,将px更新为所述输入通道标识序列中px的下一输入通道标识,返回执行步骤s2;步骤s4、将当前px对应的输入数据存入对应的输出端fifo,若px位于为输入通道标识序列的末端,则将px更新为预设的输入通道标识序列的首个输入通道标识,否则,将px更新为所述输入通道标识序列中px的下一输入通道标识,返回执行步骤s1。

18.所述多维仲裁器通过执行步骤s1-步骤s4,能够选择对应的优先级信息并选择目标数据类型对应的输入数据进行存储,既能保证仲裁的合理性,保证多个输入通道的数据均衡处理,又能避免任何一个输入通道死锁,且只需一个仲裁器即可实现,无需增加芯片面积,降低了芯片功耗,提高了芯片的数据处理效率。

19.作为一种实施例,当所述多维仲裁器获取到的n个输出端fifo的状态全部为存满状态时,说明当前所有的输出端fifo当前均无法存入数据,所述多维仲裁器暂停执行仲裁操作,当获取到的n个输出端fifo的状态并非全部为存满状态时,所述多维仲裁器继续执行仲裁操作。

20.作为一种实施例,如图1所示,所述n个输出端fifo为{f1,f2,

…fn

},fn表示第n个输出端fifo,n的取值范围为1到n,所述多维仲裁器中存储有每一fn的当前存储数据条数和fn的状态,当所述多维仲裁器向fn存入输入数据时或者接收到fn输出数据指令时,更新fn的当前存储数据条数,并根据fn深度的判断fn是否为存满状态,若是,则将fn的状态设置为存满状态该,否则,将fn的状态设置为未存满状态。具体至少可以通过以下两种方式实现:实施方式一、所述多维仲裁器中存储的fn的当前存储数据条数的初始条数为fn的深度,fn的初始状态为未存满状态,当所述多维仲裁器向fn存入输入数据时,将fn的当前存储数据条数减去1,当fn输出数据时,向所述多维仲裁器发送输出数据指令,所述多维仲裁器将当前存储数据条数加上1。可以理解的是,当每次仲裁完成时,会确定一个对应的输出端fifo,向该输

出端fifo存入数据,此时,需要将fn的当前存储数据条数减去1。当后续逻辑需要从fn中获取数据进行相应处理时,fn输出数据,此时,所述多维仲裁器将当前存储数据条数加上1。

21.所述多维仲裁器在执行fn的当前存储数据条数减去1或加上1的操作时,判断减去1或加上1后fn的当前存储数据条数是否等于0,若等于0,则将fn的状态设置为存满状态,否则,设置为未存满状态,所述多维仲裁器实时通过fn的当前存储数据条数的变化准确快速地更新fn的状态。

22.实施方式二、所述多维仲裁器中存储的fn的当前存储数据条数的初始条数为0,fn的初始状态为未存满状态,当所述多维仲裁器向fn存入输入数据时,将fn的当前存储数据条数加上1,当fn输出数据时,向所述多维仲裁器发送输出数据指令,所述多维仲裁器将当前存储数据条数减去1。可以理解的是,当每次仲裁完成时,会确定一个对应的输出端fifo,向该输出端fifo存入数据,此时,需要将fn的当前存储数据条数加上1。当后续逻辑需要从fn中获取数据进行相应处理时,fn输出数据,此时,所述多维仲裁器将当前存储数据条数减去1。

23.所述多维仲裁器在执行fn的当前存储数据条数减去1或加上1的操作时,判断减去1或加上1后fn的当前存储数据条数是否等于fn的深度,若等于fn的深度,则将fn的状态设置为存满状态,否则,设置为未存满状态。所述多维仲裁器实时通过fn的当前存储数据条数的变化准确快速地更新fn的状态。

24.本发明实施例提供了一种芯片,包括本发明实施例所述的基于多维仲裁器的数据处理系统,芯片具体可以为cpu、gpu等任意对多路输入数据有仲裁处理需求的芯片。

25.本发明实施例通过设置一个仲裁器、多个输出端fifo和多个独立的优先级信息,根据多个输出端fifo的状态组合选择对应的目标数据类型和对应的优先级信息,对多路输入数据进行处理。本发明能够在不增加芯片面积的情况下,缓解多路输入通道堵塞,且能避免多路输入通道死锁,提高了芯片的数据处理效率。

26.以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。