1.本发明涉及半导体制造技术领域,具体涉及一种半导体结构及其制造方法。

背景技术:

2.深沟槽电容器件中的沟槽的深度往往达数十微米,故深沟槽电容器件的沟槽通常称为深沟槽。在深沟槽电容器件中,深沟槽的刻蚀是一个关键性乃至决定性的工艺。深沟槽通常形成于半导体衬底如硅衬底中,深沟槽通常是通过对硅衬底进行硅的刻蚀实现的。

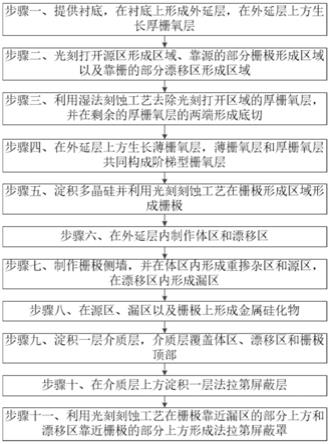

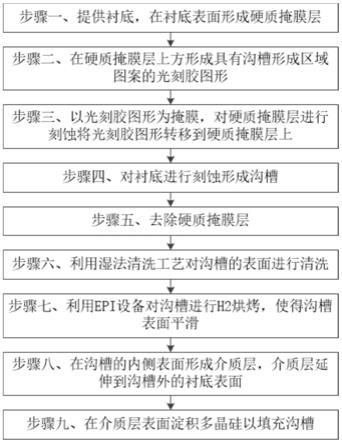

3.图1显示为现有沟槽刻蚀工艺的流程图。如图1所示,现有沟槽刻蚀工艺步骤为:首先,在衬底表面上形成硬质掩膜层(hm),所述硬质掩膜层通常为氧化层和氮化层的叠加层或者纯氧化层;然后进行光刻工艺定义出沟槽的形成区域;光刻工艺包括:涂布光刻胶,进行曝光和显影形成定义有沟槽的形成区域的光刻胶图形;接着以光刻胶为掩膜对所述硬质掩膜层进行刻蚀将光刻胶图形转移到所述硬质掩膜层上;最后,对所述衬底进行刻蚀形成沟槽。

4.图2和图3显示为刻蚀形成沟槽后的半导体结构及其放大的示意图。如图3所示,在衬底中形成沟槽后,半导体结构顶部呈瓶颈状,极易发生漏电。

技术实现要素:

5.有鉴于此,本发明提供一种半导体结构及其制造方法,用以修正沟槽轮廓,降低漏电风险,提升器件性能。

6.本发明提供一种半导体结构的制造方法,包括以下步骤:

7.步骤一、提供衬底,在所述衬底表面形成硬质掩膜层;

8.步骤二、在所述硬质掩膜层上方形成具有沟槽形成区域图案的光刻胶图形;

9.步骤三、以所述光刻胶图形为掩膜,对所述硬质掩膜层进行刻蚀将所述光刻胶图形转移到所述硬质掩膜层上;

10.步骤四、对所述衬底进行刻蚀形成沟槽;

11.步骤五、去除所述硬质掩膜层;

12.步骤六、利用湿法清洗工艺对所述沟槽的表面进行清洗;

13.步骤七、利用epi设备对所述沟槽进行h2烘烤,使得所述沟槽轮廓平滑;

14.步骤八、在所述沟槽的内侧表面形成介质层,所述介质层延伸到所述沟槽外的所述衬底表面;

15.步骤九、在所述介质层表面淀积多晶硅以填充所述沟槽。

16.优选地,步骤一中所述衬底为硅衬底。

17.优选地,步骤一中所述硬质掩膜层为氧化层。

18.优选地,步骤四中在同一所述衬底上形成有多个所述沟槽。

19.优选地,步骤七包括以下步骤:

20.步骤a、在温度为900℃下对所述沟槽进行时间为30秒的烘烤;

21.步骤b、在温度大于950℃下对所述沟槽进行时间为30秒的烘烤;

22.步骤c、在温度为1000℃下对所述沟槽进行时间为30秒的烘烤;

23.步骤d、在温度大于1000℃下对所述沟槽进行时间为60秒的烘烤;

24.步骤e、对所述沟槽进行10秒的刻蚀,再在温度大于1000℃下进行时间为60秒的烘烤。

25.本发明还提供一种半导体结构,包括:

26.衬底;

27.形成于所述衬底中的沟槽;

28.覆盖所述沟槽内侧表面的介质层,所述介质层延伸到所述沟槽外的所述衬底表面;以及

29.形成于所述介质层上方且填充所述沟槽的多晶硅层;其中,所述沟槽经过h2烘烤处理,轮廓变得平滑。

30.本发明在原有沟槽刻蚀工艺基础上,增加了h2烘烤工艺,对刻蚀形成的沟槽的轮廓进行修正,使得器件产生漏电问题的风险降低,提升了器件良率。

附图说明

31.通过以下参照附图对本发明实施例的描述,本发明的上述以及其它目的、特征和优点将更为清楚,在附图中:

32.图1显示为现有沟槽刻蚀工艺的流程图;

33.图2显示为刻蚀形成沟槽后的半导体结构及其放大的示意图;

34.图3显示为刻蚀形成沟槽后的半导体结构的放大示意图;

35.图4显示为本发明实施例的半导体结构的制造方法的流程图;

36.图5显示为本发明实施例的形成硬质掩膜层后的半导体结构示意图;

37.图6显示为本发明实施例的光刻胶图形转移到硬质掩膜层后的半导体结构示意图;

38.图7显示为本发明实施例的形成沟槽后的半导体结构示意图;

39.图8显示为本发明实施例的去除硬质掩膜层后的半导体结构示意图;

40.图9-图14显示为本发明实施例的对沟槽进行h2烘烤后的半导体结构示意图;

41.图15显示为本发明实施例的半导体结构示意图。

具体实施方式

42.以下基于实施例对本发明进行描述,但是本发明并不仅仅限于这些实施例。在下文对本发明的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本发明。为了避免混淆本发明的实质,公知的方法、过程、流程、元件和电路并没有详细叙述。

43.此外,本领域普通技术人员应当理解,在此提供的附图都是为了说明的目的,并且附图不一定是按比例绘制的。

44.除非上下文明确要求,否则整个申请文件中的“包括”、“包含”等类似词语应当解释为包含的含义而不是排他或穷举的含义;也就是说,是“包括但不限于”的含义。

45.在本发明的描述中,需要理解的是,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性。此外,在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

46.图4显示为本发明实施例的半导体结构的制造方法的流程图。

47.如图4所示,包括以下步骤:

48.步骤一、提供衬底,在衬底表面形成硬质掩膜层。

49.如图5所示,图5显示为本发明实施例的形成硬质掩膜层后的半导体结构示意图。本发明实施例中,衬底11为硅衬底。硬质掩膜层12为氧化层,可用炉管生长形成。

50.当然,在其他的实施例中,衬底11也可为其他类型;硬质掩膜层12也可为氧化层和氮化层的叠加层结构。

51.步骤二,在硬质掩膜层上方形成具有沟槽形成区域图案的光刻胶图形。

52.本发明实施例中。利用光刻(曝光和显影)形成具有沟槽形成区域图案光刻胶图形。

53.步骤三,以光刻胶图形为掩膜,对硬质掩膜层进行刻蚀将光刻胶图形转移到硬质掩膜层上。

54.如图6所示,光刻胶图形13转移到了硬质掩膜层12上。

55.步骤四,对衬底进行刻蚀形成沟槽。

56.如图7所示,图7显示为本发明实施例的形成沟槽后的半导体结构示意图。在衬底中形成沟槽14后,半导体结构顶部呈瓶颈状,沟槽14上方表面因刻蚀量较多,刻蚀轮廓弯曲。

57.步骤五,去除硬质掩膜层12。

58.如图8所示,图8显示为本发明实施例的去除硬质掩膜层后的半导体结构示意图。本发明实施例中,利用干法刻蚀将硬质掩膜层12去除。当然,也可用其他适用的方法。

59.步骤六,利用湿法清洗工艺对所述沟槽的表面进行清洗。

60.具体地,刻蚀后,沟槽表面存在刻蚀物,这些颗粒或残留物会影响器件最终的良率,因此进行清洗去除。本发明实施例中,采用湿法清洗工艺清洗所述衬底以去除刻蚀物。

61.步骤七,利用epi设备对沟槽进行h2烘烤,使得沟槽轮廓平滑。

62.如图14所示,显示为本发明实施例的对沟槽进行h2烘烤后的半导体结构示意图。

63.具体地,步骤七包括以下步骤:

64.步骤a、在温度为900℃下对所述沟槽进行时间为30秒的烘烤。如图9所示,显示为对沟槽进行900℃、30秒烘烤后的结构示意图。

65.步骤b、在温度大于950℃下对所述沟槽进行时间为30秒的烘烤。如图10所示,显示为对沟槽进行大于950℃、30秒烘烤后的结构示意图。

66.步骤c、在温度为1000℃下对所述沟槽进行时间为30秒的烘烤。如图11所示,显示为对沟槽进行1000℃、30秒烘烤后的结构示意图。

67.步骤d、在温度大于1000℃下对所述沟槽进行时间为60秒的烘烤。如图12所示,显示为对沟槽进行大于1000℃、60秒烘烤后的结构示意图。

68.步骤e、对所述沟槽进行10秒的刻蚀,再在温度大于1000℃下进行时间为60秒的烘烤。如图13所示,显示为对沟槽先进行10秒刻蚀,再进行大于1000℃、60秒烘烤后的结构示

意图。

69.从图9至图13可看出,经过步骤a至步骤e,沟槽的轮廓逐渐变得平滑,刻蚀沟槽后形成的半导体结构顶部也由瓶颈状变成圆柱状。

70.步骤八,在沟槽的内侧表面形成介质层,介质层延伸到沟槽外的衬底表面。

71.步骤九,在介质层表面淀积多晶硅以填充沟槽。

72.如图15所示,经过步骤八和步骤九,在沟槽14内和衬底11表面形成介质层15和多晶硅层16。

73.本发明实施例通过在现有沟槽刻蚀工艺基础上增加对沟槽进行h2烘烤的步骤,解决了沟槽轮廓弯曲的问题,降低了器件漏电问题产生的风险,提升了器件性能。并且,是在沟槽宽度和深度基本保持不变的情况下,实现的有效的刻蚀轮廓调整。

74.图15显示为本发明实施例的半导体结构的示意图。如图15所示,包括衬底11、形成于衬底11中的沟槽14、以及覆盖沟槽14和衬底11的介质层15和多晶硅层16。

75.本发明实施例中,沟槽14经过h2烘烤处理,轮廓变得平滑。

76.本发明实施例的半导体结构在形成过程中通过增加进行h2烘烤的步骤,使得沟槽刻蚀形貌改变,沟槽轮廓变的平滑,改善了漏电问题,提升了器件性能。

77.应当理解,许多其他层也可以存在,例如间隔元件和/或其他合适的部件,为了简化,图示中予以省略。

78.以上所述仅为本发明的优选实施例,并不用于限制本发明,对于本领域技术人员而言,本发明可以有各种改动和变化。凡在本发明的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。