1.本实用新型涉及继电保护测试仪,特别是涉及一种用于继电保护测试仪的辅助信号输出电路。

背景技术:

2.继电保护测试仪是保证电力系统安全可靠运行的一种重要测试工具。随着计算机技术、微电子技术、电力电子技术的飞速发展,应用最新技术成果不断推出新型高性能继电保护测试仪是技术进步的必然趋势。

3.在利用继电保护测试仪进行测试过程中,常常需要输出辅助信号配合测试,一般而言,但是,增加继电保护测试仪的辅助信号输出通道,往往会增加大量的成本,并且会极大增加继电保护测试仪的体积;但是,如果辅助信号输出路数过少,则可能并不能满足测试所需。

技术实现要素:

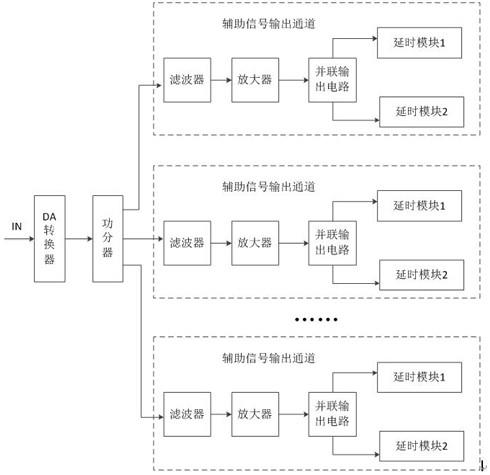

4.本实用新型的目的在于克服现有技术的不足,提供一种用于继电保护测试仪的辅助信号输出电路,在每一个辅助信号输出通道中设置了并联输出电路,使得每个辅助信号输出通道能够输出两路相同的辅助信号,以保证测试所需,有效降低了继电保护测试仪的成本和体积。

5.本实用新型的目的是通过以下技术方案来实现的:一种用于继电保护测试仪的辅助信号输出电路,包括da转换器、功分器和多个辅助信号输出通道;所述da转换器用于将进入辅助信号输入电路的数字信号转换为模拟信号,da转换器的输出端与功分器连接,所述功分器的输出端分别与每一个辅助信号输出通道连接;

6.每一路所述的辅助信号输出通道均包括并联输出电路、第一延时模块和第二延时模块;所述并联输出电路的输入端与所述功分器连接,并联输出电路的第一输出端与第一延时模块连接,并联输出电路的第二输出端与第二延时模块连接,由第一延时模块和第二延时模块对外输出辅助信号。

7.优选地,所述功分器的功率分配路数与辅助信号输出通道的数目相同,且功分器的每一路功率分配输出对应于一个辅助信号输出通道。

8.优选地,每一个所述辅助信号输出通道还包括设置于并联输出电路与功分器之间的滤波器和放大器;所述并联输出短路的输入端依次通过放大器和滤波器与所述功分器连接。

9.本实用新型的有益效果是:本实用新型在每一个辅助信号输出通道中设置了并联输出电路,使得每个辅助信号输出通道能够输出两路相同的辅助信号,以保证测试所需,有效降低了继电保护测试仪的成本和体积。

附图说明

10.图1为本实用新型的原理示意图;

11.图2为并联输出电路的原理示意图。

具体实施方式

12.下面结合附图进一步详细描述本实用新型的技术方案,但本实用新型的保护范围不局限于以下所述。

13.如图1所示,一种用于继电保护测试仪的辅助信号输出电路,包括da转换器、功分器和多个辅助信号输出通道;所述da转换器用于将进入辅助信号输入电路的数字信号转换为模拟信号,da转换器的输出端与功分器连接,所述功分器的输出端分别与每一个辅助信号输出通道连接;

14.每一路所述的辅助信号输出通道均包括并联输出电路、第一延时模块和第二延时模块;所述并联输出电路的输入端与所述功分器连接,并联输出电路的第一输出端与第一延时模块连接,并联输出电路的第二输出端与第二延时模块连接,由第一延时模块和第二延时模块对外输出辅助信号。

15.在本技术的实施例中,所述功分器的功率分配路数与辅助信号输出通道的数目相同,且功分器的每一路功率分配输出对应于一个辅助信号输出通道;每一个所述辅助信号输出通道还包括设置于并联输出电路与功分器之间的滤波器和放大器;所述并联输出短路的输入端依次通过放大器和滤波器与所述功分器连接。

16.如图2所示,在本技术的实施例中,所述并联输出电路包括第一晶体三极管t1、第二晶体三极管t2、第一耗尽型mos 管、第二耗尽型mos管和全差分运算放大器;所述第一晶体三极管t1和第二晶体三极管t2的基极连接在一起作为并联输出电路的输入端;所述第一晶体三极管t1的发射极连接第一耗尽型mos 管的漏级,第二晶体三极管t2的发射极连接第二耗尽型mos管的漏级;第一晶体三极管t1的发射极还与全差分运算放大器的正相输入端连接,第一耗尽型mos 管的栅极与全差分运算放大器的正相输出端连接;第二晶体三极管t2的发射极还与全差分运算放大器的反相输入端连接,第二耗尽型mos 管的栅极还与全差分运算放大器的反相输出端连接;所述第一晶体三极管t1的集电极作为并联输出电路的第一输出端;所述第二晶体三极管t2的集电极作为并联输出电路的第二输出端。

17.工作时,输入信号使两个晶体三极管开启,产生集电极电流,集电极电流在耗尽型mos管的漏端产生压降,理想状态下,电流相等时,两个晶体三极管的基极到发射极电压降应该相等,全差分运算放大器的两个输入端电压相等。当电流不相等时,全差分运算放大器的输入端电压有差别,例如当第一晶体三极管t1的基极电流不足时,将会使得第一晶体三极管t1的vbe压降较小,全差分运算放大器正相输入端电压较高,则正相输出端电压增大,使第一耗尽型mos 管mh1 栅极电压增大,mh1 导通压降降低,电流增大,从而补偿第一晶体三极管t1的输出电流,mh1 导通压降,即mh1 的vds 下降,拉低全差分运算放大器正相输入端电压,直到全差分运算放大器的两个输入端电压相等,使得稳定状态下,不仅两个晶体三极管的vbe 相等,同时两个耗尽型mos 管的vds 也相等,都促使流过每一晶体三级管的电流相等,也有助于使输出信号更加均匀。采用耗尽管是因为其在栅极电压为零时仍然可以导通,避免了采用增强型mos 在开机时可能出现的全差分运算放大器某一输出端电压很低

或为零导致不能开启的状态;

18.在本技术的实施例中,所述第一耗尽型mos 管与第二耗尽型mos管的宽长比相等;所述第一耗尽型mos 管与第二耗尽型mos管的版图布局为对称设置,且第一耗尽型mos 管到第一晶体三级管t1的走线长度等于第二耗尽型mos 管到第二晶体三级管t2的走线长度,第一耗尽型mos 管到第一晶体三级管t1的走线宽度等于第二耗尽型mos 管到第二晶体三级管t2的走线宽度;所述第一耗尽型mos 管的源级与衬底连接在一起,且第一耗尽型mos 管的源级接地;所述第二耗尽型mos管的源级与衬底连接在一起,且第二耗尽型mos管的源级接地。所述第一耗尽型mos 管的栅极和漏级之间连接有补偿电容c1,所述第二耗尽型mos管的栅极和漏级之间连接有补偿电容c2;由于全差分运算放大器输出端和输入端分别是mos 管的栅极和漏极,在全差分运算放大器的反馈环路中,根据密勒效应,栅漏之间的电容在小信号分析中被等效放大,从而产生一个主极点,反馈环路的稳定性增加;当在栅漏之间增加额外的补偿电容时,密勒效应同样使得该电容被放大,更容易获得优良的频率稳定性。

19.在本技术的实施例中,所述延时模块为可调延时器,在每个信号输出之前,可以根据需要进行延时调节,以便于继电保护测试仪输出所需时延的辅助信号,为继电保护测试仪的测试工作提供便利。

20.以上实施例仅用以说明本实用新型的技术方案,而非对其限制;尽管参照前述实施例对本实用新型进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。