功率高效同步整流器栅极驱动器架构

1.相关申请

2.本技术是2019年12月19日提交的美国非临时专利申请号16/721,377的国际申请,该美国非临时申请要求于2019年9月20日提交的美国临时专利申请号62/903,548的权益,这两个专利申请都通过引用整体并入本文。

背景技术:

3.各种电子装置(例如,诸如智能电话、平板计算机、笔记本计算机、膝上型计算机、集线器、充电器、适配器等)被配置为根据在通用串行总线(usb)供电(usb-pd)规范的各种修订版中定义的usb供电协议通过usb连接器传输电力。例如,在一些应用中,电子装置可以被配置为耗电方以通过usb连接器接收电力(例如,用于电池充电),而在其他应用中,电子装置可以被配置为供电方以向通过usb连接器连接到其的另一装置提供电力。然而,usb-pd规范允许供电方和耗电方动态地协商所提供的电压和电流的电平。在某些供电条件下,可以在从供电方提供的电压/电流上发生故障状况,以及可以在由耗电方接收的所提供的电压/电流上发生其他故障状况。

附图说明

4.在附图的各图中,通过示例而非限制的方式示出本公开。

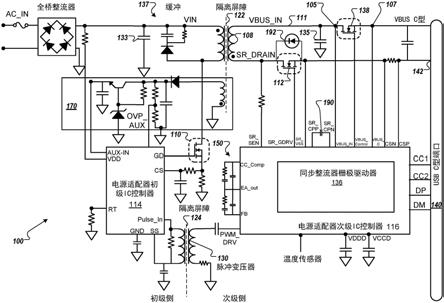

5.图1是在一个实施例中的usb-pd电源适配器的示意图,该usb-pd电源适配器具有集成于次级侧控制器(也称为电源适配器次级ic控制器)上的具有自适应转换速率控制的同步整流器栅极驱动器(srgd)。

6.图2是根据一个实施例的同步开关方案的时序图,其示出了反激转换器的次级侧上的开关电流和电压波形。

7.图3是根据一个实施例的集成于次级受控反激转换器中的次级侧控制器上的srgd的相位和转换控制器电路的示意图。

8.图4是根据一个实施例的对应于由相位和转换控制器产生的控制信号以实现集成于次级受控反激转换器中的次级侧控制器上的srgd的操作相位的时序和电压图。

9.图5是根据一个实施例的集成于次级受控反激转换器中的次级侧控制器上的srgd的框图。

10.图6是根据一个实施例的耦接到集成于次级受控反激转换器中的次级侧控制器上的srgd的相位和转换速率控制器电路的升压电压发生器电路和栅极驱动器电路的实施方式的框图。

11.图7是示出了根据一个实施例的集成于usb-pd电源适配器的次级侧控制器上的srgd操作期间栅极电容器和同步整流器fet栅极上的电压的时序图。

12.图8是根据一个实施例的集成于次级受控反激转换器中的次级侧控制器上的具有基于延迟的相位发生器的srgd的框图。

13.图9是示出了根据一个实施例的集成于usb-pd电源适配器的次级侧控制器上的具

有基于延迟的相位发生器的srgd操作期间栅极电容器和同步整流器fet栅极上的电压的时序图。

14.图10是根据一个实施例的耦接到集成于次级受控反激转换器中的次级侧控制器上的srgd的相位和转换速率控制器电路的升压电压发生器电路和具有一条上拉路径的栅极驱动器电路的实施方式的框图。

15.图11是根据一个实施例的耦接到集成于次级受控反激转换器中的次级侧控制器上的具有二极管的srgd的相位和转换速率控制器电路的升压电压发生器电路和栅极驱动器电路的实施方式的框图。

16.图12a是根据一个实施例的p型金属氧化物半导体(pmos)驱动强度跟踪电流发生器的示意图。

17.图12b是根据一个实施例的n型金属氧化物半导体(nmos)驱动强度跟踪电流发生器的示意图。

18.图13a是根据一个实施例的用于pmos器件的基于延迟的转换发生器的示意图。

19.图13b是根据一个实施例的用于nmos器件的基于延迟的转换发生器的示意图。

20.图14是根据一个实施例的srgd的具有自适应偏置控制器的上拉路径的示意图。

21.图15a是示出了根据一个实施例的用于自适应转换控制块中的同步整流器fet角两端的pmos延迟单元的延迟变化的曲线图。

22.图15b是示出了根据一个实施例的用于自适应转换控制块中的同步整流器fet角两端的nmos延迟单元的延迟变化的曲线图。

23.图16是根据一个实施例的usb-pd电源适配器的示意图,该电源适配器具有集成于次级侧控制器(也称为电源适配器次级ic控制器)上的同步整流器栅极驱动器(srgd),以从供电方装置向附接的耗电方装置输送电力。

24.图17是示出了根据一些实施例的用于usb供电中使用的usb装置的系统的框图。

25.图18是根据一个实施例的方法的流程图,该方法通过具有自适应转换控制的srgd来同步地切换同步整流器fet,以便绝热地对栅极电容器进行充电和放电,以循环利用电荷,并且在同步整流器fet的栅极上产生升压电压。

具体实施方式

26.以下描述阐述了许多具体细节,例如具体系统、部件、方法等的示例,以便提供对本文描述的技术的各种实施例的良好理解,所述技术使用具有自适应转换速率控制的同步开关方案对次级受控反激转换器(例如,用于usb供电应用中)中的栅极电容器(例如,0.1uf栅极电容器)进行充电和放电,以减少功耗。然而,对于本领域技术人员来说,显然,可以在没有这些具体细节的情况下实践至少一些实施例。在其他实例中,没有详细描述或以简单的框图格式呈现公知的部件、元件或方法,以避免不必要地使本文描述的技术难以理解。因此,下文阐述的具体细节仅是示例性的。特定的实施方式可以不同于这些示例性细节,并且仍然被认为在本发明的精神和范围内。

27.在说明书中对“实施例”、“一个实施例”、“示例实施例”、“一些实施例”和“各种实施例”的引用意味着结合(一个或多个)实施例描述的特定特征、结构、步骤、操作或特性被包括在本发明的至少一个实施例中。此外,在说明书中的各个地方出现的短语“实施例”、“一个实施例”、“示例实施例”、“一些实施例”和“各种实施例”不一定都指相同的(一个或多个)实施例。

28.说明书包括对附图的参考,附图形成具体实施方式的一部分。附图示出了根据示例性实施例的图示。这些实施例(其在本文中也可以被称为“示例”)被足够详细地描述以使得本领域技术人员能够实践本文描述的所要求保护的主题的实施例。可以组合实施例,可以利用其他实施例,或可以在不脱离所要求保护的主题的范围和精神的情况下作出结构、逻辑和电改变。应当理解,本文所述的实施例并非旨在限制本主题的范围,而是使本领域技术人员能够实践、制成和/或使用本主题。

29.本文描述的是用于绝热地对耦接到usb供电(usb-pd)中的电子装置中的电力线的次级受控反激转换器中的栅极电容器进行充电和放电的技术的各种实施例。这样的电子装置的示例包括但不限于个人计算机(例如,膝上型计算机、笔记本计算机等)、移动计算装置(例如,平板、平板计算机、电子阅读器装置等)、移动通信装置(例如,智能电话、蜂窝电话、个人数字助理、消息收发装置、掌上pc等)、连接和充电装置(例如,集线器、扩展坞、适配器、充电器等)、音频/视频/数据记录和/或回放装置(例如,相机、录音机、手持式扫描仪、监视器等)、以及可以使用usb连接器(接口)进行通信、电池充电和/或供电的其他类似电子装置。本文描述的实施例可以用于ac到dc电源适配器、以600khz频率操作的基于gan的电源适配器、具有初级或次级侧控制器的电源适配器、以各种操作模式操作的电源适配器,操作模式例如是准谐振模式(qr)、不连续导电模式(dcm)、连续导电模式(ccm)等。本文描述的实施例可以与c型pd能力一起用于电源适配器解决方案中。

30.支持usb的电子装置或系统可以符合usb规范的至少一个发行版。这样的usb规范的示例包括但不限于usb规范修订版2.0、usb 3.0规范、usb 3.1规范和/或其各种补充(例如,诸如on-the-go或otg)、版本和勘误表。usb规范一般地定义设计和构建标准通信系统和外围装置所需的差分串行总线的特性(例如,属性、协议定义、事务类型、总线管理、编程接口等)。例如,支持usb的外围装置通过主机装置的usb端口附接到支持usb的主机装置以形成支持usb的系统。usb 2.0端口包括5v的电源电压线(表示为vbus)、差分数据线对(表示为d 或dp,以及d-或dn),以及用于电力返回的地线(表示为gnd)。usb 3.0端口也提供vbus、d 、d-和gnd线,以用于与usb 2.0的向后兼容。另外,为了支持更快的差分总线(usb超高速总线),usb 3.0端口还提供差分发送器数据线对(表示为sstx 和sstx-)、差分接收器数据线对(表示为ssrx 和ssrx-)、用于电源的电源线(表示为dpwr)、以及用于电力返回的地线(表示为dgnd)。usb 3.1端口提供与usb 3.0端口相同的线,以用于与usb 2.0和usb 3.0通信的向后兼容,但是通过被称为增强超高速的特征的集合扩展超高速总线的性能。

31.在usb c型(type-c)规范的各种发行版和/或版本(例如,诸如2014年8月11日的发行版1.0、2015年4月3日的发行版1.1等)中定义了一种用于usb连接器的更新技术,其被称为usb c型。usb c型规范定义了c型插座、c型插头和c型电缆,它们可以支持usb通信以及通过在usb-pd规范的各种修订版/版本中定义的较新的usb供电协议的供电。usb c型功能和要求的示例可以包括但不限于根据usb 2.0和usb 3.0/3.1的数据和其他通信、c型电缆的机电定义和性能要求、c型插座的机电定义和性能要求、c型插头的机电定义和性能要求、c型到传统电缆组件和适配器的要求、基于c型的装置检测和接口配置的要求、c型连接器的优化供电的要求等。根据(一种或多种)usb c型规范,c型端口提供vbus、d 、d-、gnd、sstx 、

sstx-、ssrx 和ssrx-线等。另外,c型端口还提供用于边带功能的信令的边带使用(表示为sbu)线和用于发现、配置和管理跨c型电缆的连接的配置信道(表示为cc)线。c型端口可以与c型插头和/或c型插座相关联。为了易于使用,c型插头和c型插座被设计为可逆对,其操作与插头到插座的取向无关。因此,作为标准c型插头或插座设置的标准usb c型连接器提供了用于四条vbus线、四条地返回(gnd)线、两条d 线(dp1和dp2)、两条d-线(dn1和dn2)、两条sstx 线(sstxp1和sstxp2)、两条sstx-线(sstxn1和sstxn2)、两条ssrx 线(ssrxp1和ssrxp2)、两条ssrx-线(ssrxn1和ssrxn2)、两条cc线(cc1和cc2)以及两条sbu线(sbu1和sbu2)等的引脚。

32.一些支持usb的电子装置可以符合usb-pd规范的特定修订版和/或版本(例如,诸如2012年7月5日发布的修订版1.0、2014年8月11日发布的修订版2.0等、或其后的修订版/版本)。usb-pd规范定义了一种标准协议,该标准协议被设计为通过提供更灵活的供电以及经由usb c型端口通过单个usb c型电缆的数据通信来实现支持usb的装置的最大功能。usb-pd规范还描述了用于管理在高达100w功率下通过usb c型电缆的供电所必需的架构、协议、电源行为、参数和电缆布线。根据usb-pd规范,具有usb c型端口的装置(例如,诸如支持usb的装置)可以协商通过usb c型电缆的与较老的usb规范(例如,诸如usb 2.0规范、usb 3.1规范、usb电池充电规范1.1/1.2版等)中所允许的相比更大的电流和/或更高或更低的电压。例如,usb-pd规范定义了对可以在一对支持usb的装置之间协商的供电合约(pd合约)的要求。pd合约可以指定可以由两个装置适应的功率电平和电力传输的方向,并且可以在任一装置请求时和/或响应于各种事件和条件(例如,电力角色交换、数据角色交换、硬复位、电源故障等)而动态地重新协商(例如,无需装置拔出插头)。

33.根据usb-pd规范,电子装置通常被配置为通过usb vbus线上配置的电力路径向另一装置供电。提供电力的装置通常被称为(或包括)“提供方”(或电源),并且消耗电力的装置通常被称为(或包括)“消耗方”(或电力接收方(power sink))。电力路径通常包括串联耦接在vbus线上并且被配置为导通和关断电力输送的电力开关。

34.usb-pd电源可以被配置为从交流(ac)电源适配器或从另一ac电源汲取电力。因此,作为交流到直流(ac-dc)转换的一部分,一些实施方式可以在vbus线的电源侧使用大容量电容器(large bulk capacitor),以便去除功率信号的ac分量。电力开关(也称为功率fet)的导通和关断可以允许基于电流和电压状况的分析以及故障的检测的进一步电路保护。

35.在一种反激转换器中,确定效率是的一个因素是次级侧fet(例如,mosfet开关),其并联耦接到反激转换器的次级侧上的二极管。次级侧fet的导通电阻(rdson)连同次级侧控制器上的驱动次级侧fet的栅极的栅极驱动器的上升和下降时间,确定反激转换器的效率。在一个实施例中,栅极驱动器的电源可以低到3v,然后,栅极驱动器可能需要至少5v以实现次级侧fet的更低导通电阻。这需要为驱动器使用升压电源。栅极驱动器在次级侧fet的栅极处产生升压电压。然后,为了这样做,使用了用于栅极驱动器的电荷泵电源。使用电荷泵产生升压电压供应需要从电池获得比栅极驱动器的供应高的供应。利用电荷泵不可能进行电荷循环利用,从而导致在反激转换器的操作期间电力损失增大。另外,反激转换器没有自适应转换控制,这导致在快速工艺-电压-温度(pvt)角处有更高的峰值电流(例如,对于具有快速上升和下降时间的栅极驱动器)。反激转换器的问题是增大的功耗、在金属路由

线中导致可靠性问题的高峰值电流以及影响关键模拟块的性能的增大的电源/地噪声。

36.本文描述的是通过如下方式相对于传统反激转换器提高效率并且降低栅极驱动器功耗的技术的各种实施例:使用具有自适应转换速率控制的同步开关方案对栅极电容器进行绝热充电和放电,并且循环利用电荷,并且在同步整流器fet(例如,次级侧fet、次级侧供电方fet等)的栅极处产生升压电压。并非使用电荷泵向同步整流器fet的栅极直接供应升压电压,本文描述的同步开关方案允许将同步整流器fet的栅极充电到次级侧控制器的电源电压电平,并且允许以适当定时(例如,在各个阶段中)对栅极电容器充电和放电,以便向电源电压增加电压。这提供了间接在同步整流器fet的栅极上产生升压电压(例如,电源电压的两倍)的手段。在要关闭同步整流器时,过剩的电荷(例如,为了产生升压电压)被循环回到栅极电容器,以便对栅极电容器重新充电。在同步整流器fet要导通并且需要升压电压供应时,来自栅极电容器的电荷可以再次用于提升同步整流器fet的栅极上的电压供应。在一个实施例中,栅极电容器是极化电容器,例如,电解质电容器、钽电容器等。在另一实施例中,栅极电容器可以是非极化电容器,例如,陶瓷电容器、膜电容器等。在一个实施例中,栅极电容器是自举电容器。该同步开关方案被设计成使功耗最小化,循环利用栅极电荷,并且减小栅极驱动器的峰值电流(例如,从3.381a到1.33a)和噪声而不会影响瞬态性能。本文描述的具有自适应转换速率控制的同步开关方案的实施例通过绝热地对栅极电容器进行充电和放电以循环利用电荷并且减小功耗,可以解决上述和其他挑战,而不需要上文描述的额外逻辑单元和电路以及复杂的协议。在一些实施例中,可以在栅极电容器的放电阶段期间循环利用电荷。在一些实施例中,本文描述的具有自适应转换速率控制的同步开关方案可以用于次级受控反激转换器中。在一些实施例中,该同步开关方案可以将栅极驱动器的功耗降低30%,将峰值电流和电源噪声减小2.5倍,并且通过使用5v mosfet取代10v mosfet,相较于常规方案减小面积。自适应转换速率控制可以跟踪栅极驱动器的pvt变化,并且然后动态调整栅极驱动器的驱动强度,以符合性能需求(例如,在慢角组合处)并且降低峰值电流和噪声(在快角组合中)。

37.本文描述的实施例可以通过如下方式解决上述和其他挑战:在具有自适应转换速率控制的同步开关方案中提供兼容串行总线的电源装置,例如具有功率控制模拟子系统(其具有硬件、固件或任何组合以传送信息)的串行总线供电(sbpd)装置,以绝热地对栅极电容器进行充电和放电,并且在次级侧fet(本文中也称为“同步整流器fet”)的栅极处产生升压电压,并且跨越电隔离屏障驱动初级侧fet。在一个实施例中,电隔离屏障可以由脉冲变压器提供。在其他实施例中,电隔离可以由光电耦合器、电容性隔离器等提供。sbpd装置(本文也称为“源装置”)可以是兼容usb的电源装置。本文描述的实施例也可以在其他类型的电源适配器、电力转换器、供电电路等中实施。

38.图1是在一个实施例中的usb-pd电源适配器100的示意图,该usb-pd电源适配器具有集成于次级侧控制器116(也称为电源适配器次级ic控制器)上的具有自适应转换速率控制的同步整流器栅极驱动器(srgd)136。在一个实施例中,usb-pd电源适配器100可以经由脉冲变压器130跨越隔离屏障传送信息。在另一实施例中,usb-pd电源适配器100可以跨越光电隔离器(图1未示出)传送信息。usb-pd电源适配器100包括初级ic控制器114和次级ic控制器116。次级ic控制器116可以设置于芯片封装中并且包括根据本文描述的用于栅极驱动器控制的技术来配置的usb-pd子系统。次级ic控制器116被配置为与附接到usb c型端口

140的耗电方装置(未示出)协商pd合约,并且通过输出引脚(“pwm_drv”)控制从反激变压器108输出的所需vbus电压。usb c型端口140典型地与c型插头相关联,但应当理解,在各实施例中,usb c型端口可以替代地与c型插座相关联。

39.次级ic控制器116包括srgd 136。srgd具有升压电压发生器电路、栅极驱动器电路以及相位和转换控制器电路。升压电压发生器电路在栅极电容器190的极板sr_cpp上产生升压电源电压(2*vddd)。升压电压是大于次级ic控制器116的电源电压的电压。升压电压发生器块使用自举原理驱动栅极电容器,以在同步整流器fet 112的栅极上产生升压电压。栅极驱动器电路驱动反激转换器的同步整流器fet。相位和转换控制器是srgd的控制块,其产生控制信号,用于驱动器的不同操作相位和所需转换。反激变压器108耦接到整流dc电源,并且输出可以耦接到同步整流器fet 112(例如,sr_fet 412)。vbus_in由误差放大器调节,误差放大器连接到补偿网络150。补偿网络150可以是usb-pd电源适配器100的设计特有的电阻器-电容器(rc)电路。补偿网络150可以被耦接以从次级ic控制器116的第一输出引脚(“fb”)接收反馈信号。补偿网络150还可以耦接到第二输出引脚(“ea_out”)和第三输出引脚(“cc_comp”)。反激变压器108可以耦接到大容量电容器133和缓冲电路137。usb-pd电源适配器100还可以包括用于跨越隔离屏障124传送信息的脉冲变压器130(或其他反馈控制机构)。

40.集成于次级ic控制器116上的srgd 136耦接到vbus线111并且被配置为控制电力开关(例如,供电方fet 138,本文也称为次级电力开关)的操作和状态。srgd 136提供了具有自适应转换控制的同步开关方案,以便对栅极电容器190进行充电和放电,以循环利用电荷,并且在同步整流器fet 112的栅极上产生升压电压。在一些实施例中,栅极电容器190可以被绝热地充电和放电。vbus线111包括供电方fet 138,其被配置为由来自次级ic控制器116中的输出引脚的信号(“vbus_control”)控制的导通/关断开关装置。供电方fet 138可以对应于本文描述的供电方fet。在一个实施例中,供电方fet 138可以是nfet。在另一实施例中,供电方fet 138可以是peft。在供电方开关138的一侧,vbus线111上的电源节点105耦接到反激变压器108的第二绕组,反激变压器108耦接到大容量电容器135,大容量电容器135被配置为消除功率信号的ac分量。电源节点105耦接到次级ic控制器116的输入引脚(“vbus_in”)。在供电方fet 138的另一侧,vbus线111上的输出节点107耦接到usb c型端口140。输出节点107耦接到次级ic控制器116的另一个输入引脚(“vbus_c”)。usb c型端口140的gnd端子142耦接到同步整流器fet 112。

41.在操作中,vbus线111上电力流的方向是从反激变压器108到附接到usb c型端口140的耗电方装置,例如膝上型计算机(未示出)。在与耗电方装置协商pd合约时,次级ic控制器116导通供电方fet 138,以在协商的(一个或多个)电压和/或电流电平下向耗电方装置提供电力。在pd合约被动态重新协商为降低vbus电压和/或电流时,例如,在耗电方装置已经完成对其电池充电并且现在仅需要电力来操作时,可能需要vbus线111上的高到低电压转变。

42.可以发送控制信号以限制供电方fet 138的栅极-源极电压,并且关断电力开关138,由此将usb c型端口140从反激变压器108断开。通过将vbus_control的输出驱动到零,关断供电方fet 138。通过限制电力开关138的栅极源极电压,保护fet不被损坏。这种断开可能由过电压条件、过电流条件或其他条件(该其他条件可能需要从反激变压器108断开

usb c型端口140以用于保护耦接到usb c型端口140的电路)导致。

43.在另一实施例中,辅助电路170可以耦接到初级ic控制器114。辅助输出引脚(“aux_in”)和过电压保护辅助引脚(“ovp_aux”)耦接到辅助电路170。辅助电路170可以操作以针对vbus_in111的过电压进行保护,并且一旦完成启动,还向初级ic 114提供电力(aux_in)。

44.如上所述,usb-pd电源适配器100允许具有自适应转换速率控制的同步开关方案,以对栅极电容器190进行充电和放电(例如,改变其上的电荷),并且经由srgd 136在次级侧fet(本文也称为“同步整流器fet”)的栅极处产生升压电压。次级ic控制器116的pwm驱动器电路可以在输出引脚(“pwm_drv”)上输出信号,以经由脉冲变压器130跨越隔离屏障124传送信息。如本文所述,pwm驱动器电路可以是在输出引脚上生成脉冲以跨越隔离屏障124传送信息的其他驱动器电路。初级ic控制器114可以包括检测电路,检测电路在输入引脚(“pulse_in”)上接收信号并且检测次级ic控制器116何时传送信息。在另一实施例中,初级ic控制器114可以经由反激变压器108跨越隔离屏障122传送信息。初级ic控制器114可以包括用于经由脉冲变压器130改变从次级ic控制器116接收的脉冲的电路。通过改变脉冲,初级ic控制器114可以经由初级电力开关110跨越反激变压器108发送信息。次级ic控制器116可以包括测量次级电力开关112(例如,同步整流器fet)的漏极(sr_drain)的电路。

45.在另一实施例中,ac-dc电源适配器装置包括耦接于ac端子与dc端子之间的反激转换器(具有反激变压器)或隔离的电力转换器。反激变压器将ac端子上的ac电力转换成dc端子上的dc电力,其中在ac端子与dc端子之间具有电隔离。ac-dc电源适配器装置还包括耦接到反激变压器的初级侧控制器和耦接到反激变压器的次级侧控制器。初级侧电力开关(也称为初级侧开关fet或初级fet)耦接到反激变压器的初级绕组和初级侧控制器。次级侧fet(也称为同步整流器fet)耦接到反激变压器的次级绕组和次级侧控制器。初级侧控制器被配置为跨越电隔离屏障从次级侧控制器接收第一信号,并且响应于第一信号向初级侧电力开关施加第二信号,以导通和关断初级侧电力开关。次级侧控制器的srgd还被配置为产生具有自适应转换速率控制的同步开关方案,以对栅极电容器进行充电和放电,并且在同步整流器fet的栅极处产生升压电压,如本文所述。

46.在另一实施例中,初级侧控制器包括脉冲接收器和栅极驱动器。脉冲接收器跨越电隔离屏障从次级侧控制器接收第一信号。第一信号包括用于导通初级侧电力开关的第一导通脉冲和用于关断初级侧电力开关的第一关断脉冲。作为响应,耦接到脉冲接收器和初级侧电力开关的驱动器向初级侧电力开关施加第一导通脉冲和第一关断脉冲。

47.在另一实施例中,ac-dc电源适配器装置包括耦接于初级侧控制器与次级侧控制器之间的脉冲变压器。初级侧控制器被配置为经由脉冲变压器从次级侧控制器接收第一信号作为一个或多个脉冲。如本文所述,初级侧控制器可以检测次级侧控制器何时经由脉冲变压器传送信息。

48.本文描述的实施例可以在供电系统,例如兼容串行总线的供电装置中实施。兼容串行总线的供电装置的示例可以包括串行总线供电(sbpd)装置、兼容usb的供电装置等。在一些实施例中,sbpd装置是与usb-pd标准或更一般地与usb标准兼容的usb-pd装置。例如,sbpd装置可以用于基于输入电压(例如,vbus_in,电源电压)提供输出电压(例如,vbus_c,电源电压)。sbpd装置可以包括本文描述的各种实施例,以促进初级侧控制器与次级侧控制

器之间的通信。sbpd装置可以包括电力转换器(例如,ac-dc转换器)和功率控制模拟子系统(例如,usb-pd控制器)。功率控制模拟子系统可以包括如本文所述的电路、功能或两者,用于跨越电隔离屏障传送信息。

49.在实施例中,sbpd装置连接到电源,例如提供ac电力的壁式插座电源。在其他实施例中,电源可以是不同的电源,例如电池,并且可以向sbpd装置提供dc电力。电力转换器可以转换从电源接收的电力(例如,将接收的电力转换成vbus_in,其可以在3.3v到21.5v的范围内)。例如,电力转换器可以是ac-dc转换器,并且将来自电源的ac电力转换成dc电力。在一些实施例中,电力转换器是反激转换器,例如次级受控反激转换器,其在输入(例如,初级侧)与输出(例如,次级侧)之间提供电隔离。在另一实施例中,该装置可以是从sbpd装置接收电力的耗电方装置,其中,耗电方装置可以采用具有自适应转换速率控制的同步开关方案,以对其栅极电容器进行充电和放电,并且利用集成到耗电方装置的次级侧控制器上的sbpd在其同步整流器fet的栅极处产生升压电压。

50.在一些实施例中,sbpd装置(例如,经由指定特定输出电压,可能还指定输出电流的通信信道(cc))向接收方装置(sink device)提供vbus_c。sbpd装置还可以向接收方装置提供对地电势(例如,地)的访问权。在一些实施例中,vbus_c的提供与usb-pd标准兼容。功率控制模拟子系统可以从电力转换器接收vbus_in。功率控制模拟子系统可以输出vbus_in。在一些实施例中,功率控制模拟子系统是与usb c型标准兼容的usb c型控制器。功率控制模拟子系统可以响应于vbus_in和vbus_c提供系统中断。

51.在一些实施例中,sbpd装置的任何部件都可以是ic的一部分,或者替代地,sbpd装置的任何部件都可以在其自己的ic中实施。例如,电力转换器和功率控制模拟子系统均可以是具有独立封装和引脚配置的分立ic。

52.在一些实施例中,sbpd装置可以为笔记本、加密狗、监视器、扩充口、电源适配器、车辆充电器、充电宝、移动适配器等提供完整的usb c型和usb-pd端口控制解决方案。

53.确定usb-pd电源适配器100中的效率的一个元件是同步整流器fet 112(也称为次级侧fet),其并联耦接到同步整流器二极管192。同步整流器fet 112的导通电阻(rdson)可以确定同步整流器fet 112两端的电压降。另外,同步整流器fet的导通和关断时间可以确定同步整流器二极管192两端的功率损失,因为在导通过程期间,同步整流器二极管192会传导电流,直到同步整流器fet 112被导通。此外,可能需要更快的关断,因为一旦导体电流过零,它会在vbus到地之间形成短接。可以通过升高同步整流器fet 112的栅极处的电压(例如,升到~10v)来实现同步整流器fet 112的更低导通电阻。更快的导通和关断时间(例如,~100ns)可以由srgd的驱动强度确定。然后,为了在最慢工艺-电压-温度(pvt)角处满足更快的导通和关断时间,在快pvt角中,可能会有高峰值电流和增大的电源和地噪声的不利影响。图2更详细地描述了具有自适应转换速率控制的同步开关方案,其被设计成使功耗最小化,在栅极电容器与同步整流器fet的栅极之间循环利用栅极电荷,并且减小srgd的峰值电流和噪声。

54.图2是根据一个实施例的同步开关方案的时序图,其示出了反激转换器的次级侧上的开关电流和电压波形。再次参考图1,最初,在初级侧fet 110导通并且同步整流器fet 112关断时,曲线图202所示的初级电流增大。电压图206示出了同步整流器fet 112的漏极节点(sr_drain)上的电压增大到100v。在应当关断初级侧fet 110并且导通同步整流器fet

时,初级电流减小,如曲线图202所示,并且次级电流增大,如曲线图204所示。同步整流器fet 112的漏极节点上的电压降低到-0.7v,这触发了电压图208所示的负感测检测。负感测检测触发延迟以导通srgd 136,如电压图210所示。在初级侧fet 110关断并且同步整流器fet 112导通时,曲线图204中的电流减小。同步整流器fet 112的漏极上的电压降低。在该电压过零时,触发过零检测,如曲线图212所示。同步整流器fet的栅极上的电压降低,并且花费一定时间量达到0v。该时间量是关断同步整流器fet的延迟。

55.图3是根据一个实施例的集成于次级受控反激转换器中的次级侧控制器上的srgd的相位和转换控制器电路380的示意图。尽管未示出次级受控反激转换器的所有部件,但次级受控反激转换器类似于图1的usb-pd电源适配器的次级受控反激转换器,如类似附图标记所示。相位和转换控制器可以将第一信号与耦接到同步整流器fet的栅极的端子311上的电压进行比较,并且产生控制信号以绝热地对栅极电容器390进行充电和放电,并且通过分相位地将来自耦接到同步整流器fet的栅极的端子311的电荷循环利用到栅极电容器390,来产生2*vddd的升压电压(例如,电源电压的两倍)。

56.第一相位ф1可以是srgd的默认相位。在第一相位中,耦接到栅极电容器390的第一极板的端子389被上拉到电源电压电平(vddd),而耦接到同步整流器fet的栅极的端子311和耦接到栅极电容器390的第二极板的端子391被下拉到地(0v)。在第一相位期间,相位和转换控制器电路380可以在同步整流器fet的栅极处测量具有第一电压的信号,并且将第一电压与第二电压(例如,电源电压或vddd)进行对比。在第一相位期间,第一电压低于第二电压。在第二相位期间,耦接到同步整流器fet的栅极的端子311开始充电到高达电源电压电平vddd。在第二相位期间,相位和转换控制器电路380测量同步整流器fet的栅极处的第二信号。在第二信号的电压等于第二电压(例如,vddd)时,触发第三相位。在一个实施例中,比较器384检测耦接到同步整流器fet的栅极的端子311处的电压何时达到电源电压电平vddd,并且触发第三相位。在第三相位ф3中,耦接到栅极电容器的第二极板的端子391被上拉到电源电压电平vddd,并且耦接到同步整流器fet的栅极的端子311可以通过耦接到栅极电容器的第一极板的端子389被上拉到升压电压电平2*vddd。在第三相位期间,相位和转换控制器电路380测量第三信号。在第三相位结束时,第三信号的电压达到大于第二电压电平的第三电压电平(例如,2*vddd)。在第四相位期间,发生电荷循环利用,并且电荷从耦接到同步整流器fet的栅极的端子311移动到耦接到栅极电容器390的第一极板的端子389。然后可以重复相位的循环。应当注意,使用相位的名称是为了简化描述。

57.图4是根据一个实施例的对应于由相位和转换控制器产生的控制信号以实现集成于次级受控反激转换器中的次级侧控制器上的srgd的操作的相位的时序和电压图400。在图3中描述了srgd的操作的相位,并且稍晚在图7中更详细地对其进行描述。在一个实施例中,相位和转换控制器可以是图3的相位和转换控制器380。再次参考图1,曲线图402示出了在srgd 136的输出(sr_gdrv)处的同步整流器fet 112的栅极上的电压电平。曲线图404示出了相位和转换控制器产生的第一控制信号,以启用srgd的操作的第一相位,其中,同步整流器fet 112的栅极可以处于0v,栅极电容器190的第一极板可以处于第一电压电平(vddd,例如,5v、3.3v、3.5v等),并且栅极电容器190的第二极板可以处于0v。曲线图406示出了由相位和转换控制器产生的第二控制信号,以启用第二相位,在第二相位期间,同步整流器fet的栅极开始从0v充电到第一电压电平(例如,vddd)。曲线图408示出了由相位和转换控

制器产生的第三控制信号,以启用srgd的操作的第三相位。在同步整流器fet 112的栅极处的电压达到第一电压电平(vddd)时,相位和转换控制器可以被触发以产生第三控制信号,以启用第三相位。在第三相位期间,同步整流器fet 112的栅极被从第一电压电平(vddd)充电到第二电压电平(2*vddd,例如,10v、6.6v、7v等),栅极电容器的第一极板被从第一电压电平(vddd)充电到第二电压电平(2*vddd),并且栅极电容器的第二极板被从0v充电到第一电压电平(vddd)。可以在第三相位与第一相位之间过渡期间进行电荷循环利用(例如,从同步整流器fet 112的栅极到栅极电容器的第一极板)。应当注意,尽管相对所述实施例为vddd和2*vddd使用了5v和10v,但替代地,vddd和2*vddd可以是其他值。类似地,在其他实施方式中,可以实现除2或近似2之外的乘数。

58.图5是根据一个实施例的集成于次级受控反激转换器中的次级侧控制器上的srgd 536的框图。尽管未示出次级受控反激转换器的所有部件,但次级受控反激转换器类似于图1的usb-pd电源适配器的次级受控反激转换器,如类似附图标记所示。所示实施例示出了几乎不消耗电力并且可靠的次级侧栅极驱动器(例如,srgd 536)的新架构。srgd 536可以产生是ic电源电压(vddd)两倍的输出电压。srgd 536包括升压电压发生器电路560、栅极驱动器电路570以及相位和转换控制器电路580。srgd 536经由端子589和591耦接到栅极电容器590并且经由端子511耦接到同步整流器fet(图5中未示出)的栅极。升压电压发生器电路560、栅极驱动器电路570和相位和转换控制器电路580的组合被配置为在同步整流器fet的端子511上产生升压电压。

59.升压电压发生器电路560负责在栅极电容器590的第一端子589(sr_cpp)上产生升压电压供应(2*vddd)。升压电压发生器电路驱动栅极电容器590,并且使用自举原理在栅极电容器590的第一端子589(sr_cpp)上产生升压电压供应。在一个实施例中,栅极电容器590可以具有100nf的电容。升压电压发生器电路560包括第一上拉路径561、第二上拉路径562和下拉路径563。

60.栅极驱动器电路570被配置为驱动同步整流器fet(图5中未示出)。栅极驱动器电路570包括第一上拉路径571、第二上拉路径572和下拉路径573。

61.相位和转换控制器电路580被配置为针对srgd 536的操作的不同相位产生控制信号,并且进一步被配置为为srgd 536产生所需转换。相位和转换控制器电路通过跟踪同步整流器fet的端子511上的电压电平针对不同操作相位产生控制信号。在一个实施例中,为了跟踪同步整流器fet的端子511上的电压电平,相位和转换控制器电路测量同步整流器fet的栅极上的电压,并且将其与ic的电源电压(vddd)进行比较。可以由比较器,例如跟踪比较器584进行比较。相位和转换控制器电路580包括相位和驱动强度控制器581、电流发生器582、转换发生器583、跟踪比较器584和偏置发生器585。

62.图6是根据一个实施例的耦接到集成于次级受控反激转换器中的次级侧控制器上的srgd的相位和转换速率控制器电路的升压电压发生器电路和栅极驱动器电路的实施方式的框图。尽管未示出次级受控反激转换器的所有部件,但次级受控反激转换器类似于图1的usb-pd电源适配器的次级受控反激转换器,如类似附图标记所示。

63.电压发生器电路(例如,用于产生升压电压)包括上拉路径661、上拉路径662和下拉路径663。上拉路径661耦接到栅极电容器(例如,图1的栅极电容器190,图6中未示出)的端子689。上拉路径661进一步耦接到处于电压电平vddd的节点602。节点602耦接于上拉路

径662与上拉路径661之间。上拉路径662耦接于节点602与栅极电容器(例如,图1的栅极电容器190,图6中未示出)的端子691之间。下拉路径663耦接于栅极电容器的端子691与节点604之间。节点604处于电压电平vgnd,该电压电平低于vddd。

64.栅极驱动器电路包括上拉路径671、上拉路径672和下拉路径673。上拉路径671耦接于栅极电容器的端子689与耦接到同步整流器fet(例如,图1的同步整流器fet 112,图6中未示出)的栅极的端子611之间。上拉路径672耦接到上拉路径671并且进一步耦接于节点602与同步整流器fet的端子611之间。下拉路径673耦接到上拉路径672和节点604。

65.诸如上拉路径661、662、671和672的上拉路径可以是电路,以在被启用时提供通往节点602(处于vddd电压电平)的低电阻路径,并且在被禁用时提供通往节点602的高电阻路径。诸如上拉路径661、662、671和672的上拉路径可以是上拉元件、电流源、电阻元件等。可以使用开关、fet、mosfet等启用或禁用上拉路径661、662、671和672。诸如下拉路径663和673的下拉路径可以是电路,其用于在被启用时提供通往节点604(处于vgnd电压电平)的低电阻路径,并且在被禁用时提供通往节点604的高电阻路径。诸如下拉路径663和673的下拉路径可以是下拉元件、电流接收方(current sink)、电阻元件等。可以使用开关、fet、mosfet等启用或禁用下拉路径663和673。可以从相位和转换控制器提供用于启用或禁用srgd的上拉路径和下拉路径的控制信号。

66.上拉路径661(sr_cpp上拉)包括耦接到驱动强度和转换速率控制器686的开关664(p2)。在一个实施例中,开关664可以是p沟道fet(peft)。再次参考图5,驱动强度和转换速率控制器可以包括相位和驱动强度控制器581、电流发生器582(例如,驱动强度跟踪iref发生器)和转换发生器583(例如,基于延迟的转换发生器)。驱动强度和转换速率控制器686可以提供控制信号以启用或禁用(例如,接通或断开;或者导通或关断)开关664。开关664耦接到开关665(p3)。开关665耦接到电平移位器692。在一个实施例中,电平移位器692是sr_cpp电平移位器。在一些实施例中,电平移位器692可以是逻辑电平移位器或电压电平变换器。在一些实施例中,电平移位器692可以是单向电平移位器或双向电平移位器。开关665耦接到电阻器666a,并且电阻器666a耦接到栅极电容器的端子689(sr_cpp)。开关664耦接到处于电压电平vddd的节点602。

67.上拉路径662(sr_cpn上拉)包括耦接到节点602的开关667(p1)。开关667进一步耦接到驱动强度和转换速率控制器686,驱动强度和转换速率控制器686可以提供控制信号以启用或禁用开关667。电阻器666b耦接于开关667与栅极电容器的端子691(sr_cpn)之间。

68.下拉路径663(sr_cpn下拉)包括耦接于栅极电容器的端子691与开关668(n1)之间的电阻器666c。开关668耦接到驱动强度和转换速率控制器686,驱动强度和转换速率控制器686可以提供控制信号以启用或禁用开关668。开关668进一步耦接到处于vgnd电压电平的节点604。在一些实施例中,开关668可以是n沟道fet(neft)。

69.上拉路径671(升压驱动上拉)包括耦接于同步整流器fet的端子611(sr_gdrv)与开关674(p4)之间的电阻器676a。开关674耦接到自适应偏置控制器687(自适应偏置sr_cpp)。再次参考图5,自适应偏置控制器687可以包括相位和驱动强度控制器581、比较器584(例如,sr_dgrv跟踪比较器)和自适应偏置发生器585(例如,用于升压上拉的自适应偏置)。自适应偏置控制器687用于发送控制信号以启用或禁用(例如,导通或关断)开关674(例如,通过在开关674的栅极处产生电压,以便使峰值电流最小化并且满足栅极驱动器(srgd)的

上升和下降时间要求),并且在同步整流器fet的端子611处产生电压(例如,升压电压或驱动器电压)。电阻器676b耦接于栅极电容器的端子689与开关674之间。

70.上拉路径672(vddd上拉)包括耦接于同步整流器fet的端子611与开关675(p5)之间的电阻器676c。开关675耦接到电平移位器692。开关675耦接到开关677(p6)。开关677耦接到驱动强度和转换速率控制器686,驱动强度和转换速率控制器686可以提供控制信号以启用或禁用开关677。开关677进一步耦接到处于电压电平vddd的节点602。

71.下拉路径673(下拉)包括耦接到同步整流器fet的端子611和驱动强度和转换速率控制器686的开关678(n2)。驱动强度和转换速率控制器可以提供控制信号以启用或禁用开关678。开关678进一步耦接到处于vgnd电压电平的节点604。

72.开关664、665、667、668、674、675、677和678可以是n沟道fet(nfet)、p沟道fet(peft)、双极型晶体管等,或不同类型开关的任意组合。驱动强度和转换速率控制器686可以处于vddd电压电平。电平移位器692和自适应偏置控制器687可以处于2*vddd电压电平(例如,vddd电压电平两倍的电压电平)。自适应偏置控制器用于发送控制信号以启用或禁用(例如,导通或关断)开关(例如,通过在开关的栅极处产生电压,以便使峰值电流最小化并且满足栅极驱动器(srgd)的上升和下降时间要求)。电阻器666a、666b、676a、676b和676c可以是上拉元件、电阻元件等。电阻器666c可以是下拉元件、电阻元件等。

73.再次参考图5,相位和转换控制器电路580用于产生控制信号以启用或禁用上拉路径661、662、671和672,以及启用或禁用下拉路径663和673。通过启用或禁用上拉路径661、662、671和672和下拉路径663和673,相位和转换控制器电路580可以控制srgd以在第一相位、第二相位、第三相位或第四相位中的一个相位中操作,以便实施具有自适应转换速率控制的同步开关方案,以绝热地对栅极电容器590进行充电和放电,并且在同步整流器fet的端子511处产生升压电压(例如,2*vddd),如参考图7更详细所述。可以通过随时间启用(例如,导通)更多装置来控制转换速率,并且可以通过自适应转换控制电路来控制自适应延迟,如参考图12a-图12b更详细所述。应当注意,在其他实施方式中,可以将多个fet变为其他配置,以绝热地对栅极电容器进行充电和放电,用于在同步整流器fet上产生升压电压。

74.图7是示出了根据一个实施例的集成于usb-pd电源适配器的次级侧控制器上的srgd操作期间的栅极电容器和同步整流器fet的栅极上的电压的时序图。分别示出了栅极电容器的负极板、栅极电容器的正极板和同步整流器fet的栅极上的电压的例示时序图791、789和711。在一些实施例中,具有自适应转换速率控制的同步开关方案用于绝热地对栅极电容器(例如,图1的栅极电容器190或图5的栅极电容器590)进行充电和放电,并且在同步整流器fet(例如,图1的同步整流器fet 112)的栅极处产生大于次级侧控制器的电源电压(vddd)的升压电压(例如,2*vddd或大致2*vddd),该方案可以将次级侧控制器的功耗减小30%。并非使用电荷泵直接将栅极电容器充电到升压电压,而是可以绝热地(例如,消耗极少或不消耗能量)对栅极电容器进行充电。可以分相位对栅极电容器进行充电和放电,其中,相变取决于电源电压(vddd)与同步整流器fet的栅极上电压之间的相对电压差。本公开中描述的srgd(例如,图1的srgd 136或图5的srgd 536)可以具有关于栅极电容器的正极板(例如,第一极板,图1的极板189、图5的极板(或端子)589或图6的极板(或端子)689)、同步整流器fet的负极板(例如,第二极板,图1的极板191、图5的极板(或端子)591或图6的极板(或端子)691)和栅极(例如,图5的栅极(或端子)511或图6的栅极(或端子)611)上的电压

的信息。

75.在所示实施例中,栅极电容器的正极板可以具有升压开关电源电压,其值的范围可以在芯片内部电源电压vddd与2*vddd之间。栅极电容器的正极板可以充当升压电压上拉(例如,图5的第一上拉路径571或图6的上拉路径671)的源。栅极电容器的负极板上的电压的范围可以在0v与vddd之间,以便在栅极电容器的正极板上产生升压电压供应(2*vddd)。图5的端子511或图6的端子611可以耦接到srgd的输出以驱动同步整流器fet的栅极电压。srgd用于在一系列相位中控制栅极电容器的正极板、栅极电容器的负极板和同步整流器fet的栅极上的电压。

76.将参考图5-图6完成对图7的其余描述。最初,同步整流器fet的栅极处于0v,栅极电容器的负极板处于0v,并且栅极电容器的正极板处于电压vddd。在第一相位(ф1)期间,srgd导通,并且相位和转换控制器580产生控制信号以启用上拉路径672。同步整流器fet的栅极上的电压从0v增大到vddd。在第一相位期间,栅极电容器的正极板和负极板上的电压不变。为了将栅极驱动器的端子611(sr_gdrv)(例如,其耦接到同步整流器fet的栅极)充电到vddd,启用(例如,导通)上拉路径672(vddd上拉)。在将端子611上的电压从0v充电到vddd的同时,跟踪比较器584将端子611上的电压与电源电压vddd进行比较。在端子611上的电压达到vddd时,跟踪比较器584指示第一相位的结束和第二相位的开始。

77.在第二相位(ф2)期间,相位和转换控制器580产生控制信号以禁用(例如,关断)上拉路径672和上拉路径661并且启用上拉路径662,以便将栅极电容器的负极板(例如,端子691)拉高。栅极电容器的负极板上的电压从0v变为vddd,栅极电容器的正极板上的电压从vddd变为2*vddd,并且端子611上的同步整流器fet的栅极上的电压从vddd变为2*vddd。导通从升压供应(sr_cpp)到端子611(例如,srgd输出(sr_gdrv))的路径。偏置发生器585(用于升压上拉的自适应偏置)偏置上拉路径671,这会将端子611充电到2*vddd(升压电压供应)。在端子611上的电压达到2*vddd时,跟踪比较器584指示第二相位的结束。可以维持栅极电容器的负极板、栅极电容器的正极板和同步整流器fet的栅极上的电压,直到启用第三相位。

78.在第三相位(ф3)期间,相位和转换控制器580产生控制信号以启用下拉路径663,以便将栅极电容器的正极板从2*vddd拉到vddd。来自端子611处的同步整流器fet的栅极的电荷通过上拉路径671被循环回到栅极电容器,并且同步整流器fet的栅极从2*vddd变为vddd。栅极电容器的负极板从vddd变为0v。在端子611上的电压达到vddd(或几乎达到vddd)时,跟踪比较器584指示第三相位的结束和第四相位的开始。

79.在第四相位(ф4)期间,相位和转换控制器580产生控制信号以启用(例如,导通)下拉路径673,以便将端子611拉到地(0v)。启用上拉路径661以在开关周期期间对栅极电容器的电荷损失重新充电。在端子611上的电压达到0v时,跟踪比较器584指示第四相位的结束。然后可以重复开关循环。

80.图8是根据一个实施例的集成于次级受控反激转换器中的次级侧控制器上的具有基于延迟的相位发生器882的srgd 836的框图。尽管未示出次级受控反激转换器的所有部件,但次级受控反激转换器类似于图1的usb-pd电源适配器的次级受控反激转换器,如类似附图标记所示。所示实施例示出了几乎不消耗电力并且可靠的次级侧栅极驱动器(例如,srgd 836)的架构。srgd 836可以产生是芯片电源电压(vddd)两倍的输出电压。srgd 836包

括升压电压发生器电路860、栅极驱动器电路870以及相位和转换控制器电路880。srgd 836经由端子889和891耦接到栅极电容器890,并且经由端子811耦接到同步整流器fet(图8中未示出)的栅极。升压电压发生器电路860、栅极驱动器电路870和相位和转换控制器电路880的组合被配置为在同步整流器fet的端子811上产生升压电压。

81.升压电压发生器电路860负责在栅极电容器890的第一端子889(sr_cpp)上产生升压电压供应(2*vddd)。升压电压发生器电路驱动栅极电容器890并且使用自举原理在栅极电容器890的第一端子889(sr_cpp)上产生升压电压供应。在一个实施例中,栅极电容器890可以具有100nf的电容。升压电压发生器电路860包括第一上拉路径861、第二上拉路径862和下拉路径863。

82.栅极驱动器电路870被配置为驱动同步整流器fet(图8中未示出)。栅极驱动器电路870包括第一上拉路径871、第二上拉路径872和下拉路径873。

83.相位和转换控制器电路880被配置为针对srgd 836的操作的不同相位产生控制信号,并且进一步被配置为为srgd 836产生所需的转换。相位和转换控制器电路通过跟踪同步整流器fet的端子811上的电压电平针对不同的操作相位产生控制信号。在一个实施例中,为了跟踪同步整流器fet的端子811上的电压电平,相位和转换控制器电路测量同步整流器fet的栅极上的电压并且将其与ic的电源电压(vddd)进行比较。可以由比较器,例如跟踪比较器884进行比较。相位和转换控制器电路880包括相位和驱动强度控制器881、基于延迟的相位发生器882、转换发生器883、跟踪比较器884和偏置发生器888。

84.srgd 800的操作可以类似于图5的srgd 500的操作,但并非跟踪端子811上的电压并且使用高速比较器(例如,跟踪比较器884)将其与电源电压(vddd)进行比较,而是可以使用基于时间的方法。在本实施例中,相位和转换控制器880产生控制信号不取决于跟踪比较器884的响应。在由基于延迟的相位发生器882定义的固定时间延迟之后,产生用于在第二相位与第三相位之间切换的控制信号。

85.图9是示出了根据一个实施例的集成于usb-pd电源适配器的次级侧控制器上的具有基于延迟的相位发生器的srgd的操作期间栅极电容器和同步整流器fet栅极上的电压的时序图。分别示出了栅极电容器的负极板、栅极电容器的正极板和同步整流器fet的栅极上的电压的例示时序图991、989和911。可以分相位对栅极电容器(例如,图1的栅极电容器190或图8的栅极电容器890)进行充电和放电,其中,相变取决于固定时间。在一个实施例中,可以启用相位保持一定时间量,该时间量不取决于同步整流器fet的栅极与电源电压(vddd)之间的相对电压。在一个实施例中,可以启用第一相位保持固定时间量,该时间量不取决于同步整流器fet的栅极与电源电压(vddd)之间的相对电压,但可以基于同步整流器栅极电容而编程。栅极驱动器将在这个延迟持续时间内处于相位一中,并且在定时器完成该延迟时,基于延迟的相位发生器产生控制信号,用于进入第二相位,此时,栅极驱动器进入第二相位。在第二相位中,栅极电容器的负极板(sr_cpn)被充电到vddd电平,栅极电容器的正极板(sr_cpp)被充电到2*vddd电平,并且同步整流器fet的栅极被充电到2*vddd电平。类似地,在放电相位(例如,第三相位)期间,sr_cpn被下拉到地,并且电荷被从同步整流器fet的栅极循环回到sr_cpp,直到基于延迟的相位发生器产生用于进入第四相位的控制信号,其中,同步整流器fet栅极上的下拉路径被启用以将其下拉到地。为改变相位而设置的延迟是可编程的,并且可以根据所附接的同步整流器fet的电容而设置。在一些实施例中,负极板

可以达到0v,正极板可以达到vddd,并且同步整流器fet的栅极可以同时达到0v。在srgd需要进入高状态(例如,供电)时,将栅极电容器的负极板(sr_cpn)拉高。

86.图10是根据一个实施例的耦接到集成于次级受控反激转换器中的次级侧控制器上的srgd的相位和转换速率控制器电路的升压电压发生器电路和具有一条上拉路径的栅极驱动器电路的实施方式的框图。尽管未示出次级受控反激转换器的所有部件,但次级受控反激转换器类似于图1的usb-pd电源适配器的次级受控反激转换器,如类似附图标记所示。

87.电压发生器电路包括上拉路径1061、上拉路径1062和下拉路径1063。上拉路径1061耦接到栅极电容器(例如,图1的栅极电容器190,图10中未示出)的端子1089。上拉路径1061进一步耦接到上拉路径1062。上拉路径1062耦接到栅极电容器(例如,图1的栅极电容器190,图10中未示出)的端子1091。下拉路径1063耦接于栅极电容器的端子1091与节点1004之间。节点1004处于电压电平vgnd,该电压电平低于vddd。

88.栅极驱动器电路包括上拉路径1071和下拉路径1073。上拉路径1071耦接于栅极电容器的端子1089与同步整流器fet(例如,图1的同步整流器fet 112,图10中未示出)的端子1011之间。

89.诸如上拉路径1061、1062和1071的上拉路径可以是电路,其用于被启用时提供通往节点(处于vddd电压电平)的低电阻路径,并且在被禁用时提供通往节点(处于vddd电压电平)的高电阻路径。可以使用开关、fet、mosfet等启用或禁用上拉路径1061、1062和1071。诸如下拉路径1063和1073的下拉路径可以是电路,其用于在被启用时提供通往节点1004(处于vgnd电压电平)的低电阻路径,并且在被禁用时提供通往节点1004的高电阻路径。可以使用开关、fet、mosfet等启用或禁用下拉路径1063和1073。可以从相位和转换控制器提供用于启用或禁用srgd的上拉路径和下拉路径的控制信号。

90.上拉路径1061(sr_cpp上拉)包括耦接到驱动强度和转换速率控制器1086的开关1064(p2)。在一个实施例中,开关1064可以是p沟道fet(peft)。再次参考图5,驱动强度和转换速率控制器可以包括相位和驱动强度控制器581、电流发生器582和转换发生器583。驱动强度和转换速率控制器1087可以提供控制信号以启用或禁用(例如,接通或断开;或者导通或关断)开关1064。开关1064耦接到开关1065(p3)。开关1065耦接到电平移位器1092。在一个实施例中,电平移位器是sr_cpp电平移位器。在一些实施例中,电平移位器1092可以是逻辑电平移位器或电压电平变换器。在一些实施例中,电平移位器1092可以是单向电平移位器或双向电平移位器。开关1065耦接到电阻器1066a,并且电阻器1066a耦接到栅极电容器的端子1089(sr_cpp)。

91.上拉路径1062(sr_cpn上拉)包括耦接到驱动强度和转换速率控制器1086的开关1067(p1),驱动强度和转换速率控制器1086可以提供控制信号以启用或禁用开关1067。电阻器1066b耦接于开关1067和栅极电容器与端子1091(sr_cpn)之间。

92.下拉路径1063(sr_cpn下拉)包括耦接于栅极电容器的端子1091与开关1068(n1)之间的电阻器1066c。开关1068耦接到驱动强度和转换速率控制器1086,驱动强度和转换速率控制器1086可以提供控制信号以启用或禁用开关1068。开关1068进一步耦接到处于vgnd电压电平的节点1004。在一些实施例中,开关1068可以是n沟道fet(neft)。

93.上拉路径1071(升压驱动上拉)包括耦接于耦接到同步整流器fet的栅极的端子

1011(sr_gdrv)与开关1074(p4)之间的电阻器1076a。开关1074耦接到自适应偏置控制器1087(自适应偏置sr_cpp)。再次参考图5,自适应偏置控制器1087包括自适应偏置发生器(例如,相位和驱动强度控制器581和偏置发生器585)。自适应偏置控制器1087用于发送控制信号以启用或禁用(例如,导通或关断)开关1074。电阻器1076b耦接于栅极电容器的端子1089与开关1074之间。

94.下拉路径1073(下拉)包括耦接到同步整流器fet的端子1011和驱动强度和转换速率控制器1086的开关1078(n2)。驱动强度和转换速率控制器1086可以提供控制信号以启用或禁用开关1078。开关1078进一步耦接到处于vgnd电压电平的节点1004。

95.开关1064、1065、1067、1068、1074和1078可以是n沟道fet(nfet)、p沟道fet(peft)、双极型晶体管等,或不同类型开关的任意组合。驱动强度和转换速率控制器1086可以处于vddd电压电平。电平移位器1092和自适应偏置控制器1087可以处于2*vddd电压电平(例如,vddd电压电平两倍的电压电平)。自适应偏置控制器用于发送控制信号以启用或禁用(例如,导通或关断)开关(例如,通过在开关的栅极处产生电压,以便使峰值电流最小化并且满足栅极驱动器(srgd)的上升和下降时间要求)。

96.再次参考图5,相位和转换控制器电路580用于产生控制信号以启用或禁用上拉路径1061、1062和1071,并且启用或禁用下拉路径1063和1073。通过启用或禁用上拉路径1061、1062和1071和下拉路径1063和1073,相位和转换控制器电路580可以控制srgd以在第一相位、第二相位、第三相位或第四相位中的一个相位中操作,以便实施具有自适应转换速率控制的同步开关方案,以绝热地对栅极电容器590进行充电和放电,并且在同步整流器fet的端子511处产生升压电压(例如,2*vddd)。

97.在图10中所示的实施例中,栅极电容器可以在第一相位和第二相位期间向端子1011处的同步整流器fet的栅极供应电荷。由于在栅极驱动器电路中仅有一个上拉路径,所以可以减小srgd的面积,这允许减少材料清单(bom)。

98.图11是根据一个实施例的耦接到集成于次级受控反激转换器中的次级侧控制器上的具有二极管的srgd的相位和转换速率控制器电路的升压电压发生器电路和栅极驱动器电路的实施方式的框图。尽管未示出次级受控反激转换器的所有部件,但次级受控反激转换器类似于图1的usb-pd电源适配器的次级受控反激转换器,如类似附图标记所示。

99.电压发生器电路包括二极管1161、上拉路径1162和下拉路径1163。二极管1161耦接到栅极电容器(例如,图1的栅极电容器190,图11中未示出)的极板1189。二极管1161进一步耦接到处于电压电平vddd的节点1102。节点1102耦接于上拉路径1162与二极管1161之间。上拉路径1162耦接于节点1102与栅极电容器(例如,图1的栅极电容器190,图11中未示出)的端子1191之间。下拉路径1163耦接于栅极电容器的端子1191与节点1104之间。节点1104处于电压电平vgnd,该电压电平低于vddd。

100.栅极驱动器电路包括上拉路径1171、上拉路径1172和下拉路径1173。上拉路径1171耦接于栅极电容器的端子1189与同步整流器fet(例如,图1的同步整流器fet 112,图11中未示出)的端子1111之间。上拉路径1172耦接到上拉路径1171,并且进一步耦接于节点1102与同步整流器fet的端子1111之间。下拉路径1173耦接到上拉路径1172和节点1104。

101.诸如上拉路径1162、1171和1172的上拉路径可以是电路,其用于在被启用时提供通往节点1102(处于vddd电压电平)的低电阻路径,并且在被禁用时提供通往节点1102的高

电阻路径。可以使用开关、fet、mosfet等启用或禁用上拉路径1162、1171和1172。诸如下拉路径1163和1173的下拉路径可以是电路,其用于在被启用时提供通往节点1104(处于vgnd电压电平)的低电阻路径,并且在被禁用时提供通往节点1104的高电阻路径。可以使用开关、fet、mosfet等启用或禁用下拉路径1163和1173。可以从相位和转换控制器提供用于启用或禁用srgd的上拉路径和下拉路径的控制信号。

102.上拉路径1162(sr_cpn上拉)包括耦接到节点1102的开关1167(p1)。开关1167进一步耦接到驱动强度和转换速率控制器1186,驱动强度和转换速率控制器1186可以提供控制信号以启用或禁用开关1167。电阻器1166b耦接于开关1167与栅极电容器的端子1191(sr_cpn)之间。

103.下拉路径1163(sr_cpn下拉)包括耦接于栅极电容器的端子1191与开关1168(n1)之间的电阻器1166c。开关1168耦接到驱动强度和转换速率控制器1186,驱动强度和转换速率控制器1186可以提供控制信号以启用或禁用开关1168。开关1168进一步耦接到处于vgnd电压电平的节点1104。在一些实施例中,开关1168可以是n沟道fet(neft)。

104.上拉路径1171(升压驱动上拉)包括耦接于同步整流器fet的端子1111(sr_gdrv)与开关1174(p4)之间的电阻器1176a。开关1174耦接到自适应偏置控制器1187(自适应偏置sr_cpp)。再次参考图5,自适应偏置控制器1187包括相位和驱动强度控制器581和偏置发生器585。自适应偏置控制器1187用于发送控制信号以启用或禁用(例如,导通或关断)开关1174。电阻器1176b耦接于栅极电容器的极板1189与开关1174之间。

105.上拉路径1172(vddd上拉)包括耦接于同步整流器fet的端子1111与开关1175(p5)之间的电阻器1176c。开关1175耦接到电平移位器1192。开关1175耦接到开关1177(p6)。开关1177耦接到驱动强度和转换速率控制器1186,驱动强度和转换速率控制器1186可以提供控制信号以启用或禁用开关1177。开关1177进一步耦接到处于电压电平vddd的节点1102。

106.下拉路径1173(下拉)包括耦接到同步整流器fet的端子1111和驱动强度和转换速率控制器1186的开关1178(n2)。驱动强度和转换速率控制器可以提供控制信号以启用或禁用开关1178。开关1178进一步耦接到处于vgnd电压电平的节点1104。

107.开关1167、1168、1174、1175、1177和1178可以是n沟道fet(nfet)、p沟道fet(peft)、双极型晶体管等,或不同类型开关的任意组合。驱动强度和转换速率控制器1186可以处于vddd电压电平。电平移位器1192和自适应偏置控制器1187可以处于2*vddd电压电平(例如,vddd电压电平两倍的电压电平)。

108.再次参考图5,相位和转换控制器电路580用于产生控制信号以启用或禁用上拉路径1162、1171和1172,并且启用或禁用下拉路径1163和1173,并且启用或禁用二极管1161。通过启用或禁用上拉路径1162、1171和1172和下拉路径1163和1173,以及二极管1161,相位和转换控制器电路580可以控制srgd以在第一相位、第二相位、第三相位或第四相位中的一个相位中操作,以便实施具有自适应转换速率控制的同步开关方案,以绝热地对栅极电容器590进行充电和放电,并且在同步整流器fet的端子511处产生升压电压(例如,2*vddd)。

109.在一个实施例中,二极管1161可以设置于srgd内部。在另一实施例中,二极管可以设置于srgd外部,例如在具有电源电压(vddd)电路的电路板上。参考图6,通过使用二极管代替上拉路径661(sr_cpp上拉),可以减小板的面积。

110.图12a是根据一个实施例的p型金属氧化物半导体(pmos)驱动强度跟踪电流发生

器1282a的示意图。再次参考图5,pmos驱动强度跟踪电流发生器1282a可以是电流发生器582。pmos驱动强度跟踪电流发生器1282a包括耦接到开关1204a的电流源1202a(其可以与绝对温度(ctat)电流源互补,在绝对温度电流源中,电流随着温度减小)。开关1204a耦接到电阻器1206a。开关1208a耦接于电阻器1206a、地电势1226a和电阻器1210a之间。开关1212a耦接到电阻器1210a。开关1214a耦接到开关1212a。开关1216a耦接于开关1214a与电流源1218a之间。电流源1218a可以是参考电流源(可以是电流相对于温度恒定的电流源)。开关1220a耦接到开关1216a。开关1222a耦接到开关1220a。pmos驱动强度跟踪电流发生器1282a的输出可以是电流1224a。

111.在一个实施例中,pmos驱动强度跟踪电流发生器1282a可以耦接到图6的上拉路径661、662和672。在一个实施例中,pmos驱动强度跟踪电流发生器1282a可以耦接到图6的开关664、667和677。在一个实施例中,pmos驱动强度跟踪电流发生器1282a可以耦接到图10的上拉路径1061和1062。在一个实施例中,pmos驱动强度跟踪电流发生器1282a可以耦接到图10的开关1064和1067。在一个实施例中,pmos驱动强度跟踪电流发生器1282a可以耦接到图11的上拉路径1162和1172。在一个实施例中,pmos驱动强度跟踪电流发生器1282a可以耦接到图11的开关1167和1186。

112.驱动强度跟踪电流发生器1282a可以用于产生电流1224a。驱动强度跟踪电流发生器1282a跟踪srgd上拉电路(例如,图6的上拉元件661、662和672;图10的上拉元件1061和1062;或图11的上拉元件1162和1172)的驱动强度。驱动强度跟踪电流发生器1282a跟踪对应于上拉元件的开关(例如,图6的开关664、667、674和677;图10的开关1065和1067;或图11的1167、1174和1186)的驱动强度,并且产生可能与驱动强度成反比的电流1224a。电流1224a可以用于(例如,由图13中更详细描述的基于延迟的转换发生器)产生延迟。在一个实施例中,更高的电流可以导致更慢工艺角的更小(例如,更低)延迟,并且更低的电流可以导致更快工艺角的更大(例如,更高)延迟。驱动强度跟踪电流发生器1282a与图13a中更详细所述的基于延迟的转换发生器组合,形成自适应转换控制电路,自适应转换控制电路可以耦接到图5的升压电压发生器电路560和栅极驱动电路570,以便自适应地控制转换速率。用于产生延迟的电流1224a为

[0113][0114]

其中,vtp是pmos阈值电压,k1是电流复制增益,并且rs1是电阻器1210a的电阻。应当注意,在其他实施例中并且经过轻微的修改,更高的电流可以导致更大(例如,更高)延迟,而更低电流可以导致更小延迟。

[0115]

图12b是根据一个实施例的n型金属氧化物半导体(nmos)驱动强度跟踪电流发生器1282b的示意图。再次参考图5,nmos驱动强度跟踪电流发生器1282b可以是电流发生器582。nmos驱动强度跟踪电流发生器1282b包括耦接到开关1214b的电流源1202b。开关1214b耦接到开关1212b。开关1212b耦接到电阻器1210b。电阻器1210b耦接到开关1208b。开关1208b耦接到开关1204b。开关1204b耦接到地电势1226b。开关1214b进一步耦接到开关1216b。开关1216b耦接到电流源1218b。电流源1218b可以是参考电流源(相对于温度恒定的电流源)。开关1216b耦接到开关1220b。开关1220b耦接到开关1222b。nmos驱动强度跟踪电流发生器1282ab的输出可以是电流1224b。

[0116]

在一个实施例中,nmos驱动强度跟踪电流发生器1282b可以耦接到图6的下拉路径663和673。在一个实施例中,nmos驱动强度跟踪电流发生器1282a可以耦接到图6的开关668和678。在一个实施例中,nmos驱动强度跟踪电流发生器1282b可以耦接到图10的下拉路径1063和1073。在一个实施例中,nmos驱动强度跟踪电流发生器1282a可以耦接到图10的开关1068和1078。在一个实施例中,nmos驱动强度跟踪电流发生器1282b可以耦接到图11的下拉路径1163和1173。在一个实施例中,nmos驱动强度跟踪电流发生器1282a可以耦接到图11的开关1168和1178。

[0117]

驱动强度跟踪电流发生器1282b可以用于产生电流1224b。驱动强度跟踪电流发生器1282b跟踪srgd下拉电路(例如,图6的下拉元件663和673;图10的下拉元件1063和1073;或图11的下拉元件1163和1173)的驱动强度。驱动强度跟踪电流发生器1282b跟踪对应于下拉元件的开关(例如,图6的开关668和678;图10的开关1068和1078;或图11的1168和1178)的驱动强度,并且产生可能与驱动强度成反比的电流1224b。电流1224b可以用于(例如,由图13中更详细描述的基于延迟的转换发生器)产生延迟。在一个实施例中,更高的电流可以导致更慢工艺角的更小(例如,更低)延迟,并且更低电流可以导致更快工艺角的更大(例如,更高)延迟。驱动强度跟踪电流发生器1282b与图13b中更详细所述的基于延迟的转换发生器组合,形成自适应转换控制电路,自适应转换控制电路可以耦接到图5的升压电压发生器电路560和栅极驱动电路570,以便自适应地控制转换速率。用于产生延迟的电流1224b为

[0118][0119]

其中,vtn是nmos阈值电压,k2是电流复制增益,rs2是电阻器1210b的电阻,并且rdson_ns11是开关1204b(线性mosfet ns11)的导通电阻。

[0120]

图13a是根据一个实施例的用于pmos器件的基于延迟的转换发生器1383a的示意图。基于延迟的转换发生器1383a耦接到一系列mosfet分支1304a。在一个实施例中,mosfet分支可以是peft。电流1324a被输入到基于延迟的转换发生器1383a。在一个实施例中,电流1324a可以是图12的电流1224a。在另一实施例中,电流1324a可以是外部部件产生的电流。电流1324a的电流源耦接到一系列电流饥饿反相器1302a(current-starved inverter)(例如,电流反相器)。电流饥饿反相器1302a可以以级联模式彼此耦接。电流饥饿反相器1302a中的参考电流1342a可以确定延迟。为了控制驱动器的转换速率,基于由基于延迟的转换发生器产生的延迟导通和关断mosfet分支1304a。

[0121]

在一个实施例中,基于延迟的转换发生器1383a可以耦接到pmos驱动强度跟踪电流发生器1282a。耦接到pmos驱动强度跟踪电流发生器1282a的基于延迟的转换发生器形成图6的驱动强度和转换速率控制器686。在一个实施例中,基于延迟的转换发生器1383a可以耦接到图6的上拉路径661、662和672。在一个实施例中,基于延迟的转换发生器1383a可以耦接到图6的开关664、667和677。在一个实施例中,基于延迟的转换发生器1383a可以耦接到图10的上拉路径1061和1062。在一个实施例中,基于延迟的转换发生器1383a可以耦接到图10的开关1064和1067。在一个实施例中,基于延迟的转换发生器1383a可以耦接到图11的上拉路径1162和1172。在一个实施例中,基于延迟的转换发生器1383a可以耦接到图11的开关1167和1186。

[0122]

图13b是根据一个实施例的用于nmos器件的基于延迟的转换发生器1383b的示意

图。基于延迟的转换发生器1383b耦接到一系列mosfet分支1304b。在一个实施例中,mosfet分支可以是neft。电流1324b被输入到基于延迟的转换发生器1383b。在一个实施例中,电流1324b可以是图12的电流1224b。在另一实施例中,电流1324b可以是外部部件产生的电流。电流1324b的电流源耦接到一系列电流饥饿反相器1302b。电流饥饿反相器1302b可以以级联模式彼此耦接。电流饥饿反相器1302b中的参考电流1342b可以确定延迟。为了控制驱动器的转换速率,基于由基于延迟的转换发生器产生的延迟导通和关断mosfet分支1304b。

[0123]

在一个实施例中,基于延迟的转换发生器1383b可以耦接到nmos驱动强度跟踪电流发生器1282b。耦接到nmos驱动强度跟踪电流发生器1282b的基于延迟的转换发生器形成图6的驱动强度和转换速率控制器686。在一个实施例中,基于延迟的转换发生器1383b可以耦接到图6的下拉路径663和673。在一个实施例中,基于延迟的转换发生器1383b可以耦接到图6的开关668和678。在一个实施例中,基于延迟的转换发生器1383b可以耦接到图10的下拉路径1063和1073。在一个实施例中,基于延迟的转换发生器1383b可以耦接到图10的开关1068和1078。在一个实施例中,基于延迟的转换发生器1383b可以耦接到图11的下拉路径1163和1173。在一个实施例中,基于延迟的转换发生器1383b可以耦接到图11的开关1168和1178。

[0124]

图14是根据一个实施例的srgd的具有自适应偏置控制器的上拉路径1471的示意图。尽管未示出srgd的所有部件,但srgd类似于图6的srgd,如类似附图标记所示。在一个实施例中,上拉路径1471可以是图6的上拉路径671。在另一实施例中,上拉路径1471可以是图10的上拉路径1071。在另一实施例中,上拉路径1471可以是图11的上拉路径1171。

[0125]

上拉路径1471(升压驱动上拉)包括耦接于同步整流器fet的栅极的输出1411(sr_gdrv)与开关1474(p4)之间的电阻器1476a。开关1474耦接到自适应偏置控制器1487(自适应偏置sr_cpp)。再次参考图5,自适应偏置控制器1487包括相位和驱动强度控制器581和偏置发生器585。自适应偏置控制器1487用于发送控制信号以启用或禁用(例如,导通或关断)开关1474。电阻器1476b耦接于栅极电容器的极板1489与开关1474之间。在一个实施例中,栅极电容器是图1的栅极电容器190。在另一实施例中,栅极电容器是图5的栅极电容器590。在另一实施例中,栅极电容器是图8的栅极电容器890。

[0126]

自适应偏置控制器1487包括耦接到开关1474的开关1402和耦接到开关1474和开关1402的开关1404。开关1402耦接到栅极电容器的极板1489。电流1406在开关1404与开关1474之间。电容器1410耦接于开关1402与开关1412之间。开关1414耦接到开关1412。电阻器1416耦接到开关1414。开关1418耦接于电阻器1416与电阻器1420之间。电阻器1420耦接到地电势1422。电流1424在电阻器1416与电阻器1420之间。

[0127]

例如,如图12a-图12b和图13a-图12b所述,自适应延迟发生帮助控制srgd在第一相位和第四相位期间操作于电源电压(vddd)下的区段,如参考图7所述。如参考图7所述,在第二相位和第三相位期间,srgd工作于升压电源电压(例如,2*vddd)下。自适应偏置控制器1487可以提供自适应偏置方案,以通过跟踪驱动强度并且减小工作于升压电源电压下的上拉路径上的峰值电流来规避这些问题。自适应偏置方案可以用于从升压电压供应(例如,栅极电容器的极板1489)到在同步整流器fet的栅极上供应电压的srgd的输出1411的路径。在一个实施例中,同步整流器fet可以是图1的同步整流器fet 112。自适应偏置控制器1487被配置为根据操作于升压电源电压下的srgd的上拉开关(例如,根据角和温度)产生偏置,以

自适应地控制升压上拉路径的驱动强度,并且可以帮助控制(例如,srgd的输出1411处的)栅极电压,以自适应地控制同步整流器fet的驱动强度。

[0128]

图15a是示出了根据一个实施例的用于自适应转换控制块中的srgd上拉路径角两端的pmos延迟单元的延迟变化的曲线图1500a。水平轴标记从左到右表示快pmos单元和快nmos单元、快pmos单元和慢nmos单元、慢pmos单元和快nmos单元、慢pmos单元和慢nmos单元以及典型的pmos单元和典型的nmos单元。曲线图1503对应于3v的电源电压电平vddd。曲线图1505a对应于5v的电源电压电平vddd。

[0129]

图15b是示出了根据一个实施例的用于自适应转换控制块中的srgd下拉路径角两端的nmos延迟单元的延迟变化是的曲线图1500b。水平轴标记从左到右表示快pmos单元和快nmos单元、快pmos单元和慢nmos单元、慢pmos单元和快nmos单元、慢pmos单元和慢nmos单元以及典型的pmos单元和典型的nmos单元。曲线图1503b对应于3v的电源电压电平vddd。曲线图1505b对应于5v的电源电压电平vddd。

[0130]

图16是根据一个实施例的usb-pd电源适配器1600的示意图,该电源适配器具有集成于次级侧控制器1616a(也称为电源适配器次级ic控制器)上的同步整流器栅极驱动器(srgd)1636a,以从供电方装置1672a向附接的耗电方装置1672b输送电力。在耗电方装置1672b连接到供电方1672a时,供电方srgd 1636a可以启用或禁用供电方fet 1638a(也称为供电方nfet、供电方开关、次级侧fet),以便向附接的耗电方装置1672c输送电力。例如,供电方次级栅极驱动器1636a可以在要向附接的耗电方装置1672b输送电力时启用供电方fet 1638a。替代地或此外,供电方次级栅极驱动器1636a可以在不向附接的耗电方装置1672c输送电力时禁用供电方fet 1638a。

[0131]

在一个实施例中,耗电方装置1672b可以是usb-pd耗电方,其具有集成于耗电方装置的次级侧控制器1616b上的同步整流器栅极驱动器(srgd)1636b,以从附接的供电方装置1672a接收电力(例如,为耗电方装置1672b的电池充电)。在供电方装置1672a连接到耗电方装置1672b(例如,充当电源)时,耗电方srgd 1636b可以启用或禁用耗电方fet 1638b(例如,耗电方nfet、耗电方开关),以便从附接的供电方装置1672a接收电力。例如,在一个实施例中,耗电方srgd 1636b可以在要从附接的供电方装置1672a接收电力以为电池充电时启用耗电方fet 1638b。替代地或此外,耗电方srgd 1636b可以在不从供电方装置1672a接收电力时禁用耗电方fet 1638b。

[0132]

在另一实施例中,耗电方装置1672b可以是usb-pd耗电方,以从附接的供电方装置1672a接收电力(例如,为耗电方装置1672b的电池充电)。在供电方装置1672a连接到耗电方装置1672b(例如,充当电源)时,供电方srgd 1636a可以启用或禁用供电方fet 1638a(例如,供电方nfet、供电方开关)和耗电方fet 1638b(例如,耗电方nfet、耗电方开关),使得供电方1672a向耗电方装置1672b提供电力,并且耗电方装置1672b从附接的供电方装置1672a接收电力。例如,在一个实施例中,供电方srgd 1636a可以在要从附接的供电方装置1672a接收电力以为电池充电时启用供电方fet 1638a和耗电方fet 1638b。替代地或此外,供电方srgd 1636b可以在不从供电方装置1672接收电力时禁用供电方fet 1638a和耗电方fet 1638b。

[0133]

尽管未示出耗电方srgd 1636b的所有部件,但耗电方srgd 1636b类似于供电方srgd 1636a,如类似附图标记所示。srgd 1636b包括升压电压发生器电路、栅极驱动器电路

以及相位和转换控制器电路。srgd 1636b耦接到栅极电容器(图16中未示出)和同步整流器fet(图16中未示出)的栅极。升压电压发生器电路、栅极驱动器电路以及相位和转换控制器电路的组合被配置为在同步整流器fet的栅极上产生升压电压。

[0134]

图17是示出根据一些实施例的用于usb供电中使用的usb装置的系统1700的框图。系统1700可以包括外围子系统1710,其包括用于usb-pd中使用的多个部件。外围子系统1710可以包括外围互连1711,其包括时钟模块、用于向外围子系统1710的各种部件提供时钟信号的外围时钟(pclk)1712。外围互连1711可以是外围总线,例如单级或多级高级高性能总线(ahb),并且可以提供外围子系统1710、cpu子系统1730和系统资源1740之间的数据和控制接口。外围互连1711可以包括控制器电路,例如直接存储器存取(dma)控制器,其可以被编程以在外围块之间传输数据,而无需cpu子系统1730的输入、控制或承担负担。

[0135]

外围互连1711可以用于将外围子系统1710的部件耦接到系统1700的其他部件。耦接到外围互连1711的可以是用于发送和接收信号的多个通用输入/输出(gpio)1715。gpio 1715可以包括被配置为实施各种功能的电路,例如上拉、下拉、输入阈值选择、输入和输出缓冲器启用/停用、单个多路复用等。还可以由gpio 1715实施其他功能。一个或多个计时器/计数器/脉宽调制器(tcpwm)1717也可以耦接到外围互连,并且包括用于实施计时电路(计时器)、计数器、脉宽调制器(pwm)解码器以及可以对i/o信号进行操作并且向系统1700的系统部件提供数字信号的其他数字功能的电路。外围子系统1710还可以包括一个或多个串行通信块(scb)1719,用于实施串行通信接口,例如i2c、串行外围接口(spi)、通用异步接收器/发射器(uart)、控制器局域网(can)、时钟扩展外围接口(cxpi)等。

[0136]

对于usb供电应用,外围子系统1710可以包括耦接到外围互连并且包括用于在usb供电中使用的一组usb-pd模块1721的usb供电子系统1720。usb-pd模块1721可以通过usb-pd互连1723耦接到外围互连1711。usb-pd模块1721可以包括模/数转换(adc)模块,用于将各种模拟信号转换为数字信号;误差放大器(amp),用于根据pd合约调节vbus线上的输出电压;高压(hv)调节器,用于将电源电压转换成供给电源系统1700的精确电压(例如3.5-5v);低侧电流读出放大器(lscsa),用于准确测量负载电流;过电压保护(ovp)模块和过电流保护(ocp)模块,用于以可配置的阈值和响应时间在vbus线上提供过电流和过电压保护;一个或多个栅极驱动器,用于在提供方和消耗方配置中的usb供电中使用的外部功率场效应晶体管(fet);以及通信信道phy(cc bb phy)模块,用于支持在c型通信信道(cc)线上的通信。usb-pd模块1721还可以包括用于确定存在充电电路并且耦接到系统1700的充电器检测模块以及用于控制vbus上电压放电的vbus放电模块。特别地,用于外部功率fet的一个或多个栅极驱动器包括集成于次级侧控制器上的同步整流器栅极驱动器(srgd),以提供具有自适应转换速率控制的同步开关方案,以绝热地对栅极电容器进行充电和放电,并且在同步整流器fet的栅极处产生升压电压(例如,2*vddd)。如本公开中所述,srgd包括升压电压发生器电路、栅极驱动器电路以及相位和转换控制器电路。放电控制模块可以被配置为耦接到vbus线上的电源节点或vbus线上的输出(电力接收方)节点,并且将vbus线上的电压放电至期望的电压电平(即,pd合约中协商的电压电平)。usb供电子系统1720还可以包括用于外部连接的焊盘1727和c型端口上可能需要的静电放电(esd)保护电路1729。usb-pd模块1721还可以包括通信模块,用于检索非易失性存储器中存储的信息并且在一个控制器与另一个控制器之间传送信息,例如,在反激转换器的初级侧控制器和次级侧控制器之间传送信息。

[0137]

gpio 1715、tcpwm 1717和scb 1719可以耦接到输入/输出(i/o)子系统1750,该子系统可以包括耦接到多个gpio 1753的高速(hs)i/o矩阵1751。gpio 1715、tcpwm 1717和scb 1719可以通过hs i/o矩阵1751耦接到gpio 1753。

[0138]

系统1700还可以包括用于处理命令、存储程序信息和数据的中央处理单元(cpu)子系统1730。cpu子系统1730可以包括用于执行指令以及从多个存储器中的存储器位置读取和向其写入的一个或多个处理单元1731。处理单元1731可以是适于在集成电路(ic)或片上系统(soc)装置中操作的处理器。在一些实施例中,处理单元1731可以针对具有广泛时钟门控的低功率操作而优化。在该实施例中,可以实施各种内部控制电路,用于在各种功率状态下的处理单元操作。例如,处理单元1731可以包括唤醒中断控制器(wic),其被配置为将处理单元从睡眠状态唤醒,从而允许在ic或soc处于睡眠状态时切断电源。cpu子系统1730可以包括一个或多个存储器,包括闪存存储器1733、静态随机存取存储器(sram)1735和只读存储器(rom)1737。闪存存储器1733可以是被配置为用于存储数据、程序和/或其他固件指令的非易失性存储器(nand闪存、nor闪存等)。闪存存储器1733可以包括读取加速器,并且可以通过集成在cpu子系统1730内来改进存取时间。sram 1735可以是被配置用于存储可由处理单元1731访问的数据和固件指令的易失性存储器。rom 1737可以被配置为存储引导例程、配置参数以及在系统1700的操作期间不改变的其他固件参数和设置。sram 1735和rom 1737可以具有相关联的控制电路。处理单元1731和存储器可以耦接到系统互连1739以将去往和来自cpu子系统1730的各种部件的信号路由到系统1700的其他块或模块。系统互连1739可以实施为诸如单级或多级ahb的系统总线。系统互连1739可以被配置为将cpu子系统1730的各种部件彼此耦接的接口。系统互连1739可以耦接到外围互连1711以提供cpu子系统1730与外围子系统1710的部件之间的信号路径。

[0139]

系统1700还可以包括多个系统资源1740,包括电源模块1741、时钟模块1743、复位模块1745和测试模块1747。电源模块1741可以包括睡眠控制模块、唤醒中断控制(wic)模块、上电复位(por)模块、多个电压参考(ref)和pwrsys模块。在一些实施例中,电源模块1741可以包括允许系统1700以不同的电压和/或电流电平从/向外部源汲取和/或提供电力并且支持控制器在不同的功率状态中操作的电路,所述功率状态例如运行中、低功率或睡眠。在各种实施例中,当系统1700对操作进行节流以实现期望的功耗或输出时,可以实施更多的功率状态。时钟模块1743可以包括时钟控制模块、看门狗计时器(wdt)、内部低速振荡器(ilo)和内部主振荡器(imo)。复位模块1745可以包括复位控制模块和外部复位(xres)模块。测试模块1747可以包括控制和进入测试模式的模块以及用于模拟和数字功能(数字测试和模拟dft)的测试控制模块。

[0140]

系统1700可以在单片(例如,单个)半导体管芯中实施。在其他实施例中,系统1700的各个部分或模块可以在不同的半导体管芯上实施。例如,cpu子系统1730的存储器模块可以是片上的或分离的。在其他实施例中,分离管芯电路可以被封装到单个“芯片”中,或者保持分离并且作为分离元件设置在电路板上(或usb电缆连接器中)。

[0141]

系统1700可以在多个应用情境中实施,以向其提供usb-pd功能。在每个应用情境中,ic控制器或soc实施系统1700可以被设置和配置在电子装置(例如,支持usb的装置)中以执行根据本文描述的技术的操作。在一个示例实施例中,系统1700可以被设置和配置在用于膝上型计算机、笔记本计算机等的个人计算机(pc)电源适配器中。在另一示例实施例

中,系统1700可以被设置和配置在用于移动电子装置(例如,智能电话、平板计算机等)的电源适配器(例如,壁式充电器)中。在另一示例实施例中,系统1700可以被设置和配置在被配置为通过(一个或多个)usb a型和/或c型端口提供电力的壁式插座中。在另一示例实施例中,系统1700可以被设置和配置在被配置为通过(一个或多个)usb a型和/或c型端口提供电力的车载充电器中。在又一示例实施例中,系统1700可以被设置和配置在可以得到充电并且然后通过usb a型或c型端口向另一电子装置提供电力的电源组中。在其他实施例中,类似于系统1700的系统可以配置有本文所述的电力开关栅极控制电路,并且可以设置在各种其他支持usb的电子或机电装置中。

[0142]

应当理解,系统,如在ic控制器上实施或实施为ic控制器的系统1700,可以被设置到不同的应用中,这些应用可以关于所使用的电源的类型和供电的方向而不同。例如,在车载充电器的情况下,电源是提供dc电力的车载电池,而在移动电源适配器的情况下,电源是ac壁式插座。此外,在pc电源适配器的情况下,供电流是从提供方装置到消耗方装置,而在电源组的情况下,供电流可以在两个方向上,这取决于电源组是作为电力提供方操作(例如,为另一装置供电)还是作为电力消耗方操作(例如,为其自身充电)。由于这些原因,系统1700的各种应用应当被认为是说明性的而不是限制性的。

[0143]

图18是根据一个实施例的方法1800的流程图,该方法通过具有自适应转换控制的srgd来同步地切换同步整流器fet,以便在绝热地对栅极电容器进行充电和放电,以循环利用电荷,并且在同步整流器fet的栅极上产生升压电压。方法1800可以由包括硬件(例如,电路、专用逻辑单元、可编程逻辑单元、微代码等)、软件、固件或其组合的处理逻辑单元执行。在一个实施例中,集成于usb-pd电源适配器的次级侧控制器上的srgd执行方法1800。在另一实施例中,图1的srgd136执行方法1800。在另一实施例中,图5的srgd 500执行方法1800。在另一实施例中,图6的srgd 600执行方法1800。在另一实施例中,图8的srgd 800执行方法1800。在另一实施例中,图10的srgd 1000执行方法1800。在另一实施例中,图11的srgd 1100执行方法1800。在另一实施例中,图16的srgd 1636a执行方法1800。在另一实施例中,图16的srgd 1636b执行方法1800。在另一实施例中,图17的srgd 1736执行方法1800。

[0144]

参考图18,方法1800开始于处理逻辑单元测量耦接到srgd的同步整流器fet的栅极处的栅极电压(框1802),所述srgd集成于次级侧受控交流到直流(ac-dc)转换器的次级侧控制器上。次级侧受控ac-dc转换器可以是ac-dc电源、ac-dc电力转换器。ac-dc电力转换器可以是具有电隔离屏障的次级受控ac-dc反激转换器。处理逻辑单元跨越ac-dc电力转换器的电隔离屏障控制初级侧fet(框1804)。处理逻辑单元将同步整流器fet的栅极处的栅极电压与次级侧控制器的电源电压(例如,vddd)进行比较(框1806)。处理逻辑单元根据比较栅极电压与电源电压的结果使srgd绝热地对栅极电容器进行充电或放电(框1808)。处理逻辑单元向同步整流器fet的栅极输出控制信号,以便驱动同步整流器fet(框1810)。一旦处理逻辑单元输出控制信号,方法1800就结束。

[0145]

在另一实施例中,在四个相位中的一个相位中对栅极电容器绝热地进行充电或放电。控制信号可以进一步向srgd发信号通知要操作的相位。在第一相位(ф1)期间,srgd被导通,并且同步整流器fet的栅极上的电压从0v变到vddd。在第一相位期间,栅极电容器的正极板和负极板上的电压不变。在第二相位(ф2)期间,栅极电容器的负极板上的电压从0v变为vddd,栅极电容器的正极板上的电压从vddd变为2*vddd,并且输出上的同步整流器fet

的栅极上的电压从vddd变为2*vddd。在第三相位(ф3)期间,栅极电容器的正极板上的电压从2*vddd变为vddd。同步整流器fet的栅极从2*vddd变为vddd。栅极电容器的负极板从vddd变为0v。在第四相位(ф4)期间,端子611上的电压达到0v。然后可以重复开关循环。

[0146]

在另一实施例中,处理逻辑单元控制该控制信号的延迟,以便控制srgd的转换速率。处理逻辑单元向srgd的栅极驱动器电路提供控制信号,使得栅极驱动器电路可以使用栅极电容器驱动同步整流器fet。

[0147]

在以上描述中,具体实施方式的一些部分是按照对计算机存储器内的数据位的操作的算法和符号表示来呈现的。这些算法描述和表示是数据处理领域的技术人员用来最有效地将他们工作的实质传达给本领域的其他技术人员的手段。算法在此处并且通常被认为是导致期望结果的步骤的自洽序列。这些步骤是需要对物理量进行物理操作的步骤。通常,尽管不是必须的,这些量采用能够被存储、传输、组合、比较和以其他方式操纵的电或磁信号的形式。主要出于通用的原因,将这些信号称为位、值、元素、符号、字符、项、数字等已被证明有时是方便的。

[0148]

然而,应当记住,所有这些和类似的术语都与适当的物理量相关联,并且仅仅是应用于这些量的方便的标记。除非特别声明,否则如从以上讨论中显而易见的,可以理解,在整个描述中,利用诸如“接收”、“调整”等术语的讨论指的是计算系统或类似电子计算装置的动作和过程,其将表示为计算系统的寄存器和存储器内的物理(例如,电子)量的数据操纵和变换成类似地表示为计算系统存储器或寄存器或其他这样的信息存储、传输或显示装置内的物理量的其他数据。

[0149]

词语“示例”或“示例性”在本文中用于表示用作示例、实例或说明。本文描述为“示例”或“示例性”的任何方面或设计未必应解释为比其他方面或设计优选或有利。相反,词语“示例”或“示例性”的使用旨在以具体的方式呈现概念。如本技术中所使用的,术语“或”旨在表示包括性的“或”而不是排他性的“或”。即,除非另外指定,或者从上下文中清楚,否则“x包括a或b”旨在表示任何自然的包括性排列。即,如果x包括a;x包括b;或者x包括a和b两者,则在任何前述情况下都满足“x包括a或b”。另外,除非另外指定或从上下文中清楚涉及单数形式,否则本技术和所附权利要求中使用的冠词“一”一般应当被解释为表示“一个或多个”。此外,除非如此描述,否则术语“实施例”或“一个实施例”的使用全文中不旨在表示相同的实施例。

[0150]

本文描述的实施例还可以涉及用于执行本文的操作的装置。该装置可以是为所需目的而专门构造的,或者它可以包括由存储在计算机中的计算机程序选择性地启动或重新配置的通用计算机。这样的计算机程序可以存储在非暂时性计算机可读存储介质中,例如但不限于任何类型的盘,包括软盘、光盘、cd-rom和磁光盘、只读存储器(rom)、随机存取存储器(ram)、eprom、eeprom、磁卡或光卡、闪存或适于存储电子指令的任何类型的介质。术语“计算机可读存储介质”应当被理解为包括存储一个或多个指令集的单个介质或多个介质(例如,集中式或分布式数据库和/或相关联的高速缓存和服务器)。术语“计算机可读介质”还应当被理解为包括能够存储、编码或承载用于由机器执行的指令集并且使机器执行本实施例的方法中的任何一个或多个的任何介质。术语“计算机可读存储介质”因此应当被认为包括但不限于固态存储器、光学介质、磁介质、能够存储用于由机器执行并且使机器执行本实施例的方法中的任何一个或多个的指令集的任何介质。

[0151]

本文提出的算法和显示并非固有地与任何特定计算机或其他装置相关。各种通用系统可以与根据本文的教导的程序一起使用,或者可以证明构造更专用的装置来执行所需的方法步骤是方便的。从下面的描述中将出现各种这些系统所需的结构。另外,没有参考任何特定编程语言来描述本实施例。应当理解,可以使用各种编程语言来实施如本文所述的实施例的教导。

[0152]

以上描述阐述了许多具体细节,例如具体系统、部件、方法等的示例,以便提供对本公开的若干实施例的良好理解。应当理解,上述描述旨在是说明性的而非限制性的。在阅读和理解以上描述的基础上,许多其他实施例对于本领域技术人员将是显而易见的。因此,本公开的范围应当参考所附权利要求以及这些权利要求享有权利的等同方案的全部范围来确定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。