1.本公开的实施例涉及一种储备池计算装置以及数据处理方法。

背景技术:

2.储备池计算(reservoir computing,rc)是循环神经网络中(recurrent neural network,rnn)的一个重要分支。rc在21世纪初期被首次提出,用于解决rnn训练中的梯度爆炸和梯度消失问题。作为一种rnn的实现方式,rc网络展现出了强大的时序信号处理能力。近年来,rc被广泛用于生物信号处理、混沌序列预测和模式识别等领域。

技术实现要素:

3.本公开至少一实施例提供一种储备池计算装置,包括:信号输入电路,配置为接收输入信号;储备池电路,所述储备池电路包括多个储备池单元,其中,所述多个储备池单元中的每个储备池单元包括:掩模单元,配置为接收所述输入信号且将所述输入信号使用第一权重进行第一处理,得到第一处理结果,以及旋转神经元单元,配置为从所述掩模单元接收所述第一处理结果,且对所述第一处理结果进行第二处理以进行升维、非线性运算和递归连接,以得到第二处理结果;输出层单元,配置为将所述多个储备池单元的多个第二处理结果与第二权重矩阵相乘,得到第三处理结果,并将所述第三处理结果输出。

4.例如,在本公开至少一实施例提供的储备池计算装置中,所述掩模单元包括:输入端,配置为接收所述输入信号;输入权重配置模块,配置为接收关于所述第一权重的控制信号,对所述输入端接收的所述输入信号与所述第一权重进行所述第一处理,得到所述第一处理结果;以及输出端,配置为将所述输入权重配置模块的所述第一处理结果输出。

5.例如,在本公开至少一实施例提供的储备池计算装置中,所述输入权重配置模块包括:反相器;多个开关,其中所述多个开关中每个开关包括:第一开关输入端,第二开关输入端,开关输出端,以及开关控制端,其中,所述第一开关输入端与所述掩模单元的输入端连接以接收所述输入信号,所述反相器与所述掩模单元的输入端连接以接收所述输入信号且将所述输入信号反相得到反相输入信号,所述第二开关输入端与所述反相器连接以接收所述反相输入信号,所述开关输出端与所述掩膜单元的输出端连接,所述开关控制端配置为接收所述控制信号,将所述第一开关输入端或所述第二开关输入端接收的信号从所述开关输出端输出。

6.例如,在本公开至少一实施例提供的储备池计算装置中,所述控制信号为随机控制信号。

7.例如,在本公开至少一实施例提供的储备池计算装置中,所述旋转神经元单元包括:n个前神经元转子电路,其中,所述n个前神经元转子电路中每一个前神经元转子电路包括第一选通信号端、第一输入端、排序为第1到第n的n个第一输出端;n个后神经元转子电路,其中,所述n个后神经元转子与所述n个前神经元转子电路一一对应,所述每一个后神经元转子电路包括第二选通信号端、排序为第1到第n的n个第二输入端、第二输出端;n个神经

元电路,其中,所述n个神经元电路中第m个神经元电路的第一端连接所述n个前神经元转子电路中每个的第m个第一输出端,所述n个神经元电路中第m个神经元电路的第二端连接所述n个后神经元转子电路中每个的第m个第二输入端;时序控制电路,与所述n个前神经元转子电路中每一个的第一选通信号端连接,与所述n个后神经元转子电路中每一个的第二选通信号端连接,配置为产生选通信号,由此将所述选通信号同时施加到所述n个前神经元转子电路与所述n个后神经元转子电路,其中,所述n个前神经元转子电路整体上配置为,根据所述选通信号,所述n个前神经元转子电路每个选通自身的n个第一输出端中的一个,且所述n个前神经元转子电路所选通的第一输出端的序号彼此不同,所述n个后神经元转子电路整体上配置为,根据所述选通信号,所述n个前神经元转子电路每个选通自身的n个第二输入端中的一个,且所述n个后神经元转子电路所选通的第二输入端的序号彼此不同,与同一个神经元电路连接的前神经元转子电路的第一输出端和后神经元转子电路的第二输入端同时被选通,n为大于1的正整数,m=1,2,

…

,n。

8.例如,在本公开至少一实施例提供的储备池计算装置中,所述选通信号的值随时间变化且使得在n个操作周期中:所述n个前神经元转子电路每个选通自身第1到第n个第一输出端被依序选通;所述n个后神经元转子电路每个选通自身第1到第n个第二输入端被依序选通。

9.例如,在本公开至少一实施例提供的储备池计算装置中,所述多个神经元电路中每一个神经元电路包括:非线性激活电路;积分电路;以及衰减电路,其中,所述非线性激活电路的第一端与所述神经元电路的输入端连接,所述非线性激活电路的第二端与所述神经元电路的输出端连接,所述积分电路的第一端与所述神经元电路的输出端连接,所述衰减电路的第一端与所述神经元电路的输入端连接,所述积分电路的第二端与所述衰减电路的第二端连接。

10.例如,在本公开至少一实施例提供的储备池计算装置中,所述非线性激活电路包括二极管,所述二极管的负极与所述神经元电路的输出端连接,所述二极管的正极与参考电压端连接,所述积分电路包括积分电阻和电容器,所述积分电阻的第一端与所述神经元电路的输入端连接,所述积分电阻的第二端与所述电容器的第一端以及所述神经元电路的输出端连接,所述电容器的第二端与所述参考电压端连接,所述衰减电路包括衰减电阻,所述衰减电阻的第一端与所述神经元电路的输出端连接,所述衰减电阻的第二端与所述参考电压端连接。

11.例如,在本公开至少一实施例提供的储备池计算装置中,所述每个前神经元转子电路为第一多路选择器,所述每个后神经元转子电路为第二多路选择器。

12.例如,在本公开至少一实施例提供的储备池计算装置中,所述时序控制电路包括:计数器,配置为在时钟信号控制下生成所述选通信号。

13.例如,在本公开至少一实施例提供的储备池计算装置中,所述输出层单元包括:乘加模块,配置为将多个所述第二处理结果与所述第二权重矩阵相乘得到所述第三处理结果。

14.例如,在本公开至少一实施例提供的储备池计算装置中,所述乘加模块包括忆阻器阵列,所述忆阻器阵列包括多个阵列排布的忆阻器,所述多个阵列排布的忆阻器的多个电导值与所述第二权重矩阵的多个元素的值对应。

15.例如,在本公开至少一实施例提供的储备池计算装置中,所述输出层单元还包括:参数设置模块,配置为设置所述忆阻器阵列的电导值。

16.例如,本公开至少一实施例提供一种数据处理方法,对应于上述储备池计算装置,包括:使用所述储备池计算装置进行推理计算操作;或者,使用所述储备池计算装置进行训练计算操作。

17.例如,在本公开至少一实施例提供的数据处理方法中,所述推理计算操作包括:通过所述信号输入电路接收用于所述推理计算操作的输入信号;通过所述储备池电路将所述输入信号与所述第一权重进行所述第一处理,得到所述第一处理结果,将所述第一处理结果进行所述第二处理以进行升维、非线性运算和递归连接,以得到多个第二处理结果;通过所述输出层单元将所述多个第二处理结果与所述第二权重矩阵相乘,得到所述第三处理结果,并将所述第三处理结果输出。

18.例如,在本公开至少一实施例提供的数据处理方法中,所述训练计算操作包括:通过所述信号输入电路接收用于所述训练计算操作的输入信号以及用于所述输入信号的标签值;通过所述储备池电路将所述输入信号与所述第一权重进行所述第一处理,得到所述第一处理结果,将所述第一处理结果进行所述第二处理以进行升维、非线性运算和递归连接,以得到多个第二处理结果;通过所述输出层单元将所述多个第二处理结果与所述第二权重矩阵相乘,得到所述第三处理结果;根据所述多个第三处理结果与所述训练输入信号的标签值计算所述第二权重矩阵的误差,以更新所述第二权重矩阵;将更新后的第二权重矩阵写入所述输出层单元。

附图说明

19.为了更清楚地说明本公开实施例的技术方案,下面将对实施例的附图作简单地介绍,显而易见地,下面描述中的附图仅仅涉及本公开的一些实施例,而非对本公开的限制。

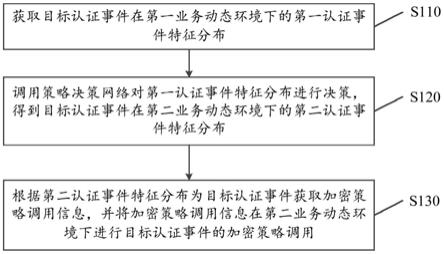

20.图1示出了一种储备池计算架构的示意图;

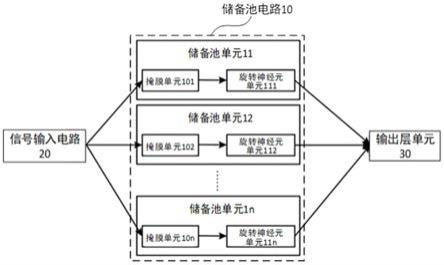

21.图2为本公开至少一实施例提供的一种储备池计算装置的示意图;

22.图3为本公开至少一实施例提供的一种储备池计算装置的掩膜单元的示意图;

23.图4a为本公开至少一实施例提供的一种储备池计算装置的旋转神经元单元的示意框图;

24.图4b为本公开至少一实施例提供的一种储备池计算装置的旋转神经元单元的示意图;

25.图5a为本公开至少一实施例提供的一种示例性的神经元电路的动态特性的示意图;

26.图5b为本公开至少一实施例提供的一种示例性的神经元电路的示意图;

27.图6为本公开至少一实施例提供的一种基于忆阻器阵列的输出层单元的示意图;

28.图7为本公开至少一实施例提供的一种数据处理方法的流程图;以及

29.图8为本公开至少一实施例提供的另一种数据处理方法的流程图。

具体实施方式

30.为使本公开实施例的目的、技术方案和优点更加清楚,下面将结合本公开实施例

的附图,对本公开实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本公开的一部分实施例,而不是全部的实施例。基于所描述的本公开的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本公开保护的范围。

31.除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。同样,“一个”、“一”或者“该”等类似词语也不表示数量限制,而是表示存在至少一个。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。

32.下面通过几个具体的实施例对本公开进行说明。为了保持本公开实施例的以下说明清楚且简明,可省略已知功能和已知部件的详细说明。当本公开实施例的任一部件在一个以上的附图中出现时,该部件在每个附图中由相同或类似的参考标号表示。

33.在rc算法得到充分发展的背景下,用硬件实现rc的方法在近十年来也得到了类脑计算领域的关注。软件实现的rc算法依赖于传统的冯诺依曼架构下的数据存储与处理。用硬件实现rc的思路依赖于一种能够高效挖掘元件的物理特性并且实现rc基本功能的架构。

34.例如,图1示出了一种储备池计算架构的示意图。该储备池计算架构由输入层、中间层和输出层三个部分组成。例如,输入层可以由一个或多个节点组成,属于前馈神经网络(feed-forward neural network,fnn)的一种;中间层由多个节点组成,属于rnn的一种;输出层可以为带有权重的加法器。具体地,储备池计算架构中的rc计算过程可以如公式(1)所示:

[0035][0036]

其中,i=1,

…

,n,x

in

表示输入层向中间层输入的输入信号,xi表示中间层向输出层输入的中间处理结果,y

out

表示输出层输出的输出信号,wi表示输出层的权重矩阵。

[0037]

在rc中,神经网络的输入层和中间层的连接由一个随机生成并且固定不变的矩阵定义,由这个矩阵对输入数据产生的复杂响应将该数据映射到高维并且线性可分的特征空间中。因此,训练一个rc网络只需要将输出层的高维状态矩阵进行线性回归即可实现rnn的一些功能,该特性大大简化了训练的复杂度和开销。

[0038]

作为一种rnn的实现方式,rc网络展现出了强大的时序信号处理能力。近年来,rc被广泛用于生物信号处理、混沌序列预测和模式识别等领域。

[0039]

由于分时复用和延迟反馈回路被引入到硬件rc的实现架构中,因此用硬件实现rc计算得到进一步的发展。对输入信号进行分时复用的操作减少了所需神经元的数量。此外,由于延迟反馈回路的存在使网络具备一定的记忆能力,该记忆能力是实现rc的关键。在上述基于延迟反馈和分时复用的rc架构中,多种电子元件、光学元件或者光电器件的物理特性被充分利用于机器学习相关的应用和实验中,并取得了良好的效果。

[0040]

现有的基于延迟反馈和分时复用的rc架构减小了硬件实现的开销,但仍然存在明显缺陷。首先,由于延迟反馈回路的构建还是存在着较大的开销和系统复杂度。例如,在电

路实现中,延迟信号一段时间还是需要数模转换模块和存储器;在光电rc系统中,该延迟线通常由一段几公里长的光纤实现。这些实现方式都存在着功耗或体积的问题,在缺少延迟反馈回路的情况下,rc系统的记忆能力和高维映射能力都讲大大减小或者丧失。其次,对输入信号的分时复用提升了系统的复杂度,带来了大量的串行操作。这些缺点阻碍了硬件rc系统的进一步发展和应用。在目前已有的rc系统中,除了关键的用于计算功能的物理器件外,往往需要大量的控制单元和数模转换来辅助系统的运行,又或者是体积庞大的光电系统,而一个理想的用rc实现的类脑计算单元应该是并行、低功耗而且实现方式简洁高效的。

[0041]

本公开至少一实施例提供一种储备池计算装置,该储备池计算装置包括信号输入电路、储备池电路和输出层单元。信号输入电路配置为接收输入信号。储备池电路包括多个储备池单元。每个储备池单元包括掩模单元和旋转神经元单元。掩模单元配置为接收输入信号且将输入信号使用第一权重进行第一处理,得到第一处理结果。旋转神经元单元配置为从掩模单元接收第一处理结果,且对第一处理结果进行第二处理以进行升维、非线性运算和递归连接,以得到第二处理结果。输出层单元配置为将多个储备池单元的多个第二处理结果与第二权重矩阵相乘,得到第三处理结果,并将第三处理结果输出。

[0042]

该储备池计算装置通过周期性地切换神经元电路阵列与输入输出电路的连接,取代了已有装置中的延迟反馈和分时复用的功能。该储备池计算装置不需要其它辅助电路即可实现完整的rc功能,优化了运行效率并降低了实现成本。

[0043]

本公开至少一实施例还提供了一种对应于上述储备池计算装置的数据处理方法,该数据处理方法包括推理计算或训练计算。

[0044]

下面结合附图对本公开的实施例进行详细说明,但是本公开并不限于这些具体的实施例。

[0045]

图2为本公开至少一实施例提供的一种储备池计算装置的示意图。

[0046]

例如,如图2所示,该储备池计算装置包括信号输入电路20、储备池电路10和输出层单元30。信号输入电路20配置为接收输入信号。储备池电路10包括多个储备池单元。每个储备池单元包括掩模单元和旋转神经元单元。掩模单元配置为接收输入信号且将输入信号使用第一权重进行第一处理,得到第一处理结果。旋转神经元单元配置为从掩模单元接收第一处理结果,且对第一处理结果进行第二处理以进行升维、非线性运算和递归连接,以得到第二处理结果。输出层单元30配置为将多个储备池单元的多个第二处理结果与第二权重矩阵相乘,得到第三处理结果,并将第三处理结果输出。

[0047]

例如,如图2所示,储备池电路10包括n个储备池单元,即储备池单元11~储备池单元1n,n为正整数,例如大于等于2。每个储备池单元包括掩膜单元和旋转神经元。信号输入电路20接收输入信号后,将该输入信号并行地输出到n个储备池单元中的n个掩膜单元,即掩膜单元101~掩膜单元10n。每个掩模单元接收输入信号后,将该输入信号使用第一权重进行第一处理,得到第一处理结果并输入到对应的旋转神经元。例如,该输入信号包括n个单元向量形式的输入信号1~n,输入信号1~n分别被输入到n个不同的储备池单元11~1n。对于同一个输入信号,将其并行地输入到配置为不同第一权重的多个掩膜单元中,可以提升状态的丰富度,从而提升网络的计算性能。

[0048]

例如,每个旋转神经元单元从对应的掩模单元接收多个第一处理结果后,旋转神经元单元将起到主要的计算作用。n个旋转神经元单元111~11n对多个第一处理结果进行

第二处理,以进行升维、非线性运算和递归连接这三种处理。经过n个旋转神经元单元111~11n的运算,得到多个第二处理结果,并将其并行地输入到输出层单元30中。

[0049]

例如,输出层单元30包括乘加模块;例如,该乘加模块通过存算一体阵列实现,例如忆阻器阵列。乘加模块中储存了已经训练好的第二权重矩阵。乘加模块配置为将旋转神经元单元输出的多个第二处理结果与第二权重矩阵相乘,得到第三处理结果,并将第三处理结果输出。乘加模块中的第二权重矩阵可以根据应用场景配置响应的目标值,以实现分类、预测和识别等功能。

[0050]

图3为本公开至少一实施例提供的一种储备池计算装置的掩膜单元的示意图。

[0051]

例如,如图3所示,在储备池电路10的第i个储备池单元1i中,掩模单元10i包括输入端10i1、输入权重配置模块10i2和输出端10i3,i为大于等于1小于等于n的正整数。输入端10i1配置为接收输入信号i。输入权重配置模块10i2配置为接收关于第一权重的控制信号。输入权重配置模块10i2对输入端10i1接收的输入信号i与第一权重进行第一处理,得到n个第一处理结果。n为正整数,例如大于等于2。输出端10i3配置为将输入权重配置模块10i2的n个第一处理结果输出,由此完成了输入信号的第一次升维处理。

[0052]

例如,如图3所示,输入权重配置模块10i2的一个示例包括反相器和n个开关s1、s2……

sn。每个开关包括第一开关输入端、第二开关输入端、开关输出端和开关控制端(图中未示出)。第一开关输入端与输入端10i1连接以接收输入信号i(该输入信号i通过图2中的信号输入电路20被输入到输入端10i1)。反相器与输入端10i1连接以接收输入信号i且将输入信号i反相得到反相输入信号i。第二开关输入端与反相器连接以接收反相输入信号i。开关输出端与输出端10i3连接。开关控制端配置为接收控制信号,将第一开关输入端或第二开关输入端接收的信号从开关输出端输出。

[0053]

例如,第一处理的具体过程为,输入权重配置模块10i2首先将输入信号i通过反相器分为正负两个值,然后再通过控制信号控制n个开关s1、s2……

sn分别选择输入每个神经元的为正值或负值,由此施加第一权重(这里权重值分别为随机分布的1和-1)。例如,输入信号i首先经过一个反相器产生一个与原信号幅值相同,极性相反的信号(相当于乘以权重

“‑

1”)。随后,将n个控制信号分别输入n个开关s1、s2……

sn的开关控制端,以选择每个开关的开关输出端输出的是正信号还是负信号,从而得到n个第一处理结果1~n。该过程对应于rc软件算法中的输入信号i与对应的第一权重相乘。

[0054]

例如,上述示例中,第一权重可以为由反相器和n个开关s1、s2……

sn实现的n个-1和1的随机分布,在其他示例中,第一权重也可以为由其他方式实现的n个0~1之间的随机数,或者可以为能实现信号升维分类处理的其他数值分布。

[0055]

例如,控制信号为随机控制信号,且n个开关s1、s2……

sn的开关控制端分别对每个开关单独控制。

[0056]

例如,输入信号可以为连续的模拟输入信号。例如,反相器可以为反向运算放大器电路。本公开的实施例对这些具体实现方式不作限制。

[0057]

需要说明的是,在储备池计算装置调试结束后或者运行的过程中,所有n个掩膜单元中控制第一权重的n组开关必须保持不变,以保证在使用的过程中对相似的输入信号产生相似的响应,以供下一级的旋转神经元单元处理。

[0058]

图4a为本公开至少一实施例提供的一种储备池计算装置的旋转神经元单元的示

意框图;图4b为本公开至少一实施例提供的一种储备池计算装置的旋转神经元单元的示例的示意图。

[0059]

例如,如图4a所示,在储备池电路10的第i个储备池单元1i中,旋转神经元单元11i包括n个前神经元转子电路11i1、n个神经元电路11i2、n个后神经元转子电路11i3和时序控制电路11i4(如图4b所示)。这里,n为正整数,例如大于等于2。

[0060]

例如,如图4b所示,在一个示例中,在第i个旋转神经元单元中,n个前神经元转子电路11i1包括神经元转子电路11i11~11i1n(标注为m1,m2,

…

,mn),n个神经元电路11i2包括神经元电路11i21~11i2n,n个后神经元转子电路11i3包括后神经元转子电路11i31~11i3n(标注为m1’

,m2’

,

…

,m

n’)。

[0061]

例如,每一个前神经元转子电路包括第一选通信号端、第一输入端以及排序为第1到第n的n个第一输出端(in1,in2,

…

,inn)。相邻的前神经元转子电路的n个第一输出端的顺序不同;例如,对于标注为m1的前神经元转子电路11i11的n个第一输出端分别为in1,inn,

…

,in2,对于标注为m2的前神经元转子电路11i12的n个第一输出端分别为in2,in1,

…

,inn,

…

,对于标注为mn的前神经元转子电路11i1n的n个第一输出端分别为inn,in

n-1

,

…

,in1。

[0062]

例如,如图4b所示,n个后神经元转子11i3与n个前神经元转子电路11i1一一对应;每一个后神经元转子电路包括第二选通信号端、排序为第1到第n的n个第二输入端(out1,out2,

…

,outn)以及第二输出端。相邻的后神经元转子电路的n个第二输入端的顺序不同;例如,对于标注为m1’

的后神经元转子电路11i31的n个第二输入端分别为out1,outn,

…

,out2,对于标注为m2’

的后神经元转子电路11i32的n个第二输入端分别为out2,out1,

…

,outn,

…

,对于标注为m

n’的后神经元转子电路11in的n个第二输入端分别为outn,out

n-1

,

…

,out1。

[0063]

例如,如图4b所示,神经元电路11i2m的第一端连接每个前神经元转子电路的第m个第一输出端inm,即n个前神经元转子电路11i11~11i1n的n个第一输出端inm彼此连通;神经元电路11i2m的第二端连接每个后神经元转子电路的第m个第二输入端outm,即n个后神经元转子电路11i21~11i2n的n个第一输出端outm彼此连通;这里m=1,2,

…

,n;因此,神经元电路11i2m同时与n个前神经元转子电路11i1的n个第一输出端inm连接,同时与n个后神经元转子电路11i3的n个第二输入端outm连接。

[0064]

例如,每个前神经元转子电路110可以为第一多路选择器,即n选一多路选择器,在n个第一输出端(in1,in2,

…

,inn)中选择一个与第一输入端连接;例如,每个后神经元转子电路130可以为第二多路选择器,即n选一多路选择器,在n个第二输入端(out1,out2,

…

,outn)中选择一个与第二输出端连接。

[0065]

例如,时序控制电路11i4包括计数器,配置为在时钟信号控制下生成选通信号。时序控制电路11i4与每一个前神经元转子电路的第一选通信号端连接,与每一个后神经元转子电路的第二选通信号端连接。由此将选通信号同时施加到n个前神经元转子电路11i1与n个后神经元转子电路11i3,即第一选通信号端和第二选通信号端接收同一个选通信号。

[0066]

需要说明的是,n个前神经元转子电路11i1的第一选通信号端和n个后神经元转子电路11i3的第二选通信号端可以接收同一个选通信号或不同的选通信号。

[0067]

例如,n个前神经元转子电路11i1整体上配置为,根据选通信号,每个前神经元转子电路选通自身的n个第一输出端(in1,in2,

…

,inn)中的一个,且n个前神经元转子电路

11i1所选通的第一输出端的序号彼此不同。n个后神经元转子电路11i3整体上配置为,根据选通信号,每个后神经元转子电路选通自身的n个第二输入端(out1,out2,

…

,outn)中的一个,且n个后神经元转子电路11i3所选通的第二输入端的序号彼此不同。与同一个神经元电路连接的前神经元转子电路的第一输出端和后神经元转子电路的第二输入端同时被选通,由此得到从第一输入端到第二输出端的通路。

[0068]

例如,选通信号的值随时间变化且使得在n个操作周期中:每个前神经元转子电路选通自身第1到第n个第一输出端(in1,in2,

…

,inn)被依序选通;每个后神经元转子电路选通自身第1到第n个第二输入端(out1,out2,

…

,outn)被依序选通。

[0069]

例如,如图4b所示,时序控制电路11i4可以包括一个计数器,例如该计数器为log2n位计数器,以用于定时输出例如递增的数值信号。每个前神经元转子电路110可以为n选一的第一多路选择器(m1,m2,

…

,mn),n个第一多路选择器(m1,m2,

…

,mn)的第一选通信号端都连接在计数器的输出端。每个后神经元转子电路130可以为n选一的第二多路选择器(m1’

,m2’

,

…

,m

n’),n个第二多路选择器(m1’

,m2’

,

…

,m

n’)的第二选通信号端也都连接在该计数器的输出端。当该计数器的输入端接收到一个特定频率的驱动脉冲信号时,计数器同时向第一选通信号端和第二选通信号端输出选通信号,n个前神经元转子电路11i1第一多路选择器的第一输出端(in1,in2,

…

,inn)与n个后神经元转子电路11i3的第二多路选择器的n个第二输入端(out1,out2,

…

,outn)依次被选通。

[0070]

例如,在某一个(第1个)时刻,时序控制电路11i4向第一选通信号端和第二选通信号端输出一个选通信号,该选通信号用于选择第一多路选择器中预定序号的第一输出端,以及用于选择第二多路选择器中同一预定序号的第二输入端。

[0071]

例如,在这一时刻,选通信号用于选择图4b中的第一多路选择器中第1个第一输出端和第二多路选择器中第1个第二输入端,那么第一多路选择器m1的第一输出端in1被选通,而第一多路选择器m2的第一输出端in2被选通,第一多路选择器m3的第一输出端in3被选通

……

;对应地,第二多路选择器m1’

的第二输入端out1被选通,而第二多路选择器m2’

的第二输入端out2被选通,第二多路选择器m3’

的第二输入端out3被选通

……

。

[0072]

在这种情况下,神经元电路1由于与所有的第一多路选择器的第一输出端in1连接,且与所有的第二多路选择器的第二输入端out1连接,由此得到从第一多路选择器m1的第一输入端、第一多路选择器m1的第一输出端in1、神经元电路1、第二多路选择器m1’

的第二输入端out1、第二多路选择器m1’

的第二输出端的通路;同样地,神经元电路j由于与所有的第一多路选择器的第一输出端inj连接,且与所有的第二多路选择器的第二输入端outj连接,由此得到从第一多路选择器mj的第一输入端、第一多路选择器mj的第一输出端in1、神经元电路j、第二多路选择器m

j’的第二输入端outj、第二多路选择器m

j’的第二输出端的通路。这里,j大于1小于等于n。

[0073]

例如,在下一个(第2个)时刻,选通信号用于选择图4b中的第一多路选择器中第2个第一输出端和第二多路选择器中第2个第二输入端,那么第一多路选择器m1的第一输出端inn被选通,而第一多路选择器m2的第一输出端in1被选通,第一多路选择器m3的第一输出端in2被选通

……

;对应地,第二多路选择器m1’

的第二输入端outn被选通,而第二多路选择器m2’

的第二输入端out1被选通,第二多路选择器m3’

的第二输入端out2被选通

……

。

[0074]

在这种情况下,神经元电路1由于与所有的第一多路选择器的第一输出端in1连

的效果,并实现了信号的升维处理。该电路切换的过程与软件算法中的环形rc的矩阵乘法等效。

[0082]

图5a为本公开至少一实施例提供的一种示例性的神经元电路的动态特性的示意图,图5b为本公开至少一实施例提供的一种示例性的神经元电路的示意图。

[0083]

例如,如图5a所示,每一个神经元电路(以图4b中的神经元电路11i2m为例)包括非线性激活电路im1、积分电路im2以及衰减电路im3。非线性激活电路im1的第一端与神经元电路11i2m的输入端im01连接,非线性激活电路im1的第二端与神经元电路11i2m的输出端im02连接;积分电路im2的第一端与神经元电路11i2m的输出端im02连接,衰减电路im3的第一端与神经元电路11i2m的输入端im01连接,积分电路im2的第二端与衰减电路im3的第二端连接。

[0084]

例如,如图5a所示,非线性激活电路im1可以对应一个非线性函数f,积分电路im2可以对应积分z-1

,衰减电路im3可以对应积分的过程中的衰减d。第一处理结果m从输入端im01输入到神经元电路11i2m后,非线性激活电路im1对第一处理结果m通过非线性函数f进行非线性处理;同时,衰减电路im3对第一处理结果m进行衰减d,积分电路im2对衰减后的第一处理结果进行积分z-1

处理,最终得到非线性和递归处理后的第二处理结果m并从输出端im02输出。

[0085]

例如,如图5b所示,在一个示例中,非线性激活电路im1包括二极管d

relu

,二极管d

relu

的负极与输出端im02连接,二极管d

relu

的正极与参考电压端v

ref

连接。积分电路im2包括积分电阻r

int

和电容器c

int

,积分电阻r

int

的第一端与输入端im01连接,积分电阻r

int

的第二端与电容器c

int

的第一端以及输出端im02连接,电容器c

int

的第二端与参考电压端v

ref

连接。衰减电路im3包括衰减电阻r

leakage

,衰减电阻r

leakage

的第一端与输出端im02连接,衰减电阻r

leakage

的第二端与参考电压端v

ref

连接。例如,在如图5b所示的电路中,非线性方程f由二极管d

relu

提供,积分z-1

由r

int

和c

int

提供,衰减d由电阻r

leakage

提供。电阻r

leakage

的阻值大于积分电阻r

int

的阻值。

[0086]

需要说明的是,非线性激活电路im1也可以包括其他能够提供非线性处理功能的元器件;积分电路im2也可以包括其他能够提供积分处理功能的元器件;衰减电路im3也可以包括其他能够提供衰减处理功能的元器件。本公开的实施例对这些电路的具体构成不作限制。

[0087]

例如,在上述实施例提供的神经元电路中,由于积分电路对过去时刻输入的第一处理结果的积分作用,神经元电路每一时刻输出的第二处理结果包含了当前时刻的第一处理结果的信息和过去时刻的第一处理结果的信息。因此,利用神经元电路本身的记忆特性可以保持过去时刻的输入信息,使得该储备池计算装置在模拟计算过程中不需要额外的存储器,从而优化了运行效率并降低了实现成本。

[0088]

图6为本公开至少一实施例提供的一种基于忆阻器阵列的输出层单元30的示意图。

[0089]

例如,如图6所示,输出层单元30包括乘加模块和参数设置模块(图中未示出)。乘加模块包括存算一体阵列,该存算一体阵列可以包括忆阻器阵列,配置为将多个第二处理结果与第二权重矩阵相乘得到第三处理结果。参数设置模块配置为用于设置忆阻器阵列的电导值。

[0090]

例如,乘加模块的忆阻器阵列包括多个阵列排布的忆阻器。多个阵列排布的忆阻器的多个电导值与第二权重矩阵的多个元素的值对应。

[0091]

例如,如图6所示,该忆阻器阵列由多个忆阻器单元构成,多个忆阻器单元构成一个m行r列的阵列,m和r均为正整数。每个忆阻器单元包括开关元件(例如,晶体管)和一个或多个忆阻器。在图6中,bl《1》、bl《2》

……

bl《r》分别表示第一列、第二列

……

第r列的位线,每一列的忆阻器单元中的忆阻器和该列对应的位线连接;sl《1》、sl《2》

……

sl《m》分别表示第一行、第二行

……

第m行的源线,每一行的忆阻器单元中的开关元件的源极(例如,晶体管的源极)和该行对应的源线连接;此外,每一行的忆阻器单元中的开关元件的控制极(例如晶体管的栅极)和该行对应的字线连接(图中未示出)。根据基尔霍夫定律,通过设置忆阻器单元的状态(例如,电阻值或电导值)并且在字线与位线施加相应的字线信号与位线信号,上述忆阻器阵列可以并行地完成乘积累加计算。

[0092]

例如,每个旋转神经元单元输出n个第二处理结果,则n个储备池单元中的n个旋转神经元单元共输出n

×

n个第二处理结果,即r=n

×

n。

[0093]

例如,r个第二处理结果为电压输出(v1、v2……vr

),可直接作为高维特征向量用于输出层单元30的乘加。例如,m行r列排布的忆阻器的多个电导值g

t

=[g

11

,g

12

…g1r

;g

21

,g

22

…g2r

;

…

;g

m1

,g

m2

…gmr

]与第二权重矩阵的多个元素的值对应。m行r列排布的忆阻器的多个电导值由参数设置模块设置。

[0094]

例如,在位线bl《1》、bl《2》

……

bl《r》上输入r个第二处理结果(例如,输入电压向量v

t

=[v1,v2,

…

,vr]),r个第二处理结果与m行r列的第二权重矩阵(例如,电导矩阵g

t

)相乘得到m个第三处理结果(例如,输出电流向量i

t

=[i1,i2,

…

,im]),并在源线sl《1》、sl《2》

……

sl《m》上输出m个第三处理结果。例如,具体计算过程如公式(2)所示。

[0095][0096]

例如,对于如图2所示的储备池计算装置,该储备池计算装置的n个储备池单元输出r(r=n

×

n)个第二处理结果到如图6所示的输出层单元30,在输出层单元30中将r个第二处理结果与第二权重矩阵相乘,最终输出n

×

m个第三处理结果。

[0097]

例如,图6的忆阻器阵列中的忆阻器单元例如可以具有1t1r结构或者2t2r结构,其中,1t1r结构的忆阻器单元包括一个晶体管和一个忆阻器,2t2r结构的忆阻器单元包括两个晶体管和两个忆阻器。该忆阻器阵列还可以进一步包括用于各个晶体管的字线(图中未示出),每条字线用于控制例如一行忆阻器单元中的晶体管的导通或截止。例如,忆阻器为非挥发性忆阻器,包括但不限于rram、pcram、ecram、闪存(flash)等。本公开对忆阻器单元的结构不作限制,也可以采用可以实现乘积累加运算的其他结构形式的忆阻器单元。

[0098]

需要说明的是,本公开的实施例中采用的晶体管均可以为薄膜晶体管或场效应晶体管(例如mos场效应晶体管)或其他特性相同的开关器件。这里采用的晶体管的源极、漏极在结构上可以是对称的,所以其源极、漏极在结构上可以是没有区别的。

[0099]

上述实施例提供的储备池计算装置将非易失性忆阻器阵列应用于输出层单元实现了高效乘加。在上述装置中,元器件的物理特性被充分挖掘用于rc计算,在误差可接受范

围内,降低了系统成本和运行功耗。

[0100]

图7为本公开至少一实施例提供的一种数据处理方法的流程图;图8为本公开至少一实施例提供的另一种数据处理方法的流程图。

[0101]

例如,用于上述储备池计算装置的数据处理方法包括推理计算操作或训练计算操作。推理计算操作中的第一权重矩阵和第二权重矩阵可以为在训练计算操作中根据应用场景训练得到的目标值,以实现对输入信号的分类、预测、识别等功能。

[0102]

例如,如图7所示,在一个示例中,推理计算操作包括以下步骤s101-s103。

[0103]

步骤s101:通过信号输入电路20接收用于推理计算操作的输入信号。

[0104]

步骤s102:通过储备池电路10将输入信号与第一权重进行第一处理,得到第一处理结果,将第一处理结果进行第二处理以进行升维、非线性运算和递归连接,以得到多个第二处理结果;

[0105]

步骤s103:通过输出层单元30将多个第二处理结果与第二权重矩阵相乘,得到第三处理结果,并将第三处理结果输出。

[0106]

例如,如图7所示,在图2所示的储备池计算装置中进行推理计算操作时,首先通过信号输入电路20接收输入信号。然后,信号输入电路20将输入信号输入到n个例如图3中掩膜单元101~10n的输入端1011~10n1(例如,该输入信号包括n个单元向量形式的输入信号1~n,输入信号1~n分别输入n个不同的储备池单元11~1n)。在掩膜单元10i中,将输入信号i与输入权重配置模块10i2对应的第一权重进行第一处理,得到n个第一处理结果1~n。随后,掩模单元10i输出n个第一处理结果1~n到例如图4b所示的旋转神经元单元11i,同时向时序控制电路11i4输入与神经元电路的时间常数和时序信号相匹配的脉冲频率,将n个第一处理结果1~n在旋转神经元单元11i中进行第二处理以进行升维、非线性运算和递归连接,在每个时刻得到n个第二处理结果1~n。最后,例如图6所示的输出层单元30采集n个旋转神经元单元111~11n的r(r=n

×

n)个第二处理结果,将该r个第二处理结果经输出层单元30进行处理,例如与映射于忆阻器阵列中的第二权重矩阵相乘,得到n

×

m个第三处理结果,并将n

×

m个第三处理结果输出,用于后续处理。

[0107]

例如,如图8所示,在一个示例中,训练计算操作包括以下步骤s201-s205。

[0108]

步骤s201:通过信号输入电路20接收用于训练计算操作的输入信号以及用于输入信号的标签值。

[0109]

步骤s202:通过所述储备池电路10将输入信号与第一权重进行第一处理,得到第一处理结果,将第一处理结果进行第二处理以进行升维、非线性运算和递归连接,以得到多个第二处理结果。

[0110]

步骤s203:通过输出层单元30将多个第二处理结果与第二权重矩阵相乘,得到第三处理结果。

[0111]

步骤s204:根据多个第三处理结果与训练输入信号的标签值计算第二权重矩阵的误差,以更新第二权重矩阵。

[0112]

步骤s205:将更新后的第二权重矩阵写入输出层单元30。

[0113]

例如,如图8所示,在图2所示的储备池计算装置中进行训练计算操作时,首先通过信号输入电路20接收输入信号以及对应于输入信号的标签值。然后,信号输入电路20将输入信号输入到n个例如图3中掩膜单元101~10n的输入端1011~10n1(例如,该输入信号包

括n个单元向量形式的输入信号1~n,输入信号1~n分别输入n个不同的储备池单元11~1n)。在掩膜单元10i中,将输入信号i与输入权重配置模块10i2对应的第一权重进行第一处理,得到n个第一处理结果1~n。随后,掩模单元10i输出n个第一处理结果1~n到例如图4b所示的旋转神经元单元11i,同时向时序控制电路11i4输入与神经元电路的时间常数和时序信号相匹配的脉冲频率,将n个第一处理结果1~n在旋转神经元单元11i中进行第二处理以进行升维、非线性运算和递归连接,在每个时刻得到n个第二处理结果1~n。然后,例如图6所示的输出层单元30采集n个旋转神经元单元111~11n的r(r=n

×

n)个第二处理结果,将该r个第二处理结果经输出层单元30进行处理,例如与映射于忆阻器阵列中的第二权重矩阵相乘,得到n

×

m个第三处理结果。随后,根据n

×

m个第三处理结果与训练输入信号的标签值计算第二权重矩阵的误差,例如使用该误差计算损失值,使用该损失值进行反向传播,以更新第二权重矩阵;最后,将更新后的第二权重矩阵写入例如图6所示的输出层单元30中,例如,重新设置作为存算一体阵列的忆阻器阵列中各个忆阻器单元的电导值。

[0114]

例如,在步骤s204中,可以采用线性回归等算法更新第二权重矩阵,本公开的实施例对此不作限制。在训练过程中,可以将各个时刻储备池电路10输出的r个第二处理结果作为线性回归算法中的变量,再设置期望的第三处理结果作为线性回归算法的目标值,从而计算出一组第二权重矩阵。图6中的参数设置模块根据训练得到的第二权重矩阵来设置忆阻器阵列中m行r列忆阻器的电导值。

[0115]

对于本公开,有以下几点需要说明:

[0116]

(1)本公开实施例附图中,只涉及到与本公开实施例涉及到的结构,其他结构可参考通常设计。

[0117]

(2)在不冲突的情况下,本公开同一实施例及不同实施例中的特征可以相互组合。

[0118]

以上,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。