一种fpga并行仿真的海量仿真波形数据切片方法

技术领域

1.本发明涉及计算机程序数据处理技术领域,具体而言,涉及一种fpga并行仿真的海量仿真波形数据切片方法。

背景技术:

2.现有技术中,fpga(field programmable gate array,现场可编辑逻辑门阵列)仿真的仿真波形通常采用vcd格式(value change dump,它是ieee1364标准(verilog hdl语言标准)中定义的一种ascii文件,是一种通用的文件格式)进行记录,vcd格式文件是ieee1364标准(verilog hdl语言标准)中定义的一种ascii文件(ascii file文件,指含有用标准ascii字符集编码的字符的数据和文本文件),其记录了信号的完整变化信息,可以用vcd格式文件来再现仿真。因为vcd格式是verilog hdl语言标准的一部分,因此所有的verilog的仿真器都能够查看vcd格式文件。vcd格式文件通常由三部分组成:头信息区、节点信息区及数值变化区,其中头信息区包括vcd产生日期、仿真器版本以及仿真时间精度等信息;节点信息区主要记录了哪些变量信号将被记录在vcd中以及在vcd中对应这些变量信号的标识符;数值变化区主要记录那些随着仿真时间推移发生变化的变量信号。一般而言,vcd仅记录信号的变化,因此需要创建检查点,在检查点记录所有要被记录的信号以为基准,vcd数值变化区起始位置默认会创建检查点记录所有要被记录的信号之初始值。再现仿真需从检查点开始顺序解析还原波形数据,而无法随机访问以获得仿真波形数据。

3.fpga并行仿真时,将用户设计划分成子设计分布到多块fpga上运行,在每块fpga都将配备ddr(double data rate sdram,双倍速率sdram)内存,仿真波形数据先缓存在几十上百块fpga标配的ddr内存中,待仿真完成后利用全局时钟时间戳校准合并重整后转存为vcd格式仿真波形文件保存在服务端,用户需通过网络下载至本地显示及分析处理。

4.fpga并行仿真将产生海量仿真波形数据,按业界通行做法,仿真需记录至少1ms内(通常间隔为1ns)信号的变化,哪怕带宽一位的信号所记录二进制数据量就达1m位以上,而一次仿真往往需观察数千位信号波形,记录的vcd仿真波形文件多达几十gb,而且大规模fpga并行仿真时,仿真波形文件存储在服务端,访问速度受制于网络带宽,超大型仿真波形文件的分析处理及显示的主要问题在于时延,当前主流仿真器/仿真波形工具处理此类仿真波形文件数据都需要等待几十分钟至数小时不等,其原因在于网络速度瓶颈及cpu性能瓶颈,无论是下载还是顺序解析超大型仿真波形文件都需要大量时间。

5.鉴于此,研究一种降低时延以提高调试效率的fpga并行仿真的海量仿真波形数据切片方法是本领域技术人员亟需解决的技术问题。

技术实现要素:

6.鉴于此,本发明提出了一种fpga并行仿真的海量仿真波形数据切片方法,以克服当前仿真波形文件访问速度和分析处理时延的问题,该方法能够降低还原仿真波形的时延,有效提高了调试效率。

7.本发明提出的fpga并行仿真的海量仿真波形数据切片方法,包括:

8.s1、设置仿真波形切分信息并导入fpga项目,将导入的fpga项目划分为多个独立子模块并逐一生成fpga位流,然后将所生成的fpga位流分别下载至全局时钟信号同步的fpga上并行仿真,其中仿真波形切分信息包括rlm划分、时间轴切分粒度和仿真文件保存路径;

9.s2、选择需要调试的调试信号并设置调试信号触发条件,将仿真过程中调试信号产生的仿真波形数据添加全局时钟时间戳后缓存至ddr内存中;

10.s3、利用仿真波形切分模块访问步骤s2中所缓存的仿真波形数据,基于全局时钟时间戳对所访问的仿真波形数据进行校准、合并和重整并生成索引文件,然后将仿真波形数据转存的vcd仿真波形切片文件与索引文件一起保存至步骤s1中配置的仿真文件保存路径并提供网络文件访问服务;

11.s4、利用仿真波形显示模块下载索引文件,并通过解析索引文件得到调试信号列表;

12.s5、基于步骤s4中所得到的调试信号列表选择需要还原的调试信号和/或时间点,并利用仿真波形显示模块将相应的vcd仿真波形切片文件加载至ddr内存中以还原出仿真波形。

13.上述的fpga并行仿真的海量仿真波形数据切片方法,可选的,所述步骤s1中rlm划分是基于调试信号之间的功能关系紧密程度进行划分。

14.上述的fpga并行仿真的海量仿真波形数据切片方法,可选的,所述步骤s3中生成的索引文件为ascii文件,其包括头信息区、节点信息区和节点url映射区。

15.上述的fpga并行仿真的海量仿真波形数据切片方法,可选的,所述步骤s3中仿真波形数据转存为vcd仿真波形切片文件具体实现方式为:按照时间轴切分粒度和索引文件中信号url映射表将仿真波形数据转存为vcd仿真波形切片文件。

16.上述的fpga并行仿真的海量仿真波形数据切片方法,可选的,所述步骤s3中将仿真波形数据转存的vcd仿真波形切片文件与索引文件一起保存至步骤s1中配置的仿真文件保存路径的具体步骤包括:

17.s31、根据调试信号的信息查询索引文件,进而生成该调试信号所归属rlm仿真波形切片文件名称,其中rlm仿真波形切片文件名称表示为:rlm仿真波形切片文件名称仿真波形切片序号.vcd,仿真波形切片序号的计算公式表示为:

[0018][0019]

式(1)中,[]表示取整;

[0020]

s32、基于步骤s31中生成的仿真波形切片文件名称即可得到vcd仿真波形切片文件,将vcd仿真波形切片文件与索引文件一起保存至步骤s1中配置的仿真文件保存路径。

[0021]

上述的fpga并行仿真的海量仿真波形数据切片方法,可选的,所述步骤s3中的将仿真波形数据转存为vcd仿真波形切片文件时需要在数值变化区起始位置创建检查点,进而记录该时刻rlm仿真波形切片文件的所有信号的当前值。

[0022]

上述的fpga并行仿真的海量仿真波形数据切片方法,可选的,所述步骤s5中利用仿真模型显示模块将相应vcd仿真波形切片文件加载至ddr内存中即可还原出仿真波形的

具体步骤包括:

[0023]

s51、利用仿真模型显示模块在本地缓存中查找是否存在相应的vcd仿真波形切片文件,若存在则直接加载至ddr内存中以还原出仿真波形,若不存在,则进入步骤s52;

[0024]

s52、通过文件共享模块将相应的vcd仿真波形切片文件下载至本地,然后将下载的vcd仿真波形切片文件加载至ddr内存中即可还原出仿真波形。

[0025]

上述的fpga并行仿真的海量仿真波形数据切片方法,可选的,所述仿真模型显示模块通过异步线程对vcd仿真波形切片文件进行下载和/或加载,进而能够充分利用cpu多核优势以降低时延。

[0026]

本发明所提出的一种fpga并行仿真的海量仿真波形数据切片方法,该切片方法根据fpga并行仿真还原仿真波形对调试信号及时间点高度集中的特点,基于调试信号的功能模块及时间轴将包含海量仿真数据的超大型仿真波形文件切分为大量微型文件,并通过创建索引将大量微型文件组织起来,该方法聚焦于调试所需信号及时段,能够滤除大量冗余数据,进而降低了对网络带宽及cpu处理速度的要求,使得利用cpu多核优势并行下载和/或解析vcd仿真波形切分文件成为可行,从而降低了还原仿真波形的时延,大幅提高了调试效率。

附图说明

[0027]

此处所说明的附图仅仅用来提供对本发明的进一步解释,构成被申请的一部分,并不构成对本发明的限定。在附图中:

[0028]

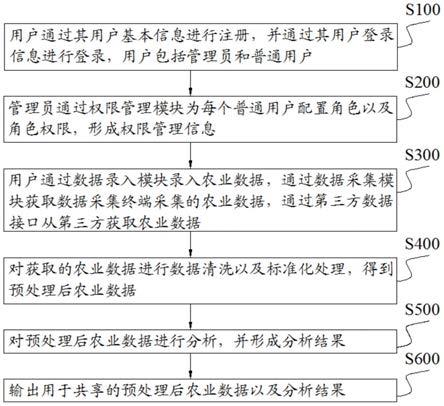

图1为本发明中一种fpga并行仿真的海量仿真波形数据切片方法的流程图,

[0029]

图2为本发明中仿真波形切片文件加载至ddr内存中的方法流程图。

具体实施方式

[0030]

为了能够更清楚地理解本发明的上述目的、特征和优点,下面结合附图和具体实施方式对本发明进行进一步的详细描述。需要说明的是,在不冲突的情况下,本技术的实施例及实施例中的特征可以相互组合。

[0031]

具体地,本发明具体实施例提出的一种fpga并行仿真的海量仿真波形数据切片方法,如图1所示,包括如下步骤:

[0032]

s1、设置仿真波形切分信息并导入fpga项目(fpga项目是指verilog源代码、使用的ip核、网表及约束,其用于描述硬件电路以生成fpga位流),将导入的fpga项目划分为多个独立子模块并逐一生成fpga位流,然后将所生成的fpga位流分别下载至全局时钟信号同步的fpga上并行仿真,其中,仿真波形切分信息包括rlm(rlm是提出的接收者驱动的分层多播算法)划分、时间轴切分粒度和仿真文件保存路径,rlm划分是基于调试信号之间的功能关系紧密程度进行划分,rlm划分具体如下:

[0033]

rlm划分中的fpga项目是以top module(顶层模块)为根节点的实例树,实例树中的每个节点对应一个module的实例,每个节点对应子树代表该子树下所有节点由该节点对应module的实例所实例化,根节点对应的是top module本身,初始时默认所有module实例归属于rlm0,本实施例中,给出rlm最顶层的module实例节点表示将此节点对应子树下所有节点划分到某个rlm,rlm划分示例如下://rlm序号rlm名称rlm的顶层module实例路径

[0034]

rlm 0top top_tb

[0035]

rlm 1u_dut1 top_tb|u_dut1

[0036]

rlm 2u_dut2 top_tb|u_dut2;

[0037]

基于rlm划分调试信号在调试功能时,只需下载相应rlm对应仿真波形文件而无须下载全部调试信号的仿真波形文件,基于时间轴切分粒度切分仿真波形文件,将调试信号仿真波形数据按给定时间轴切分粒度分时段保存,切分后尽管vcd仿真波形切片文件仍无法按仿真精度随机访问,但是可以根据关注的仿真时刻定位到对应时段保存的仿真波形数据切片文件,能够实现按需访问,大幅降低时延;

[0038]

s2、选择需要调试的调试信号并设置调试信号触发条件,将仿真过程中调试信号产生的仿真波形数据添加全局时钟时间戳后缓存至ddr内存中,该ddr内存是fpga标配的ddr内存;

[0039]

s3、利用仿真波形切分模块访问步骤s2中所缓存的仿真波形数据,基于全局时钟时间戳对所访问的仿真波形数据进行校准、合并和重整并生成索引文件,然后将仿真波形数据转存的vcd仿真波形切片文件与索引文件一起保存至步骤s1中配置的仿真文件保存路径并提供网络文件访问服务(由于仿真波形数据的文件很大,因此,本发明采用仿真波形切分模块对仿真波形数据进行预处理以便于后续的信息检索,同时利用仿真波形切分模块生成索引文件以及将仿真波形数据转存为vcd仿真波形切片文件),其中,所述仿真波形数据按照时间轴切分粒度和索引文件中信号url(uniform resource locator,统一资源定位器)映射表转存为vcd仿真波形切片文件,索引文件为ascii文件,其包括头信息区、节点信息区和节点url映射区,该索引文件对应的头信息区和节点信息区应该与vcd仿真波形文件中的信息区及节点信息区兼容,索引文件示例如下:

[0040]

[0041][0042]

索引文件中的时间轴切分粒度来自步骤s1中仿真波形切分信息配置中时间轴切分粒度,仿真持续时间来自全局时钟计数,信号url映射表中project目录来自步骤s1配置的仿真文件保存路径,标识符根据步骤s2中所选择的调试信号按照ieee-1364标准生成,rlm名称根据调试信号的module层级结构查询rlm划分表得到;

[0043]

s4、利用仿真波形显示模块下载索引文件,并通过解析索引文件得到调试信号列表;

[0044]

s5、基于步骤s4中所得到的调试信号列表选择需要还原的调试信号和/或时间点,并利用仿真波形显示模块将相应的vcd仿真波形切片文件加载至ddr内存中即可还原出仿真波形。

[0045]

本实施例中,所述仿真显示模块和仿真波形切分模块均为本领域的常规技术,只要具备本实施例中所相应的功能均可,此处不再赘述。所述切片方法根据fpga并行仿真还原仿真波形对调试信号及时间点高度集中的特点,基于调试信号的功能模块及时间轴将包含海量仿真数据的超大型仿真波形文件切分为大量微型文件,并通过创建索引将大量微型文件组织起来,该方法聚焦于调试所需信号及时段,能够滤除大量冗余数据,进而降低了对网络带宽及cpu处理速度的要求,使得利用cpu多核优势并行下载和/或解析vcd仿真波形切分文件成为可行,从而降低了还原仿真波形的时延,大幅提高了调试效率。

[0046]

如图2所示,所述步骤s3中将仿真波形数据转存的vcd仿真波形文件与索引文件一起保存至步骤s1中配置的仿真文件保存路径的具体步骤包括:

[0047]

s31、根据调试信号的信息查询索引文件,进而生成该调试信号所归属的rlm仿真波形切片文件名称,其中rlm仿真波形切片文件名称表示为:rlm仿真波形切片文件名称仿真波形切片序号.vcd,仿真波形切片序号的计算公式表示为:

[0048][0049]

式(1)中,[]表示取整;

[0050]

s32、基于步骤s31中生成的rlm仿真波形切片文件名称即可得到vcd仿真波形切片文件,将vcd仿真波形切片文件与索引文件一起保存至步骤s1中配置的仿真文件保存路径。

[0051]

本实施例中,所述调试信号的信息是指调试信号在索引文件中的编号,索引文件包含信号url影射表,其中包括了归属rlm仿真波形切片文件名称,具体如下:

[0052]

$url//信号url映射表,格式:标识符project目录/rlm名称

[0053]

!/home/ubisectech/project/rlm1

[0054]

调试信号在索引文件中的编号为符号!,归属rlm仿真波形切片文件名称为rlm1,存储路径/home/ubisectech/project/。

[0055]

其中,所述步骤s3中的将仿真波形数据转存为vcd仿真波形切片文件时需要在数值变化区起始位置创建检查点,进而记录该时刻rlm仿真波形切片文件的所有信号的当前值。由于vcd仿真波形切片文件一般在信号发生改变时才会记录该信号当前值,在切片的初始时间点rlm内信号不一定都有记录,通过在数值变化区起始位置创建检查点记录该时刻rlm仿真波形切片文件的所有信号的当前值,能够有效避免访问某个vcd仿真波形切片文件时需要向前追溯该vcd仿真波形切片文件。

[0056]

其中,所述步骤s5中利用仿真模型显示模块将相应vcd仿真波形切片文件加载至ddr内存中以还原出仿真波形的具体步骤包括:

[0057]

s51、利用仿真模型显示模块在本地缓存中查找是否存在相应的vcd仿真波形切片文件,若存在则直接加载至ddr内存中以还原出仿真波形,若不存在,则进入步骤s52;

[0058]

s52、通过文件共享模块将相应的vcd仿真波形切片文件下载至本地,然后将下载的vcd仿真波形切片文件加载至ddr内存中即可还原出仿真波形。

[0059]

其中,所述仿真模型显示模块通过异步线程对vcd仿真波形切片文件进行下载和/

或加载,进而能够充分利用cpu多核优势以降低时延。

[0060]

本实施例中,由于初始时,仿真波形索引文件以及vcd仿真波形切片文件在本地没有缓存,因此,所述仿真波形显示模块需要利用文件共享模块将仿真波形索引文件以及vcd仿真波形切片文件下载至本地后再加载到ddr内存中,同时通过异步线程对vcd仿真波形切片文件进行下载和/或加载,能够充分利用cpu多核优势,进一步降低时延,提高调试效率。

[0061]

以上仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。