极低耗可重构波形紧凑型uwb发射器

技术领域

1.本发明涉及超宽带(ultra-wideband)或uwb脉冲生成领域,特别是使用低阻抗rf天线的uwb发射器的领域,它在连接对象的定位领域、uwb雷达领域以及在符合ieee 802.15.4-2011标准的通信系统中有特别的应用。

背景技术:

2.uwb信号被应用于大量的应用中,无论是定位还是通信需求。这些信号的频谱必须符合美国联邦通信委员会(fcc)和欧洲电信标准协会(etsi)颁布的频谱掩码,以免干扰已在使用的频谱带。ieee 802.15.4-2011标准,涉及使用uwb信号的lr wpan(low rate wireless personal area network,低速率无线个域网)类型网络,规定了在3.1ghz-10.6ghz频段中的几个600mhz和1300mhz宽的通信信道,并具有相关的频谱掩码。uwb信号由uwb脉冲组成。在下面的描述中,术语uwb脉冲将表示具有包络函数的rf周期序列,使得其符合前述频谱掩码。

3.uwb发射器应采用可重构的架构,以便能够适应所考虑的不同的应用,特别是不同的信道、不同的带宽、不同的数据调制类型、不同的发射电平、不同的频谱掩码。

4.此外,uwb发射器通常是用来配备连接的对象,这些对象在架构上只有很低的能量自主性(小型电池),这些对象的广泛存在也有利于减少它们的能量消耗,从而限制它们在环境中的足迹。

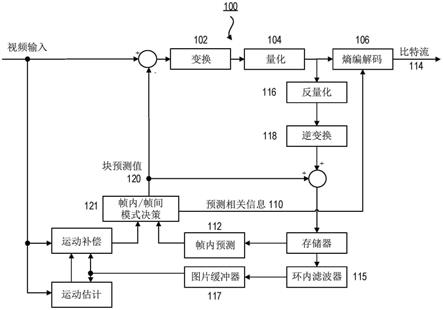

5.现有技术中已知的不同类型的uwb发射器符合如图1所示的一般架构100。

6.根据该一般架构,uwb发射器包括用于使由模块110指定的rf时钟和脉冲的包络成形的模块。该模块用于从相同频率的时钟信号,在uwb信号的中心频率f0处生成rf信号,以使脉冲成形,使其具有所需的包络。此外,当必须执行调制(通常是全调制或无调制、ook(on off keying,开关键控)或极性调制、bpsk(二进制相移键控))时,模块110可以应用该调制以获得调制的uwb脉冲。

7.然后,模块110输出端的uwb脉冲由功率放大模块120放大,之后由天线发射。由于天线阻抗小,功率放大级是必要的。

8.可以区分出两大类uwb发射器:使用存储元件和延迟线以数字方式生成脉冲的发射器和使用“h”桥以模拟方式生成脉冲的发射器。

9.在本技术人的专利us-b-8179945中描述了属于第一类发射器的一个示例。待生成的脉冲以存储在存储器中的数字样本序列的形式表示并以中心频率f0依次读取。之后,通过允许调节增益的数字缓冲器的测温并行来进行放大。

10.尽管如此,这样的发射器消耗能量,以至于使脉冲在中心频率上一个接一个的交替形成。

11.此外,尽管数字生成本身是可再现的,但存在于组合级和放大级中的寄生电容使波形失真,因此,所传输的uwb信号的频谱是相对不可预测的。此外,数字缓冲器产生大的电流冲击,这导致电源电位和地面的寄生变化,并使发射信号的频谱变得更难控制。

12.前述第二类uwb发射器使用如图2所示的“h”桥架构。

13.该h桥包括两个并联支路210b和220b,每个支路分别在251和252处具有一个中点。uwb天线250安装在所考虑的两个中点之间(因此是桥的形状像h形)。第一支路210b包括在电源端子vdd和中点251之间的第一开关213以及在中点251和地之间的第二开关217。类似地,第二支路220b包括在电源端子和中点252之间的第一开关223以及在中点252和地之间的第二开关227。开关采用cmos工艺制成。第一支路的第一开关213和第二支路227的第二开关由第一时钟信号clkrf-控制。第二支路的第一开关223和第一支路的第二开关217由第二时钟信号clkrf 控制,第二时钟信号的极性与第一时钟信号的极性相反。因此,当第一时钟信号处于高电平时,电流在天线250中的第一支路的第一开关213中沿第一方向流动,然后在第二支路的第二开关227中流动。相反,当第一时钟信号处于低电平时,电流在天线250中的第二支路的第一开关223中沿与第一方向相反的第二方向流动,然后在第一支路的第二开关217中流动。

14.这种“h”桥架构的主要优点是,电流效率是最佳的,从而通过具有非常高的输入阻抗的cmos开关执行阻抗自适应。另一方面,如果在导通状态下cmos开关两端的电位降非常低(电阻为几欧姆),负载(天线250)端子处的电压漂移是最佳的,接近2xvdd。

15.在专利申请us-a-2012/0027050中,特别是在该文献的图4中描述了采用“h”桥架构的uwb发射器的示例。在该示例中,uwb脉冲是通过使用快速逻辑在中心频率处一次接一次地交替合成的,然后所考虑的交替(使用多个参考电压)被放大并组合成“h”桥,该“h”桥包括与待生成的uwb脉冲中的交替一样多的并联支路。

16.这种架构还导致高能量消耗,以至于uwb脉冲的合成再次在中心频率处一次接一次地交替进行。它还很复杂,因为它需要与组成脉冲的不同交替的振幅电平一样多的参考电压(在低输出阻抗下)。

17.此外,uwb信号频谱的控制难以预测,因为在逻辑组合级和在由“h”桥形成的组合级中存在的寄生电容会通过滤波使uwb脉冲失真。

18.最后,可用的参考电压的数目限制了生成器的可重构性。

19.因此,本发明旨在提供一种消耗非常低的uwb发射器架构,该架构是可重构的,并且允许精确地控制发射的uwb脉冲的频谱。

技术实现要素:

20.本发明由如权利要求1所给出的uwb脉冲发射器定义。从属权利要求中指定了优选实施例。

附图说明

21.在阅读参照附图描述的本发明的优选实施例时,本发明的其他特征和优点将显现出来,在附图中:

22.图1示意性地示出了现有技术中已知的uwb发射器的一般架构。

23.图2示意性地示出了现有技术中已知的uwb发射器中使用的“h”桥。

24.图3示意性地示出根据本发明第一实施例的uwb发射器的一般架构。

25.图4a示意性地示出了根据图3的一般架构的uwb发射器,详细说明了第一包络形状

控制模块和第二包络形状控制模块的实现示例。

26.图4b示出了在图4a的uwb发射器中介入的信号的时间图。

27.图4c示意性地示出了在发射闭合脉冲串的情况下,为图4a的发射器生成时钟信号和包络控制信号的电路。

28.图5示意性地示出了根据图3的架构的uwb发射器,其适合执行qpsk或8-psk调制。

29.图6示意性地示出了根据图3的架构的uwb发射器,其配备有根据第一实现方式变体的振幅控制级。

30.图7示意性地示出了根据图3的架构的uwb发射器,其配备有根据第二实现方式变体的振幅控制级。

31.图8示意性地示出了根据本发明第二实施例的uwb发射器的一般架构。

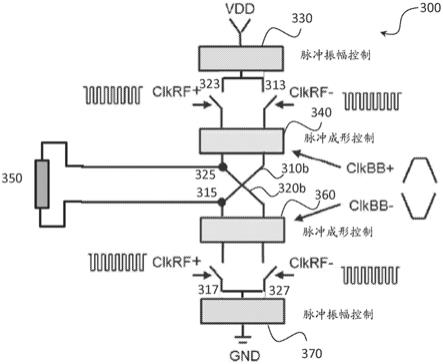

32.图9示意性地示出了根据本发明第三实施例的uwb发射器的一般架构。

33.图10a示出了由图9的uwb发射器生成的脉冲串的示例。

34.图10b示出了图10a的脉冲串的基本脉冲。

35.图10c示出了图10a的脉冲串的频谱占用和图10b的基本脉冲的频谱占用。

具体实施方式

36.本发明的总体思想是提供一种uwb发射器,该uwb发射器再次基于“h”桥架构,但在h桥的支路内,一方面集成了对uwb脉冲包络形状的基带控制,另一方面集成了与对包络形状的控制不同的、对这些脉冲振幅的控制。

37.图3示意性地示出了根据本发明第一实施例的uwb发射器的一般架构。

38.基于“h”桥300的uwb发射器包括两个并联支路。如图2所示的h桥,我们在第一支路中发现第一开关313、中点315和第二开关317。以同样的方式,我们在第二支路中发现第一开关323、第二中点325和第二开关327。第一支路的第一开关313和第二支路327的第二开关由第一时钟信号clkrf-控制。第二支路的第一开关323和第一支路的第二开关317由第二时钟信号clkrf 控制,第二时钟信号的极性与第一时钟信号的极性相反。第一时钟信号和第二时钟信号的频率等于待生成的uwb脉冲的中心频率(rf频率)。

39.uwb天线在第一中点315和第二中点325之间上升。它以差分方式进行馈电(差分馈电天线)。

40.与图2不同,uwb发射器包括第一振幅控制模块330,用于控制uwb脉冲包络的正向部分的振幅,该模块位于电源端子和第一支路和第二支路的第一公共端之间。第一振幅控制模块允许调节施加到第一公共端的电压(称为高电压)。

41.对称地,uwb发射器包括第二振幅控制模块370,用于控制uwb脉冲负向部分的振幅,该模块位于第一支路和第二支路的第二公共端与地之间。第二振幅控制模块允许设置施加到第二公共端的电压(称为低电压)。

42.uwb发射器还包括第一包络控制模块340,其通过第一形状控制信号clkbb 控制uwb脉冲的正向部分的包络的形状,该模块位于第一开关313、323和相应的中点315、325之间。对称地,uwb发射器包括第二包络控制模块360,其通过第二形状控制信号clkbb-控制uwb脉冲负向部分的包络的形状,该模块位于中点315、325与第一支路和第二支路317、327的第二开关之间。需要注意的是,形状控制信号clkbb 和clkbb-是低频信号(在基带中),因

为它们对应于uwb脉冲的振幅调制。换句话说,这些形状控制信号的频谱位于远低于uwb脉冲的中心频率f0的频谱带中。通过控制低频脉冲包络的形状,而不是在rf频率f0处合成每一个半波,可以显著降低发射器的消耗。

43.图3所示的uwb发射器架构具有若干个有利特征。

44.首先,通过简单地控制支路末端的高电压(通过模块330)和低电压(通过模块370)来静态地执行振幅控制。因此,我们避免了数字地存储若干个增益电平的波形或模拟地生成大量参考电压。

45.然后,由发射器发射的uwb脉冲的包络的形状由第一包络控制模块340和第二包络控制模块360差分控制。对uwb脉冲的成形的控制与对其振幅的控制无关。这两个控制直接在功率放大级串联操作,而不需要任何阻抗自适应或附加电路,这也有助于降低发射器的总消耗。

46.此外,脉冲频谱的控制是简单和精确的。包络形状控制信号可以以简单的分量在低频下生成。它们直接施加到功率放大级,而不需要引入阻抗变换级。在开关和负载(在这种情况下是uwb天线)之间存在包络成形级,允许后者与在rf频率下的开关瞬态隔离。这种特性有助于生成的uwb脉冲的频谱纯度,并因此有助于使它们符合频谱掩码。

47.图4a示意性地示出了根据图3的一般架构的uwb发射器,并详细说明了第一包络形状控制模块和第二包络形状控制模块的实现示例。

48.图4a示出了第一支路410的第一开关413和第二开关417和第二支路420的第一开关423和第二开关427。第一开关413和423是pmos晶体管,第二开关417和427是nmos晶体管,从而功率放大级由第一cmos反相器(413和417)和第二cmos反相器(423和427)制成,它们的各自输出连接到负载的端子。

49.振幅控制级由振幅控制模块430、470组成,振幅控制模块430、470与包络控制级串联,包络控制级由包络控制模块440和460组成。

50.振幅控制模块的架构将在后面详细说明。

51.使用mosfet晶体管实现第一包络控制模块440和第二包络控制模块460。更具体地说,第一包络成形模块440包括位于第一支路410中的第一pmos晶体管441和位于第二支路420中的第二pmos晶体管442。第一pmos晶体管441的源极和漏极分别连接到pmos晶体管413的漏极,和第一中点415,该第一中点连接到负载450的第一端子。类似地,第二pmos晶体管442的源极和漏极分别连接到pmos晶体管423的漏极,和第二中点425,该第二中点连接到负载450的第二端子。第一包络控制模块440的第一晶体管441和第二晶体管442由第一包络控制信号clkbbo-控制。该信号由第一包络控制信号生成模块445(如图右侧所示)从第一控制信号clkbbi 中生成。

52.对称地,第二包络控制模块460包括位于第一支路410中的第一nmos晶体管461和位于第二支路420中的第二nmos晶体管462。第一nmos晶体管461的源极和漏极分别连接到nmos晶体管的漏极417和第一中点415。类似地,第二nmos晶体管462的源极和漏极分别连接到nmos晶体管的漏极427和第二中点425。

53.第二包络控制模块460的第一晶体管461和第二晶体管462由第二包络控制信号clkbbo 控制。该信号由第二包络控制信号生成模块465(如图右侧所示)从第二控制信号clkbbi-中生成。

54.第一包络控制信号生成模块和第二包络控制信号生成模块具有相同的结构。

55.更具体地说,考虑到第一包络控制信号生成模块445,第一控制信号clkbbi 控制串联安装在电源和地之间的一对pmos 447和nmos 448晶体管的栅极。pmos晶体管447的源极经由第一可变电阻器446连接到电源,而nmos晶体管448的源极经由第二可变电阻器449连接到地。晶体管447和448的漏极互连。因此,当第一控制信号clkbbi 包括高电压脉冲时,pmos晶体管447关断,而nmos晶体管448导通。因此,晶体管441的栅源电容和晶体管442的栅源电容通过第二可变电阻器449放电。第一包络控制信号生成模块输出端处的信号clkbbo-的振幅线性减小。振幅减小率由上述并联栅源电容和第二可变电阻器449的值给出。在脉冲结束时,pmos晶体管447导通,nmos晶体管448关断,然后晶体管441和442的栅源电容通过可变电阻器446充电,并且信号的振幅线性增加。振幅增加率由上述栅源电容和第一可变电阻器446的值给出。

56.关于第二包络控制信号生成模块465,第二控制信号clkbbi-控制串联安装在电源和地之间的一对pmos 467和nmos 468晶体管的栅极。pmos晶体管467的源极经由第一可变电阻器466连接到电源,而nmos晶体管468的源极经由第二可变电阻器469连接到地。晶体管467和468的漏极互连。因此,当第二控制信号clkbbi-包括低电压脉冲时,pmos晶体管467导通而nmos晶体管468截止。结果,晶体管461的栅极-源极电容和晶体管462的栅极-源极电容通过第一可变电阻器466充电。第二包络控制信号生成模块输出的clkbbo 信号的振幅线性增加。振幅增加率由上述栅极-源极电容和第一可变电阻器466的值给出。在脉冲结束时,pmos晶体管467关断,nmos晶体管468导通,然后晶体管461和462的栅源电容通过可变电阻器469放电,并且信号clkbbo 的振幅线性减小。振幅减小率由上述栅极-源极电容和第二可变电阻器469的值给出。

57.模块445和465的第一可变电阻器446和466有利地具有480所示的相同结构。

58.这样的第一可变电阻器由串联安装在电源电压和pmos晶体管(视情况而定447或467)的源极之间的一组基本电阻器481-1、

…

、481-n组成。每个基本电阻器481-n可能通过并联连接在该基本电阻器上的对应晶体管482-2(这里是pmos晶体管)短路。因此,第一电阻由未短路(也就是说,其栅极控制处于高状态)的基本电阻之和决定。可以选择一致的基本电阻,在这种情况下控制码是测温的,或者遵循2次方几何级数,在这种情况下控制码是二进制的。

59.第一可变电阻器446、466中的每一个可变电阻器可能通过如485所示的晶体管(这里为pmos晶体管)短路。第一包络控制信号生成模块445的晶体管485由第二验证信号clkrfopt-控制,第二包络控制信号生成模块465的晶体管485由第一验证信号clkrfopt 控制。该晶体管用于启动和终止uwb脉冲的成形。因此,验证信号clkrfopt 、clkrfopt-,可以被分别视为每个都给出uwb脉冲的开始和结束。

60.类似地,模块445和465的第二可变电阻器449和469也有利地具有如490所示的相同的结构。这种第二可变电阻器由串联连接在nmos晶体管(视情况而定449或469)的源极和地之间的一组基本电阻器491-1、

…

、491-n组成。每个基本电阻器491-n可能通过相关的晶体管(在此为nmos晶体管)492-n短路。因此,第二电阻由未短路(也就是说,其栅极控制处于低状态)的基本电阻之和决定。这里同样地,可以选择一致的基本电阻,在这种情况下控制代码是测温的,或者遵循2次方几何级数,在这种情况下控制代码是二进制的。

61.第二可变电阻器449、469中的每一个可变电阻器可能通过如495所示的晶体管(在此为nmos晶体管)短路。第一包络控制信号生成模块445的晶体管495由第二验证信号clkrfopt-控制,第二包络控制信号生成模块465的晶体管495由第一验证信号clkrfopt 控制。因此,该晶体管具有启动和终止uwb脉冲成形的功能。

62.图4b示出了由图4a的发射器生成uwb脉冲所涉及的信号的时间图。

63.线(a)表示rf频率下f0的基本时钟clkrf,该rf频率实际上是所成生脉冲的中心频率。

64.线(b)表示在对发射信号施加bpsk调制的情况下的极性信号pol。在极性改变的情况下,在(e)和(f)中表示的开关信号clkrfo-和clkrfo 的相位被反转。由于开关信号clkrfo-和clkrfo 彼此反转,因此可以通过简单地切换这些信号来实现极性的改变。

65.应该注意的是,如后面所解释的,高阶(qpsk、8-psk等)的相位调制也是可能的。

66.彼此相反的第一验证信号clkrfopt-和第二验证信号clkrfopt 用线(c)和(d)表示。这些信号在时间上限定每个脉冲,更具体地说,限定uwb脉冲成形的间隔。

67.需要注意的是,开关信号clkrfo-和clkrfo 仅在由信号clkrfopt-和clkrfopt 定义的验证间隔期间包括基本时钟的半波。因此,“h”桥的消耗进一步减少,因为它被限制在功率放大发生的间隔期间。当晶体管423和442、461和417导通时(在这种情况下,端子425和415之间的电位差为正)生成uwb脉冲的正半波,并且当晶体管413和441、462和427导通时生成uwb脉冲的负半波。振动的振幅由包络控制信号clkbbo-和clkbbo 差分确定。

68.在(g)和(h)中表示的第一控制信号clkbbi 和第二控制信号clkbbi-彼此相反。这些信号在时间上限定脉冲包络的增大斜坡和减小斜坡。

69.当第一控制信号clkbbi 处于高状态(因此第二控制信号clkbbi-处于低状态)时,(i)中指示的第一包络控制信号clkbbo-具有减小的斜坡。相反,当第一控制信号clkbbi 处于低状态时,它具有增大斜坡。

70.类似地,当第二控制信号clkbbi-处于低状态(因此第一控制信号clkbbi 处于高状态)时,(j)所示的第二包络控制信号clkbbo 具有增大的斜坡。相反,当第二控制信号clkbbi-处于高状态时,第二包络控制信号clkbbi 具有减小斜坡。

71.如上所述,通过在rc电路中充电和放电,获得包络控制信号clkbbo-和clkbbo 的增大斜坡和减小斜坡,其中r是可变电阻(446和466用于充电,449和469用于放电),c是对应于栅极-源极电容之和的固定电容(441与442并联用于clkbbo-,461与462并联用于clkbbo )。因此,包络控制信号具有三角形形状,这允许高斯包络形状的满意近似。

72.验证信号clkrfopt-和clkrfopt 将第一包络控制信号clkbbo-设置为高电平,将第二包络控制信号clkbbo 设置为低电平。因此,在验证信号clkrfopt-和clkrfopt 定义的时间间隔之外,不会生成脉冲包络调制的增减斜坡,这将发射器的消耗降低到严格的最小值。

73.最后,负载(天线)端子上的电压用(k)表示。脉冲仅出现在由clkrfopt-和clkrfopt-定义的验证间隔期间。它们的包络的形状仅在这些间隔期间被调制。这些脉冲进一步具有由调制信号bpsk,pol给出的相位。

74.图4c示意性地示出了在发射闭合脉冲串的情况下为图4a的发射器生成时钟信号和包络控制信号的电路。

75.第一控制信号clkbbi 在此被分解为两个(更一般地分解为多个)交替的控制信号clkbb1i 和clkbb2i 。换句话说,这些控制信号中的每一个控制信号都具有脉冲重复频率,即,该clkbbi 的一半脉冲,clkbbi 上的(正向)脉冲之后为clkbb2i 上的(正向)脉冲。信号clkbb1i 和clkbb2i 中的每一个信号被输入到如图4a中的445所示的第一包络控制信号生成模块中。被表示为clkbb1o-和clkbb2o-的相应的输出信号本身是交错的。它们通过诸如497-1和497-2之类的开关组合,交替地通过clkbb1o-脉冲和clkbb2o-脉冲,以提供第一包络控制信号clkbbo-。

76.类似地,第二控制信号clkbbi-被分解成两个交错的控制信号clkbb1i-和clkbb2i-。换句话说,这些控制信号中的每一个控制信号都具有脉冲重复频率,即,该clkbbi-的一半脉冲,clkbb1i-上的(负向)脉冲之后为clkbb2i-上的(负向)脉冲。信号clkbb1i-和clkbb2i-中的每一个信号被输入到如图4a中的465所示的第二包络控制信号生成模块中。被表示为clkbb1o-和clkbb2o-的相应的输出信号本身是交错的。它们通过诸如497-1和497-2之类的开关组合,交替地通过clkbb1o 脉冲和clkbb2o 脉冲,以提供第二包络控制信号clkbbo 。

77.因此,有利地可以生成uwb脉冲串,例如发射8个脉冲,这些脉冲被4ns隔开,并且具有如ieee 802.15.4z标准所规定的交替极性。

78.图5示意性地示出了根据图3的架构的uwb发射器,其实现了qpsk或8-psk调制。

79.图5示出了:由包络控制模块540和560组成的包络成形级,其与上述描述的模块440和460一致;以及由模块530和570组成的振幅控制级,其与模块430和470相同,其结构将在之后描述。

80.与图4a的uwb发射器不同,功率放大级包括第一支路510中位于第一公共端和第一包络控制模块540之间的两个并联开关513-1和513-2,以及位于第二包络控制模块560和第二公共端之间的两个并联开关517-1和517-2。

81.更具体地说,开关513-1和513-2是pmos晶体管,它们的源极连接到第一公共端,它们的高电压由第一振幅控制模块设置,它们的漏极连接到pmos晶体管541的源极。晶体管513-1和513-2的栅极分别由信号clkf01p 和clkf02p 控制。类似地,开关517-1和517-2是nmos晶体管,它们的源极连接到第二公共端,它们的低电压由第二振幅控制模块设置,它们的漏极连接到nmos晶体管561的源极。晶体管517-1和517-2的栅极分别由信号clkf01n 和clkf02n 控制。

82.类似地,开关523-1和523-2是pmos晶体管,它们的源极连接到第一公共端,它们的漏极连接到pmos晶体管542的源极。晶体管523-1和523-2的栅极分别由信号clkf01p-和clkf02p-控制。最后,开关527-1和527-2是nmos晶体管,它们的源极连接到第二公共端,它们的漏极连接到nmos晶体管562的源极。晶体管527-1和527-2的栅极分别由信号clkf01n-和clkf02n-控制。

83.信号clkf01p 和clkf02p 、clkf01n 和clkf02n 、clkf01p-和clkf02p-、clkf01n-和clkf02n-从图的右侧示出的开关信号生成系统590生成。该系统590分别以相位(0

°

)、相位正交(90

°

)、相位反向(180

°

)和反向相位正交(-90

°

)在频率rf f0(uwb脉冲的中心频率)下接收时钟clkf0-i、clkf0-q、clkf0-lb和clkf0-qb作为输入。它还接收待传输的符号的分量(i、q)。根据i和q的值,开关信号生成系统将上述开关信号上的输入时钟复用。对于不同

的调制类型,在表1中给出了复用表。为简化表示,时钟clkf0-i、clkf0-q、clkf0-lb和clkf0-qb已由表中的后缀l、q、lb、qb指定。

84.qpsk调制可以以两种可能的方式实现。在第一种方式(表1中称为选项1)中,对于待发送的qpsk符号,在2个正交信道上同时生成两个uwb脉冲,每个脉冲由所考虑的qpsk符号的分量调制。在第二种方式中(在表1中称为选项2a),携带符号的2个分量的uwb脉冲在2个信道上交替生成。表1也示出了第二信道被抵消(第6-9列)的变体(表1中的选项2b)。当然,第一信道也可以被抵消,而不是第二信道被抵消。

85.通过如表1所示的上述选项1和2a的组合可以实现8-psk调制。在必要时,可通过作用于振幅控制的因子对符号(-1,-1)、(-1,1)、(1,1)和(1,-1)进行归一化。表1

86.图6示意性地示出了根据图3的架构的uwb发射器,其配备有根据第一实现方式变体的振幅控制级。

87.图6示出了由第一支路中的开关613和617以及第二支路中的开关623和627组成的功率放大级。包络控制级与功率放大级串联,包络控制级由模块640和660组成,它们与之前描述的模块440和460一致。

88.振幅控制级也与功率放大级和包络控制级串联。振幅控制级由位于第一公共端和电源电压之间的第一振幅控制模块630以及位于第二端和地之间的第二振幅控制模块670组成。更具体地说,这里的第一模块630由单个pmos晶体管631组成,其源极连接到电源vdd,其漏极连接到第一公共端。第一支路的第一开关晶体管的源极613和第二支路的第一开关晶体管的源极623连接到该第一公共端。类似地,第二模块670由单个nmos晶体管671组成,

其源极连接到地,其漏极连接到第二公共端。第一支路的第二晶体管的源极617和第二支路的第二晶体管的源极627连接到该第二公共端。

89.施加在晶体管631栅极上的信号vref 通过粗电压阶梯680生成,其输出提供在第一细电压阶梯635上。类似地,施加在晶体管671栅极上的信号vref-通过粗电压阶梯680生成,其输出提供在第二细电压阶梯675上。

90.对于生成信号vref 和vref-,粗电压阶梯680是共用的,它简单地由第一组n 1个串联在电源电压vdd和地之间的、相同值的基本电阻组成。

91.在粗电压阶梯的中间节点处可用的n 1个参考电压vrefh《0》、vrefh《1》、

…

、vrefh《n》在第一细电压阶梯635的输入处被提供给多路复用器636。该输入多路复用器通过第一选择信号selvrefh ,在680的n 1个可用参考电压中选择两个连续的参考电压vrefh《n》和vrefh《n 1》。第二细电压阶梯包括串联排布在这样选择的两个参考电压vrefh《n》和vrefh《n 1》之间的m 1个基本电阻器(具有相同的值)。在该第二阶梯的中间节点处,可用的m 1个参考电压,vrefl 《0》、

…

、vrefl 《m》被提供给输出多路复用器637。该输出多路复用器通过第二选择信号selvrefl ,在m 1个可用电压中选择参考电压vrefl 《m》

…

,并将其作为信号vref 提供给输出端。

92.类似地,在粗电压阶梯的中间节点处可用的n 1个参考电压vrefh《0》、vrefh《1》、

…

、vrefh《n》在第二细电压阶梯675的输入处被提供给多路复用器676。该输入多路复用器通过第一选择信号selvrefh-,在n 1个可用参考电压中选择两个连续的参考电压vrefh-《n》和vrefh-《n 1》。第二细电压阶梯包括串联排布在这样选择的两个参考电压vrefh-《n》和vrefh-《n 1》之间的m 1个基本电阻器(具有相同的值)。在该第二阶梯的中间节点处,可用的m 1个参考电压,vrefl-《0》、

…

、vrefl-《m》、

…

,被提供给输出多路复用器677。该输出多路复用器通过第二选择信号selvrefl-,在m 1个可用电压中选择参考电压vrefl-《m》

…

,并将其作为信号vref-输出。

93.在晶体管631的栅极上施加信号vref 和在晶体管671的栅极上施加信号vref-允许调节这些晶体管的漏源电阻,并因此降低相对于电源电压的高电压(通过vref ),以及当这些晶体管被电流穿过时提高相对于地的最小电压(通过vref-)。因此,晶体管631和671的联合作用允许在宽的动态范围内同质地改变包络的振幅,而与包络形状的控制无关。

94.生成信号vref 和vref-的电路消耗仅限于在电压梯级中循环的电流(几μa)引起的消耗。

95.图7示意性地示出了根据图3的架构的uwb发射器,其配备有根据第二实现方式变体的振幅控制级。

96.由第一支路中的开关713和717以及第二支路中的开关723和727组成的功率放大级与图6中的一致。类似地,包络形状控制级包括模块740和760,分别与图6的模块640和660一致。

97.然而,位于第一公共端和电源电压之间的第一振幅控制模块730以及位于第二公共端和地之间的第二振幅控制模块770不同于图6的相应模块630和670。

98.实际上,第一振幅控制模块730由多个第一传输门731-0、731-1、

…

、731-n组成,它们并联安装在电源电压vdd和连接pmos晶体管713和723的源极的第一公共端之间。第一传输门可以由简单的pmos晶体管组成。本领域技术人员可以想到这些传输门的替代方案。

99.因此,通过利用第一选择信号sel-tgp《0》、sel-tgp《1》、

…

、sel-tgp《n》选择第一传输门,可以调节电压vdd和mos晶体管源极的公共节点之间的等效电阻。因此,一旦电流通过桥,就可以使用上述选择信号降低高电压。

100.类似地,第二振幅控制模块770由多个第二传输门771-0、771-1、

…

、771-n组成,它们并联安装在连接nmos晶体管717和727的源极的第二公共端与地之间。第二传输门可以由简单的nmos晶体管组成。本领域技术人员可以想到这些传输门的替代方案。

101.因此,一旦电流通过h桥,就可以使用分别控制栅极771-0、771-1、

…

、771-n的第二选择信号sel-tgn《0》、sel-tgn《1》、

…

、sel-tgn《n》来提高低电压。

102.与图6所示的振幅控制模块相比,图7所示的振幅控制模块的实现方式变体具有不消耗静态功率的优点。实际上,这里不需要提供电阻器阶梯来生成参考电压,因此除了生成通过负载的脉冲所需的电流之外,不消耗电流。

103.在不脱离本发明的范围的情况下,也可以考虑振幅控制模块的其他实现方式变体。特别地,振幅控制模块可以借助于ldo电压调节器(低压差调节器)制成。

104.图8示意性地示出了根据本发明第二实施例的uwb发射器的一般架构。

105.振幅控制级、功率放大级和包络形状控制级与结合图3描述的第一实施例中的级相同,因此,这里不再赘述。

106.然而,与第一实施例不同的是,uwb天线850不是以差分模式馈电,而是单馈电天线。更具体地说,形成发射器的第一输出的第一支路810b的中点815经由去耦电容器853连接到50ω的特性负载855。形成发射器的第二输出的第二支路820b的中点825通过去耦电容器854连接到天线850。电容器853和854具有相同的值,并且意图在发射器的输出处不施加偏振点。

107.本领域技术人员应当理解,结合第一实施例公开的不同变体和实施例也适用于第二实施例。

108.在第一实施例和第二实施例中,假设振幅控制由从电源端子操作以改变高电压的第一振幅控制模块和从地操作以改变低电压的第二振幅控制模块来执行。然而,本领域技术人员应该理解,可以交替地提供单个振幅控制模块来改变高电压或低电压。

109.图9示意性地示出了根据本发明第三实施例的uwb发射器的一般架构。

110.第三实施例与先前实施例的不同之处在于,uwb发射器包括多个并联连接的h桥,每个桥的uwb脉冲被独立地控制并通过去耦电容器在公共uwb天线的端子处组合。

111.在本实施例中,h桥的结构可以是如上所述的第一实施例或第二实施例列出的h桥的结构。

112.方便起见,在下面的描述中,假定h桥的结构符合第一实施例。

113.更具体地,uwb发射器包括多个(n个)并联的h桥900,其承载特定参考tx pa1、...、tc pan。这些h桥中的每一个h桥的第一支路的相应的第一中点915通过多个第一桥解耦电容器954连接到第一公共端子955。类似地,这些桥的第二支路的第二中点925通过多个第二桥解耦电容器953连接到第二公共端子956。

114.uwb天线950连接在第一公共端子和第二公共端子之间。然而,应该理解,在h桥的结构符合第二实施例的情况下,uwb天线将仅连接到这些公共端子中的一个,另一个公共端子通过特性阻抗连接到地。

115.桥接去耦电容器确保各个桥的连续分量之间没有相互作用,同时允许在天线的端子处组合由不同桥生成的uwb脉冲的交替分量。

116.每个h桥包括在所述桥的两个支路处,位于电源端子和第一公共端931之间第一振幅控制模块(未示出),第一振幅控制模块允许改变该第一公共端处的高电压。类似地,位于h桥的第一支路和第二支路处的第二公共端971和地之间的第二振幅控制模块(未示出)允许改变第二公共端处的低电压。

117.和之前实施例中描述的一样,每个h桥包括在第一开关913、923和第一支路和第二支路的相应中点915、925之间的第一包络控制模块941、942,通过与该h桥相关联的第一基带信号(clkbb-),对由该h桥生成的uwb脉冲的正向部分的包络进行成形。

118.它还包括位于中点915、925和该h桥的第二开关917、927之间的第二包络控制模块961、962,通过与该h桥相关联的第二基带信号(clkbb )对由该h桥生成的uwb脉冲的负向部分的包络进行成形。

119.和之前实施例中描述的一样,对于每个桥900,第一支路的第一(第二)开关切换状态与第二支路的第一开关(第二)的切换状态相反。每个开关以相同的中心rf频率切换,rf频率给出由该桥生成的uwb脉冲的中心频率。

120.需要注意的是,不同桥的第一包络控制模块由相互独立的第一基带信号控制。类似地,不同桥的第二包络控制模块由相互独立的第二基带信号控制。第一基带信号和第二基带信号由独立模块990生成。

121.不同桥的第一支路的第一开关和第二开关有利地在相同的rf频率下由相同的信号clkrf0 切换。类似地,不同桥的第二支路的第一开关和第二开关在相同的rf频率下由相同的信号clkrf0-切换,该信号是前一个信号的逆信号。因此,这些开关的控制信号可以由公共模块生成。或者,它们可以由独立模块990从公共rf时钟生成。

122.第三实施例允许生成基本脉冲串,基本脉冲串可以非常接近或者甚至在时间上重叠,具有很大的控制灵活性。特别地,每个基本脉冲的极性可以通过第一基带信号和第二基带信号单独控制。这种控制灵活性还允许确保基本脉冲串符合在有效标准(etsi、fcc、arib)中定义的uwb频谱掩码。

123.图10a示出了在时域中可由图9的uwb脉冲发射器生成的基本脉冲串,图10b示出了该脉冲串的基本脉冲。

124.图10c示出了图10的基本脉冲串的频谱和图10b的基本脉冲的频谱。注意,这两个频谱实际上符合上述频谱掩码。

125.最后,需要指出的是,本技术所提出的技术方案比定义分辨率在rf周期的一小部分范围内的单个h桥的基本脉冲串的总时间支持的解决方案简单得多。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。