1.本公开涉及一种固态成像元件和电子设备,尤其涉及一种可以实现更高图像质量的固态成像元件和电子设备。

背景技术:

2.迄今为止,在诸如数码相机和数码摄像机等具有成像功能的电子设备中,已经使用固态成像元件,例如ccd(电荷耦合器件)和cmos(互补金属氧化物半导体)图像传感器。例如,在cmos图像传感器中,光电二极管中通过光电转换产生的电荷被传输到fd(浮动扩散)单元,并且基于电荷量经由放大晶体管输出的像素信号经过ad(模拟到数字)转换。

3.例如,专利文献1公开了一种能够执行其中在所有行中同时进行从光电二极管到存储器的电荷传输的全局快门操作的cmos图像传感器。

4.[引用列表]

[0005]

[专利文献]

[0006]

[专利文献1]:日本特开2014-72788号公报

技术实现要素:

[0007]

[技术问题]

[0008]

顺便提及,现有技术的cmos图像传感器具有如下结构:被构造为进行全局快门操作的驱动电路被设置在像素阵列区域的一边或像素阵列区域的两个相对边的各边上。因此,由于瞬时电流、配线延迟等引起的ir压降,波形可能会变圆,从而导致曝光时间不均匀。特别地,在高速运转时,曝光时间不均匀非常大从而对图像质量产生不良影响。为此,要求减小这种曝光时间不均匀,从而能够获取具有更高图像质量的图像。

[0009]

鉴于这种情况,提出本公开,并且本公开可以实现更高图像质量。

[0010]

[问题的解决方案]

[0011]

根据本公开的方面,提供了一种固态成像元件,包括:像素,其具有同时驱动所有行的全局驱动部和在相应的时刻驱动各行的滚动驱动部;像素阵列区域,其中多个所述像素布置成阵列;全局驱动电路,其被构造为向所述全局驱动部提供驱动信号;和滚动驱动电路,其被构造为向所述滚动驱动部提供驱动信号。所述全局驱动电路布置在围绕所述像素阵列区域的四边中的至少三边以上的每一边上。

[0012]

根据本公开的另一方面,提供了一种包括固态成像元件的电子设备。固态成像元件包括:像素,其具有同时驱动所有行的全局驱动部和在相应的时刻驱动各行的滚动驱动部;像素阵列区域,其中多个所述像素布置成阵列;全局驱动电路,其被构造为向所述全局驱动部提供驱动信号;和滚动驱动电路,其被构造为向所述滚动驱动部提供驱动信号。所述全局驱动电路布置在围绕所述像素阵列区域的四边中的至少三边以上的每一边上。

[0013]

根据本公开的方面,提供了一种固态成像元件,包括:像素,其具有同时驱动所有行的全局驱动部和在相应的时刻驱动各行的滚动驱动部;像素阵列区域,其中多个所述像

素布置成阵列;全局驱动电路,其被构造为向所述全局驱动部提供驱动信号;和滚动驱动电路,其被构造为向所述滚动驱动部提供驱动信号。此外,所述全局驱动电路布置在围绕所述像素阵列区域的四边中的至少三边以上的每一边上。

附图说明

[0014]

图1是示出本技术适用的成像元件的第一实施方案的构成例的图。

[0015]

图2是示出图1的成像元件的示例性电路构成的图。

[0016]

图3描绘了分别示出全局驱动信号的示例性传输电压的图。

[0017]

图4是示出成像元件的第二实施方案的构成例的图。

[0018]

图5是示出成像元件的第三实施方案的构成例的图。

[0019]

图6是示出成像元件的第四实施方案的构成例的图。

[0020]

图7是图6的成像元件的示例性电路构成的图。

[0021]

图8是示出成像元件的第五实施方案的构成例的图。

[0022]

图9是图8的成像元件的示例性电路构成的图。

[0023]

图10是示出具有两层结构的成像元件的截面构成例的图。

[0024]

图11是示出具有三层结构的成像元件的截面构成例的图。

[0025]

图12是示出成像装置的构成例的框图。

[0026]

图13是示出图像传感器的使用示例的图。

具体实施方式

[0027]

下面参照附图详细说明本技术适用的具体实施方案。

[0028]

《成像元件的第一构成例》

[0029]

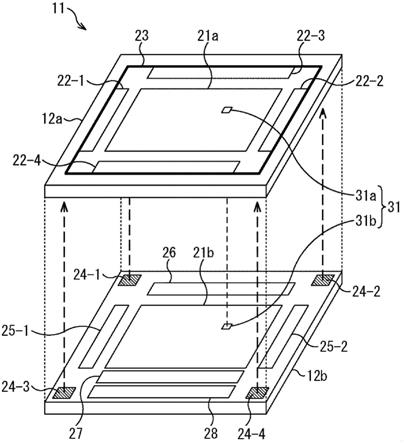

图1是示出本技术适用的成像元件的第一实施方案的构成例的图。

[0030]

例如,图1所示的成像元件11是包括堆叠的多个芯片12的堆叠cmos图像传感器。在图1示出的构成例中,成像元件11具有其中堆叠有上芯片12a和下芯片12b的两层结构。

[0031]

此外,在成像元件11中,多个像素31被布置成阵列。像素31形成为跨越上芯片12a和下芯片12b。像素31的设置在上芯片12a上的一部分被称为上像素31a,并且像素31的设置在下芯片12b上的一部分被称为下像素31b。上像素31a具有在同一时刻驱动所有行的部分(在下文中,称为全局驱动部)和在相应的时刻驱动各行的部分(在下文中,称为滚动驱动部)。此外,下像素31b具有滚动驱动部,但不具有全局驱动部。

[0032]

如图1所示,在上芯片12a上布置有像素阵列区域21a、全局驱动电路22-1至22-4和配线23。此外,在下芯片12b上布置有像素阵列区域21b、电源焊盘24-1至24-4、滚动驱动电路25-1和25-2、负荷mos区域26、ad转换单元27和水平传输电路28。

[0033]

在像素阵列区域21a中,上像素31a被布置成阵列,并且在像素阵列区域21b中,下像素31b被布置成阵列。

[0034]

全局驱动电路22-1至22-4沿像素阵列区域21a的各自的四个边布置。全局驱动电路22-1至22-4的每个输出用于驱动上像素31a的全局驱动部的信号。例如,全局驱动电路22-1沿像素阵列区域21a的左边布置,全局驱动电路22-2沿像素阵列区域21a的右边布置,全局驱动电路22-3沿像素阵列区域21a的上边布置,并且全局驱动电路22-4沿像素阵列区

域21a的下边布置。

[0035]

配线23包括地线和用于提供驱动全局驱动电路22-1至22-4所需的电力的电源线。配线23被布置为围绕上芯片12a的外围(左边、右边、上边和下边),以连接到全局驱动电路22-1至22-4的每个。

[0036]

电源焊盘24-1至24-4是与上芯片12a电连接和机械连接的焊盘,并且被布置在下芯片12b的各自的四个角部处。例如,电源焊盘24-1到24-4分别连接到配线23并且经由配线23将外部供应的电力提供给全局驱动电路22-1到22-4。

[0037]

滚动驱动电路25-1和25-2沿像素阵列区域21b的各自的左右两边布置。滚动驱动电路25-1和25-2的每个输出用于驱动上像素31a和下像素31b的滚动驱动部的信号。

[0038]

例如,在负荷mos区域26中布置有用作用于从像素31读出像素信号的负荷元件的多个mos晶体管。

[0039]

例如,ad转换单元27包括比较器和计数器。ad转换单元27对从像素31读出的像素信号进行ad转换并输出像素信号。

[0040]

例如,水平传输电路28在水平方向上传输从ad转换单元27以逐列的像素31输出的像素信号,并将像素信号输出到成像元件11的后级上的信号处理单元。

[0041]

图2是示出成像元件11的电路构成的图。

[0042]

如图2示出的虚线所示,成像元件11被分割成上芯片12a和下芯片12b。此外,图2示出了上芯片12a的上像素31a和全局驱动电路22以及下芯片12b的下像素31b和滚动驱动电路25的电路构成。

[0043]

上像素31a包括光电二极管51、排出晶体管52、传输晶体管53、存储器54、读出晶体管55和fd单元56。下像素31b包括放大晶体管57、选择晶体管58和复位晶体管59。

[0044]

光电二极管51通过光电转换产生电荷并累积电荷。

[0045]

例如,排出晶体管52以排出信号ofg驱动,并在像素31的曝光开始时将累积在光电二极管51中的电荷排出到漏极ofd。此外,排出晶体管52还具有使产生的超过光电二极管51容量的电荷溢出的功能。

[0046]

传输晶体管53用传输信号trx驱动,并在像素31的曝光期间将光电二极管51中产生的电荷传输到存储器54。

[0047]

存储器54暂时保持经由传输晶体管53传输的电荷,直到逐行读出像素31的时刻为止。

[0048]

读出晶体管55用读出信号trg驱动,并将保持在存储器54中的电荷读出到fd单元56。

[0049]

fd单元56保持经由读出晶体管55读出的电荷,并将基于电荷电平的电位施加到放大晶体管57的栅电极。

[0050]

放大晶体管57放大fd单元56中累积的电荷,并将基于电荷电平的像素信号输出到垂直信号线vsl。

[0051]

选择晶体管58用选择信号sel驱动,并经由垂直信号线vsl将放大晶体管57连接到恒流源61。

[0052]

复位晶体管59用复位信号rst驱动,并排出在存储器54和fd单元56中累积的电荷,以复位像素31。

[0053]

全局驱动电路22包括多个放大器41,即,被构造为向传输晶体管53提供传输信号trx的放大器41-1以及被构造为向排出晶体管52提供排出信号ofg的放大器41-2。注意,在下文中,从全局驱动电路22输出的传输信号trx和排出信号ofg也被适当地称为全局驱动信号。

[0054]

滚动驱动电路25包括多个放大器42,即,被构造为向读出晶体管55提供读出信号trg的放大器42-1以及被构造为向选择晶体管58提供选择信号sel的放大器42-2。

[0055]

因此,由图2中的点划线包围的光电二极管51、排出晶体管52和传输晶体管53对应于像素31的全局驱动部。以类似的方式,由图2中的长虚线-双短虚线包围的读出晶体管55和选择晶体管58对应于像素31的滚动驱动部。

[0056]

如上所述构造成像元件11,使得全局驱动电路22-1至22-4从像素阵列区域21a的四个方向向像素31的全局驱动部提供全局驱动信号。因此,成像元件11具有如下结构:每个像素31提供全局驱动信号的全局驱动电路22的数量与现有技术相比增加,从而导致成像元件11可以减小全局驱动信号的波形变圆。

[0057]

这里,参照图3,说明从全局驱动电路22输出的全局驱动信号的波形。

[0058]

例如,如图3的a所示,由于像素阵列区域21a的端部靠近全局驱动电路22,因此从全局驱动电路22输出的全局驱动信号的波形具有大体上垂直的脉冲边缘(具有急剧上升和下降的变化)。此外,在更靠近像素阵列区域21a的中央部且更远离全局驱动电路22的部分,全局驱动信号变圆。

[0059]

例如,现有技术的成像元件具有其中全局驱动电路被设置在像素阵列区域的一边或两边的各边上的结构。为此,如图3的b所示,在像素阵列区域的中央部中,与端部相比,全局驱动信号的波形主要是圆形的(上升和下降的变化是平缓)。

[0060]

与此相反,如图3的c所示,与现有技术的成像元件相比,成像元件11可以减小全局驱动信号的波形变圆,即,可以防止像素阵列区域21a的中央部中的波形变圆。

[0061]

如上所述,成像元件11可以防止像素阵列区域21a的中央部中的全局驱动信号的波形形状变圆,从而在整个像素阵列区域21a上同时驱动像素31。此外,成像元件11具有其中分布有瞬时电流路径的结构。因此,成像元件11可以减少曝光时间不均匀的发生,即,可以在相同时刻的曝光时间曝光所有像素31,从而即使在高速操作下(以较短的快门时间)也能够获取更高质量的图像。

[0062]

此外,成像元件11具有高效的布局:全局驱动电路22布置在上芯片12a上,并且滚动驱动电路25布置在下芯片12b上,使得与其中这些驱动电路布置在单个芯片上的布局相比,可以使芯片尺寸小型化。

[0063]

《成像元件的第二构成例》

[0064]

图4是示出本技术适用的成像元件的第二实施方案的构成例的图。注意,在图4示出的成像元件11a中,由相同的附图标记表示与图1的成像元件11的组件共同的组件,并省略其详细说明。

[0065]

即,类似于图1的成像元件11,成像元件11a包括堆叠的上芯片12a和下芯片12b。此外,成像元件11a与图1的成像元件11的相似之处在于,像素阵列区21a和配线23布置在上芯片12a上,并且像素阵列区21b、电源焊盘24-1至24-4、滚动驱动电路25-1和25-2、负荷mos区域26、ad转换单元27和水平传输电路28布置在下芯片12b上。

[0066]

此外,成像元件11a与图1的成像元件11的不同之处在于,三个全局驱动电路22-1到22-3布置在上芯片12a上。

[0067]

例如,如上面参照图3所述,通过与现有技术相比增加每个像素31提供全局驱动信号的全局驱动电路22的数量的构成,可以减小全局驱动信号的波形变圆。即,不必使用类似于图1的成像元件11的设置有四个全局驱动电路22-1至22-4的构成,使用设置有至少三个以上的全局驱动电路22的构成就足够了。

[0068]

注意,三个全局驱动电路22-1至22-3不必布置在如图4所示的左边、右边和上边。即,成像元件11a例如可以采用其中全局驱动电路22-1至22-3布置在左边、右边和下边,左边、上边和下边,或者右边、上边和下边。

[0069]

此外,成像元件11a的电路构成类似于图2所示的成像元件11的电路构成。

[0070]

与现有技术的成像元件相比,如上所述构造的成像元件11a可以防止全局驱动信号的波形变圆,以减少曝光时间不均匀的发生,从而能够获取更高质量的图像。

[0071]

《成像元件的第三构成例》

[0072]

图5是示出本技术适用的成像元件的第三实施方案的构成例的图。注意,在图5所示的成像元件11b中,由相同的附图标记表示与图1的成像元件11的组件共同的组件,并省略其详细说明。

[0073]

即,类似于图1的成像元件11,成像元件11b包括堆叠的上芯片12a和下芯片12b。此外,成像元件11b与图1的成像元件11的相似之处在于,像素阵列区21a布置在上芯片12a上,并且像素阵列区21b、电源焊盘24-1至24-4、负荷mos区域26、ad转换单元27和水平传输电路28布置在下芯片12b上。

[0074]

此外,成像元件11a与图1的成像元件11不同之处在于,滚动驱动电路25-1和25-2布置在上芯片12a上,并且全局驱动电路22-1到22-4布置在下芯片12b上。

[0075]

如上所述,具有其中全局驱动电路22-1至22-4被设置在下芯片12b上以驱动布置在上芯片12a的像素阵列区域21a中的上像素31a的全局驱动部的构成的成像元件11b也可以减小全局驱动信号的波形变圆。特别地,成像元件11b具有如下构成:全局驱动电路22-1到22-4布置在电源焊盘24-1到24-4附近,并且因此可以向全局驱动电路22-1至22-4提供更多的电力。因此,成像元件11b可以进一步减小全局驱动信号的波形变圆。

[0076]

此外,成像元件11b的电路构成类似于图2所示的成像元件11的电路构成。

[0077]

与现有技术的成像元件相比,如上所述构造的成像元件11b可以防止全局驱动信号的波形变圆,以减少曝光时间不均匀的发生,从而能够获取更高质量的图像。

[0078]

《成像元件的第四构成例》

[0079]

图6是示出本技术适用的成像元件的第四实施方案的构成例的图。注意,在图6示出的成像元件11c中,由相同的附图标记表示与图1的成像元件11的组件共同的组件,并省略其详细说明。

[0080]

即,类似于图1的成像元件11,成像元件11c包括堆叠的上芯片12a和下芯片12b。此外,成像元件11c与图1的成像元件11的相似之处在于,像素阵列区21a和配线23布置在上芯片12a上,并且像素阵列区21b、电源焊盘24-1至24-4、滚动驱动电路25-1和25-2、负荷mos区域26、ad转换单元27和水平传输电路28布置在下芯片12b上。

[0081]

此外,成像元件11c与图1的成像元件11的不同之处在于,全局驱动电路22-1a至

22-4a布置在上芯片12a上,并且全局驱动电路22-1b至22-4b布置在下芯片12b上。即,在成像元件11c中,全局驱动电路22包括全局驱动电路22a和22b,使得全局驱动电路22形成为跨越上芯片12a和下芯片12b。

[0082]

参照图7,说明成像元件11c的全局驱动电路22的结构。注意,在下文中,以类似方式构造的放大器41-1和41-2被简称为放大器41。

[0083]

如图7所示,在成像元件11c中,全局驱动电路22的放大器41包括n型晶体管71a和p型晶体管71b。此外,成像元件11c具有如下布局:n型晶体管71a布置在上芯片12a的全局驱动电路22a中且p型晶体管71b布置在下芯片12b的全局驱动电路22b中。

[0084]

通过具有这种构成的成像元件11c,例如,在上像素31a仅包括n型晶体管的情况下,可以仅使用nmos工艺制造上芯片12a。

[0085]

此外,成像元件11c可以仅在全局驱动信号下降(高电平到低电平)时减小全局驱动信号的波形变圆。因此,成像元件11c也可以减少曝光时间不均匀的发生,从而,相比现有技术的成像元件的情况,获取更高质量的图像。

[0086]

《成像元件的第五构成例》

[0087]

图8是示出本技术适用的成像元件的第五实施方案的构成例的图。注意,在图8所示的成像元件11d中,由相同的附图标记表示与图1的成像元件11的组件共同的组件,并省略其详细说明。

[0088]

即,类似于图1的成像元件11,成像元件11d包括堆叠的上芯片12a和下芯片12b。此外,成像元件11d与图1的成像元件11的相似之处在于,像素阵列区21a、全局驱动电路22-1至22-4以及配线23布置在上芯片12a上,并且像素阵列区21b、电源焊盘24-1至24-4、滚动驱动电路25-1和25-2以及水平传输电路28布置在下芯片12b上。

[0089]

此外,成像元件11d与图1的成像元件11的不同之处在于,模拟像素信号在像素31内部经过ad转换,并且输出数字像素信号。

[0090]

参照图9,说明了成像元件11d的像素31的构成。

[0091]

如图9所示,像素31包括光电二极管51、排出晶体管52、传输晶体管53、fd单元56、比较器81、计数器82和锁存器83。此外,像素31具有比较器81形成为跨越上芯片12a和下芯片12b的结构,通过比较器81和计数器82对fd单元56中累积的电荷进行ad转换。

[0092]

此外,成像元件11d被构造为将来自滚动驱动电路25的锁存数据读出控制信号提供给锁存器83,并且在逐行读出数字像素信号的情况下,锁存器83可以被视为像素31的滚动驱动部。即,像素31的滚动驱动部被构造为处理数字信号而非模拟信号。

[0093]

与现有技术的成像元件相比,如上所述构造的成像元件11d可以防止全局驱动信号的波形变圆以减少曝光时间不均匀的发生,从而能够获取更高质量的图像。

[0094]

《成像元件的堆叠构成》

[0095]

参照图10和图11,说明了成像元件11的堆叠构成。

[0096]

图10示出了具有如上所述的两层结构的成像元件11的截面构成例。

[0097]

上芯片12a具有其中绝缘层102、滤光器层103和片上透镜层104堆叠在半导体层101的背面侧上并且配线层105堆叠在半导体层101的正面侧上的截面。例如,在半导体层101中,针对每个像素31形成光电二极管51、存储器54等,并且为存储器54遮光。

[0098]

下芯片12b具有其中配线层112堆叠在半导体层111上的截面。

[0099]

此外,在成像元件11中,形成为从上芯片12a的配线层105露出的连接焊盘和形成为从下芯片12b的配线层112露出的连接焊盘彼此电性地且机械地连接。

[0100]

例如,具有这种堆叠结构的成像元件11具有其中逻辑电路等被设置在下芯片12b的像素阵列区域21b的外侧的周边区域中的构成。因此,在上芯片12a和下芯片12b具有相同的芯片尺寸的情况下,获得了其中元件等未形成在上芯片12a的像素阵列区域21a的外侧的周边区域中的具有余量的布局。因此,成像元件11具有其中全局驱动电路22-1至22-4被设置在上芯片12a的周边区域中的布局,并且因此可以更有效地增加封装密度。

[0101]

图11示出了具有三层结构的成像元件11e的截面构成例。

[0102]

即,成像元件11e包括堆叠的上芯片12a、下芯片12b和逻辑芯片12c。

[0103]

上芯片12a的截面类似于图10的上芯片12a的截面,并且下芯片12b具有其中添加有用于在逻辑芯片12c上堆叠下芯片12b的配线层113的截面。逻辑芯片12c具有其中配线层122被堆叠在半导体层121上的截面。

[0104]

此外,在成像元件11e中,逻辑电路形成在逻辑芯片12c上,并且负荷mos区域26、ad转换单元27和水平传输电路28也可以形成在逻辑芯片12c上。因此,成像元件11e可以采用如下布局:全局驱动电路22-1至22-4被设置在上芯片12a的周边区域中并且滚动驱动电路25-1和25-2被设置在下芯片12b的周边区域中。

[0105]

与类似于具有两层结构的成像元件11的逻辑电路等被设置在下芯片12b的周边区域中的构成相比,可以进一步使具有这种堆叠结构的成像元件11e小型化。

[0106]

《电子设备的构成例》

[0107]

如上所述的成像元件11可适用于多种电子设备,例如,诸如数码相机和数码摄像机等成像系统、具有成像功能的移动电话以及具有成像功能的其他设备。

[0108]

图12是示出安装在电子设备上的成像装置的构成例的框图。

[0109]

如图12所示,成像装置201包括光学系统202、成像元件203、信号处理电路204、监视器205和存储器206,并且可以获取静止图像和运动图像。

[0110]

光学系统202包括一个或多个透镜。光学系统202将来自被摄体的图像光(入射光)引导到成像元件203,并在成像元件203的光接收表面(传感器单元)上形成图像。

[0111]

作为成像元件203,应用上述成像元件11。在成像元件203中,基于经由光学系统202在光接收表面上形成的图像,在一定期间累积电子。然后,将基于成像元件203中累积的电子的信号提供给信号处理电路204。

[0112]

信号处理电路204对从成像元件203输出的像素信号执行各种类型的信号处理。通过信号处理电路204执行信号处理获得的图像(图像数据)被提供给监视器205,以在监视器205上显示,或者被提供给存储器206,以存储(记录)在存储器206中。

[0113]

例如,通过将上述成像元件11适用于如上所述构造的成像装置201,可以获取更高质量的图像。

[0114]

《图像传感器的使用示例》

[0115]

图13是示出上述图像传感器(成像元件)的使用示例的图。

[0116]

例如,上述图像传感器可以用于如下所述感测诸如可见光、红外光、紫外光或x射线等光的各种情况。

[0117]-被构造为拍摄图像以供鉴赏的设备,诸如数码相机和具有相机功能的移动设备

等

[0118]-用于交通的设备,诸如为了诸如自动停止和驾驶员状态识别等安全驾驶的目的而拍摄汽车的前侧、后侧、周围、内部等的车载传感器;监视行进车辆和道路的监视摄像机;以及测量车辆之间的距离的测距传感器等

[0119]-用于诸如电视、冰箱和空调等家用电器的设备,以便拍摄用户的手势并基于手势进行设备操作

[0120]-用于医疗保健的设备,诸如内窥镜和通过接收红外光进行血管造影的设备等

[0121]-用于安保的设备,诸如用于预防犯罪的监视摄像机和用于个人身份验证的相机等

[0122]-用于美容的设备,诸如拍摄皮肤的皮肤测量设备和拍摄头皮的显微镜等

[0123]-用于运动的设备,诸如运动相机和用于运动的可穿戴相机等

[0124]-用于农业的设备,诸如用于监控田地和农作物状况的相机等。

[0125]

《构成组合示例》

[0126]

注意,本技术还可以采用以下构成。

[0127]

(1)

[0128]

一种固态成像元件,包括:

[0129]

像素,其具有同时驱动所有行的全局驱动部和在相应的时刻驱动各行的滚动驱动部;

[0130]

像素阵列区域,其中多个所述像素布置成阵列;

[0131]

全局驱动电路,其被构造为向所述全局驱动部提供驱动信号;和

[0132]

滚动驱动电路,其被构造为向所述滚动驱动部提供驱动信号,

[0133]

其中,所述全局驱动电路布置在围绕所述像素阵列区域的四边中的至少三边以上的每个边上。

[0134]

(2)

[0135]

根据项(1)所述的固态成像元件,其中,所述全局驱动电路包括沿所述像素阵列区域的左边、右边、上边和下边布置的四个全局驱动电路。

[0136]

(3)

[0137]

根据项(1)或(2)所述的固态成像元件,其中,所述固态成像元件具有堆叠有至少两个芯片的堆叠结构。

[0138]

(4)

[0139]

根据项(3)所述的固态成像元件,其中,所述像素形成为跨越设置有所述全局驱动部和所述滚动驱动电路的上芯片以及设置有所述滚动驱动电路的下芯片。

[0140]

(5)

[0141]

根据项(4)所述的固态成像元件,

[0142]

其中,所述全局驱动电路布置在所述上芯片上的所述像素阵列区域的周边区域中,并且

[0143]

所述滚动驱动电路布置在所述下芯片上的所述像素阵列区域的周边区域中。

[0144]

(6)

[0145]

根据项(4)所述的固态成像元件,

[0146]

其中,所述滚动驱动电路布置在所述上芯片上的所述像素阵列区域的周边区域中,并且

[0147]

所述全局驱动电路布置在所述下芯片上的所述像素阵列区域的周边区域中。

[0148]

(7)

[0149]

根据项(4)至(6)中任一项所述的固态成像元件,其中,所述全局驱动电路形成为跨越所述上芯片和所述下芯片。

[0150]

(8)

[0151]

根据项(7)所述的固态成像元件,

[0152]

其中,形成所述全局驱动电路的n型晶体管布置在所述上芯片上,并且

[0153]

形成所述全局驱动电路的p型晶体管布置在所述下芯片上。

[0154]

(9)

[0155]

根据项(1)至(8)中任一项所述的固态成像元件,

[0156]

其中,所述全局驱动部包括形成所述像素的光电二极管、排出晶体管和传输晶体管,并且

[0157]

所述滚动驱动部包括形成所述像素的读出晶体管和选择晶体管。

[0158]

(10)

[0159]

根据项(1)至(9)中任一项所述的固态成像元件,

[0160]

其中,所述像素包括用于对所述像素内部的模拟像素信号进行ad转换并输出数字像素信号的比较器和计数器,

[0161]

所述全局驱动部包括形成所述像素的光电二极管、排出晶体管和传输晶体管,并且

[0162]

所述滚动驱动部包括形成所述像素的锁存器。

[0163]

(11)

[0164]

一种电子设备,包括:

[0165]

固态成像元件,其包括:

[0166]

像素,其具有同时驱动所有行的全局驱动部和在相应的时刻驱动各行的滚动驱动部;

[0167]

像素阵列区域,其中多个所述像素布置成阵列;

[0168]

全局驱动电路,其被构造为向所述全局驱动部提供驱动信号;和

[0169]

滚动驱动电路,其被构造为向所述滚动驱动部提供驱动信号,

[0170]

其中,所述全局驱动电路布置在围绕所述像素阵列区域的四边中的至少三边以上的每个边上。

[0171]

注意,本实施方案不限于上述实施方案,并且可以在不脱离本公开的主旨的情况下进行各种变形。此外,这里所述的效果仅是示例性的而非限制性的,并且可以提供其他效果。

[0172]

[附图标记列表]

[0173]

11:成像元件

[0174]

12:芯片

[0175]

12a:上芯片

[0176]

12b:下芯片

[0177]

21a和21b:像素阵列区域

[0178]

22:全局驱动电路

[0179]

23:配线

[0180]

24:电源焊盘

[0181]

25:滚动驱动电路

[0182]

26:负荷mos区域

[0183]

27:ad转换单元

[0184]

28:水平传输电路

[0185]

31:像素

[0186]

31a:上像素

[0187]

31b:下像素

[0188]

41和42:放大器

[0189]

51:光电二极管

[0190]

52:排出晶体管

[0191]

53:传输晶体管

[0192]

54:存储器

[0193]

55:读出晶体管

[0194]

56:fd单元

[0195]

57:放大晶体管

[0196]

58:选择晶体管

[0197]

59:复位晶体管

[0198]

61:恒流源

[0199]

71a:n型晶体管

[0200]

71b:p型晶体管

[0201]

81:比较器

[0202]

82:计数器

[0203]

83:锁存器。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。