1.本发明涉及电路版图设计领域,具体是一种基于wifi4正交信号发生器版图设计结构。

背景技术:

2.正交信号发生器是电子技术领域中最基本的电子仪器,广泛应用于通信系统、电子对抗、电子测量、科研教学等领域,随着电子信息技术的发展,对其性能要求也越高,版图布局是否合理直接影响其性能指标。版图布局不合理,带来的额外rc寄生效应再加上工艺引起的失配,给阵列电路的时钟、电源的布线带来不利影响,继而影响像素单元电路的一致性和抗干扰能力。

技术实现要素:

3.本发明的目的在于提供一种基于wifi4正交信号发生器版图设计结构,提高版图的精度,减小rc寄生,保证正交信号发生器工艺角度的匹配,以解决上述背景技术中提出的问题。

4.为实现上述目的,本发明提供如下技术方案:

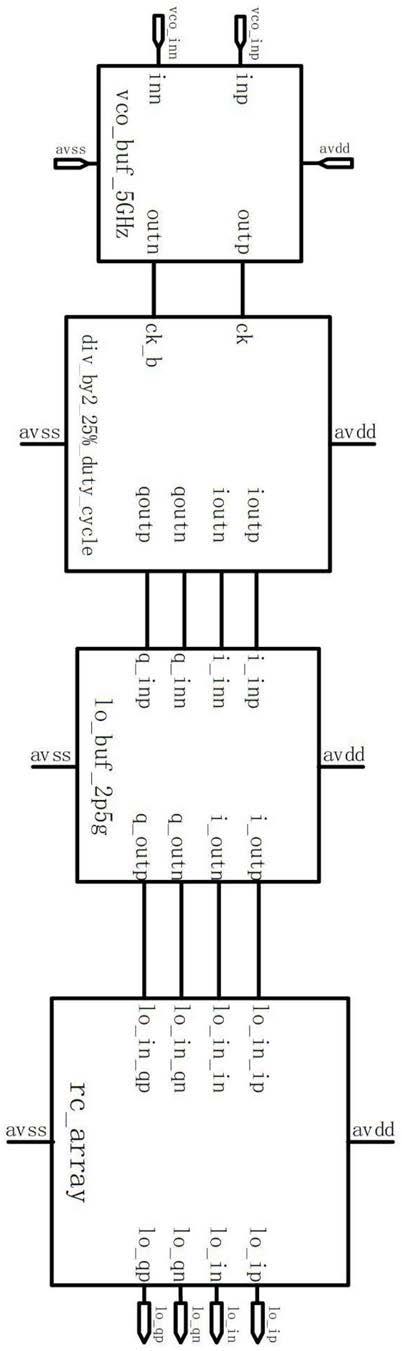

5.一种基于wifi4正交信号发生器版图设计结构,主要包含4个模块,vco_buf_5ghz,div_by2_25%_duty_cycle,lo_buf_2p5g,rc_array;整体布局水平对称,信号走向采用左近右出的方法,vco两路信号先经过vco_buf_5ghz模块提高驱动力,输出两路信号送给div_by2_25%_duty_cycle模块进行分频,产生四路lo信号,再经过lo_buf_2p5g模块提高驱动力,最后rc_array模块分别产生四路lo信号。

6.进一步的,其中vco_buf_5ghz模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,左进右出,直接输出给div_by2_25%_duty_cycle模块,大大缩短走线长度,减小rc寄生。

7.进一步的,其中div_by2_25%_duty_cycle模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,四路lo信号从模块中间输出,采用两两匹配的方式连接到lo_buf_2p5g,减小工艺失配。

8.进一步的,其中lo_buf_2p5g模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,产生的lo信号分别从模块的上下对称输出,采用45

°

的连线方式连接到rc_array,缩短走线长度,减小rc寄生。

9.进一步的,其中rc_array模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,确保i路和q路lo信号对称匹配。

10.本发明所述的一种基于wifi4正交信号发生器版图设计结构,电源地线以插指的形式上下分布,保证工艺差分对称;电源地线和时钟线设置为垂直相交,最大程度的减小电源地线和时钟线之间的寄生电容。

11.本发明的整体版图采用水平对称的布局方式,保证工艺差分对称,减小工艺引起

的信号失配;电源地线与时钟线和lo信号线设置为垂直相交,最大程度的减小电源地线和时钟线之间的寄生电容;从而达到提高正交信号发生器的性能的目标。

附图说明

12.图1为本发明的正交信号发生器电路图。

13.图2为本发明的正交信号发生器版图。

具体实施方式

14.下面结合具体实施方式对本专利的技术方案作进一步详细地说明。

15.请参阅图1-2,一种基于wifi4正交信号发生器版图设计结构,具体电路如图1所示,主要包含4个模块,vco_buf_5ghz,div_by2_25%_duty_cycle,lo_buf_2p5g,rc_array。该设计结构包括以下内容:

16.1)如图2所示,从整体布局分析,信号走向上采用左近右出的方法,vco两路信号先经过vco_buf_5ghz模块提高驱动力,输出两路信号送给div_by2_25%_duty_cycle模块进行分频,产生四路lo信号,再经过lo_buf_2p5g模块提高驱动力,最后rc_array模块分别产生四路lo信号;整体布局水平对称,电源地线以插指的形式上下分布,保证工艺差分对称。电源地线和时钟线设置为垂直相交,最大程度的减小电源地线和时钟线之间的寄生电容。

17.2)其中vco_buf_5ghz模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,左进右出,直接输出给div_by2_25%_duty_cycle模块,大大缩短走线长度,减小rc寄生。

18.3)其中div_by2_25%_duty_cycle模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,四路lo信号从模块中间输出,采用两两匹配的方式连接到lo_buf_2p5g,减小工艺失配。

19.4)其中lo_buf_2p5g模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,产生的lo信号分别从模块的上下对称输出,采用45

°

的连线方式连接到rc_array,缩短走线长度,减小rc寄生。

20.5)其中rc_array模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,确保i路和q路lo信号对称匹配。

21.上面对本专利的较佳实施方式作了详细说明,但是本专利并不限于上述实施方式,在本领域的普通技术人员所具备的知识范围内,还可以在不脱离本专利宗旨的前提下作出各种变化。

技术特征:

1.一种基于wifi4正交信号发生器版图设计结构,其特征在于,包括4个模块,vco_buf_5ghz,div_by2_25%_duty_cycle,lo_buf_2p5g,rc_array;整体布局水平对称,信号走向采用左近右出的方法,vco两路信号先经过vco_buf_5ghz模块提高驱动力,输出两路信号送给div_by2_25%_duty_cycle模块进行分频,产生四路lo信号,再经过lo_buf_2p5g模块提高驱动力,最后rc_array模块分别产生四路lo信号。2.根据权利要求1所述的一种基于wifi4正交信号发生器版图设计结构,其特征在于,所述vco_buf_5ghz模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,左进右出,直接输出给div_by2_25%_duty_cycle模块,大大缩短走线长度,减小rc寄生。3.根据权利要求1所述的一种基于wifi4正交信号发生器版图设计结构,其特征在于,所述div_by2_25%_duty_cycle模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,四路lo信号从模块中间输出,采用两两匹配的方式连接到lo_buf_2p5g,减小工艺失配。4.根据权利要求1所述的一种基于wifi4正交信号发生器版图设计结构,其特征在于,所述lo_buf_2p5g模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,产生的lo信号分别从模块的上下对称输出,采用45

°

的连线方式连接到rc_array,缩短走线长度,减小rc寄生。5.根据权利要求1所述的一种基于wifi4正交信号发生器版图设计结构,其特征在于,所述rc_array模块采用水平对称的布局方式,保证工艺差分对称,减小工艺引起的信号失配,确保i路和q路lo信号对称匹配。6.根据权利要求1所述的一种基于wifi4正交信号发生器版图设计结构,其特征在于,电源地线以插指的形式上下分布,保证工艺差分对称。7.根据权利要求1所述的一种基于wifi4正交信号发生器版图设计结构,其特征在于,电源地线和时钟线设置为垂直相交,最大程度的减小电源地线和时钟线之间的寄生电容。

技术总结

本发明公开了一种基于wifi4正交信号发生器版图设计结构,包括vco_buf_5GHz,div_by2_25%_duty_cycle,lo_buf_2p5g,rc_array;信号走向采用左近右出的方法,vco两路信号先经过vco_buf_5GHz模块提高驱动力,输出两路信号送给div_by2_25%_duty_cycle模块进行分频,产生四路lo信号,再经过lo_buf_2p5g模块提高驱动力,最后rc_array模块分别产生四路lo信号。本发明的为水平对称的布局结构,保证工艺差分对称,减小工艺引起的信号失配;电源地线与时钟线设置为垂直相交,最大程度的减小电源地线和时钟线之间的寄生电容。和时钟线之间的寄生电容。和时钟线之间的寄生电容。

技术研发人员:袁立凯 张妮娜 郑雷 尹莉 周旸 庞坚

受保护的技术使用者:芯河半导体科技(无锡)有限公司

技术研发日:2022.01.05

技术公布日:2022/4/15

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。