一种camellia算法p函数的硬件电路及优化方法

技术领域

1.本发明属于camellia算法技术领域,更具体地,涉及一种camellia算法p函数的硬件电路及优化方法。

背景技术:

2.随着高速无线通信网和物联网的发展,各类通信设备和处理终端逐渐朝着轻量化、智能化方向发展。轻量级设备的普及对密码算法提出了更高的要求,首先,资源受限装置需提供安全的加解密功能;其次,加解密电路面积必须尽可能小。因此,密码算法的优化实现越来越重要。camellia是一种常用的分组密码算法,由三菱和日本电信电话(ntt)于2000年共同发明,具有较高的安全性强度,是欧盟nessie项目选定算法和日本cryptrec项目推荐算法,并于2005年正式成为iso/iec国际标准,广泛应用于网络通信加密领域。

3.现代分组密码一般包含线性部分和非线性部分。在研究分组密码的优化实现时,通常将密码算法线性部分表示成有限域f2上的二元矩阵,并通过搜索该矩阵的实现评估密码算法的实现代价。然而,上述方法并不适用于camellia算法。

技术实现要素:

4.针对现有技术的至少一个缺陷或改进需求,本发明提供了一种camellia算法p函数的硬件电路及优化方法,其实现p函数的异或门电路数是目前已知最少的,降低了整体密码算法硬件实现的成本及面积。

5.为实现上述目的,按照本发明的第一方面,提供了一种camellia算法p函数的硬件电路,camellia算法p函数的总输入信号为{x1,x2,x3,

……

,x

64

},总输出信号为{y1,y2,y3,

……

,y

64

},所述硬件电路包括四层电路,每层电路包括四个模块;

6.其中第一层电路的输入信号为:z1,z2,z3,z4,z5,z6,z7,z8,z1={x1,x2,

……

,x8},z2={x9,x

10

,

……

,x

16

},z3={x

17

,x

18

,

……

,x

24

},z4={x

25

,x

26

,

……

,x

32

},z5={x

33

,x

34

,

……

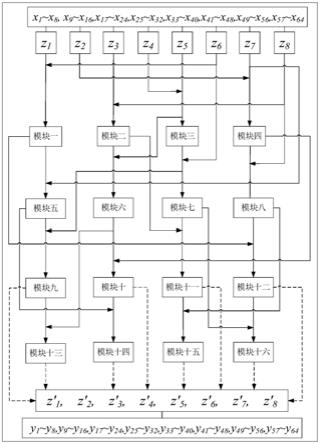

,x

40

},z6={x

41

,x

42

,

……

,x

48

},z7={x

49

,x

50

,

……

,x

56

},z8={x

57

,x

58

,

……

,x

64

},输出信号为:},输出信号为:},输出信号为:表示异或操作;

7.第二层电路的输入信号为:z5,z6,z7,z8,z9,z

10

,z

11

,z

12

,输出信号为:

8.第三层电路的输入信号为:z9,z

10

,z

11

,z

12

,z

13

,z

15

,z

18

,z

20

,输出信号为:z

22

,z

19

,z

14

,z

17

,并且z

22

,z

19

,z

14

,z

17

还作为所述硬件电路的输出信号,

9.第四层电路的输入信号为:z

13

,z

14

,z

15

,z

17

,z

18

,z

19

,z

20

,z

22

,输出信号为:z

23

,z

21

,z

16

,z

24

,并且z

23

,z

21

,z

16

,z

24

还作为所述硬件电路的输出信号,

10.进一步地,其中第一层电路包括第一模块、第二模块、第三模块和第四模块;

11.第一模块的输入信号为:x1,x2,x3,x4,x5,x6,x7,x8,x

41

,x

42

,x

43

,x

44

,x

45

,x

46

,x

47

,x

48

,输出信号为为为为

12.第二模块的输入信号为:x

17

,x

18

,x

19

,x

20

,x

21

,x

22

,x

23

,x

24

,x

57

,x

58

,x

59

,x

60

,x

61

,x

62

,x

63

,x

64

,输出信号为:,输出信号为:,输出信号为:

13.第三模块的输入信号为:x

25

,x

26

,x

27

,x

28

,x

29

,x

30

,x

31

,x

32

,x

33

,x

34

,x

35

,x

36

,x

37

,x

38

,x

39

,x

40

,输出信号为:为:为:

14.第四模块的输入信号为:x9,x

10

,x

11

,x

12

,x

13

,x

14

,x

15

,x

16

,x

49

,x

50

,x

51

,x

52

,x

53

,x

54

,x

55

,x

56

,输出信号为:,输出信号为:,输出信号为:

15.进一步地,第二层电路包括第五模块、第六模块、第七模块和第八模块;

16.第五模块的输入信号为:x

49

,x

50

,x

51

,x

52

,x

53

,x

54

,x

55

,x

56

,输出信号为:输出信号为:输出信号为:

17.第六模块的输入信号为:x

33

,x

34

,x

35

,x

36

,x

37

,x

38

,x

39

,x

40

,输出信号为:输出信号为:输出信号为:输出信号为:

18.第七模块的输入信号为:x

41

,x

42

,x

43

,x

44

,x

45

,x

46

,x

47

,x

48

,输出信号为:输出信号为:输出信号为:输出信号为:

19.第八模块的输入信号为:x

57

,x

58

,x

59

,x

60

,x

61

,x

62

,x

63

,x

64

,输出信号为:输出信号为:输出信号为:输出信号为:

20.进一步地,第三层电路包括第九模块、第十模块、第十一模块和第十二模块;

21.第九模块的输入信号为:为:输出信号为:为:为:为:

22.第十模块的输入信号为:第十模块的输入信号为:输出信号为:输出信号为:输出信号为:输出信号为:

23.第十一模块的输入信号为:第十一模块的输入信号为:输出信号为::::

24.第十二模块的输入信号为:输出信号为:号为:号为:

25.进一步地,第四层电路包括第十三模块、第十四模块、第十五模块和第十六模块;

26.第十三模块的输入信号为:第十三模块的输入信号为:输出信号为:为:为:为:

27.第十四模块的输入信号为:第十四模块的输入信号为:输出信号为:号为:号为:号为:

28.第十五模块的输入信号为:

输出信号为:号为:号为:号为:

29.第十六模块的输入信号为:第十六模块的输入信号为:输出信号为:号为:号为:号为:

30.进一步地,包括128个异或逻辑门。

31.按照本发明的第二方面,提供了一种camellia算法p函数的硬件电路的优化方法,包括步骤:

32.s1,将camellia算法p函数表示为64

×

64的二元矩阵,总输入信号为{x1,x2,x3,

……

,x

64

},总输出信号为{y1,y2,y3,

……

,y

64

},继而将camellia算法p函数表示为元素在有限域上的矩阵;

33.s2,优化有限域上矩阵的实现,包括子步骤:

34.s2.1,初始化异或操作的输入变量集合s,s={z1,z2,

…

,z8},z1={x1,x2,

……

,x8},z2={x9,x

10

,

……

,x

16

},z3={x

17

,x

18

,

……

,x

24

},z4={x

25

,x

26

,

……

,x

32

},z5={x

33

,x

34

,

……

,x

40

},z6={x

41

,x

42

,

……

,x

48

},z7={x

49

,x

50

,

……

,x

56

},z8={x

57

,x

58

,

……

,x

64

},继而将camellia算法p函数表示为元素在有限域上的矩阵;

35.s2.2,给出利用集合s中的元素生成矩阵输出变量的异或操作方案集合imp;

36.s2.3,遍历集合imp,消除其中的冗余异或操作;

37.s2.4,将经过步骤s2.3处理后的集合imp中的异或操作对应的矩阵实现深度为d,将集合imp中的异或操作按深度分为d个集合,从第二层开始,遍历之前的每一层,从中选择两个元素做异或,并将异或后得到的结果保存到集合s中,利用更新的集合s生成新的矩阵实现,若该实现消耗异或操作数较之前有所减少,则用新生成的矩阵实现替换集合imp,转到步骤s2.3,否则,若异或操作数并未减少,转到s2.5;

38.s2.5,将集合imp中的异或操作展开成关于输入变量{z1,z2,

……

,z8}的线性表达式,转到s2.6;

39.s2.6,重复执行步骤s2.1至s2.5预设次数,保留异或操作数最小的集合imp,作为有限域上矩阵的最优实现。

40.进一步地,一种camellia算法p函数的硬件电路的优化方法,还包括步骤:

41.s3,确定有限域上矩阵的最优实现后,确定camellia算法p函数的门级逻辑电路。

42.总体而言,本发明与现有技术相比,具有有益效果:

43.(1)本发明中异或门电路数是目前已知最少的,减少了camellia算法p函数的实现代价,进而降低了整体密码算法硬件实现的成本及面积。

44.(2)本发明的优化方法中,采用基于深度优先的框架,在搜索矩阵优化时,从当前深度出发,将之前所有深度中因异或操作产生的中间结果作为当前深度下异或门的可能输入信号,由此保证了本发明生成的矩阵优化实现电路深度较小。利用该框架,可以使得本发明得到的密码算法p函数优化实现电路的电路深度较优的同时,异或操作数也最小。

45.(3)本发明的优化方法中,调用启发式算法次数少,对启发式算法依赖性小,搜索过程速度更快,保证了本发明的高效性。

附图说明

46.图1是本发明实施例的camellia算法的f-函数流程图;

47.图2是本发明实施例的camellia算法p函数的实现中各层之间的关系图;

48.图3是本发明实施例的camellia算法p函数的实现电路图;

49.图4是本发明实施例的第一模块电路图;

50.图5是本发明实施例的第二模块电路图;

51.图6是本发明实施例的第三模块电路图;

52.图7是本发明实施例的第四模块电路图;

53.图8是本发明实施例的第五模块电路图;

54.图9是本发明实施例的第六模块电路图;

55.图10是本发明实施例的第七模块电路图;

56.图11是本发明实施例的第八模块电路图;

57.图12是本发明实施例的第九模块电路图;

58.图13是本发明实施例的第十模块电路图;

59.图14是本发明实施例的第十一模块电路图;

60.图15是本发明实施例的第十二模块电路图;

61.图16是本发明实施例的第十三模块电路图;

62.图17是本发明实施例的第十四模块电路图;

63.图18是本发明实施例的第十五模块电路图;

64.图19是本发明实施例的第十六模块电路图。

具体实施方式

65.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以相互组合。

66.图1所示为camellia密码算法更新函数(即f-函数)的流程图,本发明涉及的电路优化整个算法中的p-函数(即线性层)部分对应电路。

67.本发明的p-函数电路的得到方法为,将算法p-函数表示成元素在上的矩阵;优

化上矩阵的实现,列出上矩阵的实现关系图;列出camellia算法p-函数的门级逻辑电路图。

68.s1,将camellia算法p函数表示为64

×

64的二元矩阵,总输入信号为{x1,x2,x3,

……

,x

64

},总输出信号为{y1,y2,y3,

……

,y

64

},继而将camellia算法p函数表示为元素在有限域上的矩阵。

69.通过将密码算法p函数表示成二元域f2上的矩阵,继而利用既有启发式算法搜索矩阵的优化实现是目前探索密码算法p函数优化实现的主要手段。

70.camellia算法的更新函数中,p-函数可以表示成有限域f2上64

×

64的二元矩阵,该矩阵如下所示:

71.100000000000000010000000100000000000000010000000100000001000000001000000000000000100000001000000000000000100000001000000010000000010000000000000001000000010000000000000001000000010000000100000000100000000000000010000000100000000000000010000000100000001000000001000000000000000100000001000000000000000100000001000000010000000010000000000000001000000010000000000000001000000010000000100000000100000000000000010000000100000000000000010000000100000001000000001000000000000000100000001000000000000000100000001000000011000000010000000000000001000000010000000000000001000000010000000010000000100000000000000010000000100000000000000010000000100000000100000001000000000000000100000001000000000000000100000001000000001000000010000000000000001000000010000000000000001000000010000000010000000100000000000000010000000100000000000000010000000100000000100000001000000000000000100000001000000000000000100000001000000001000000010000000000000001000000010000000000000001000000010000000010000000100000000000000010000000100000000000000010000000110000000100000001000000000000000100000001000000000000000100000000100000001000000010000000000000001000000010000000000000001000000001000000010000000100000000000000010000000100000000000000010000000010000000100000001000000000000000100000001000000000000000100000000100000001000000010000000000000001000000010000000000000001000000001000000010000000100000000000000010000000100000000000000010000000010000000100000001000000000000000100000001000000000000000100000000100000001000000010000000000000001000000010000000000000001000000001000000010000000100000001000000010000000100000000000000000000000010000000100000001000000010000000100000001000000000000000000000000100000001000000010000000100000001000000010000000000000000000000001000000010000000100000001000000010000000100000000000000000000000010000000100000001000000010000000100000001000000000000000000000000100000001000000010000000100000001000000010000000000000000000000001000000010000000100000001000000010000000100000000000000000000000010000000100000001000000010000000100000001000000001000000010000000000000000000000000000000100000001000000010000000010000000100000000000000000000000000000001000000010000000100000000100000001000000000

0000000000000000000000100000001000000010000000010000000100000000000000000000000000000001000000010000000100000000100000001000000000000000000000000000000010000000100000001000000001000000010000000000000000000000000000000100000001000000010000000010000000100000000000000000000000000000001000000010000000100000000100000001000000000000000000000000000000010000000100000001000000001000000010000000000000001000000000000000100000001000000000000000010000000100000000000000010000000000000001000000010000000000000000100000001000000000000000100000000000000010000000100000000000000001000000010000000000000001000000000000000100000001000000000000000010000000100000000000000010000000000000001000000010000000000000000100000001000000000000000100000000000000010000000100000000000000001000000010000000000000001000000000000000100000001000000000000000010000000100000000000000010000000000000001000000010000000000000000100000001000000010000000100000000000000010000000000000000000000001000000010000000100000001000000000000000100000000000000000000000010000000100000001000000010000000000000001000000000000000000000000100000001000000010000000100000000000000010000000000000000000000001000000010000000100000001000000000000000100000000000000000000000010000000100000001000000010000000000000001000000000000000000000000100000001000000010000000100000000000000010000000000000000000000001000000010000000100000001000000000000000110000000000000000000000010000000100000001000000010000000000000000100000000000000000000000100000001000000010000000100000000000000001000000000000000000000001000000010000000100000001000000000000000010000000000000000000000010000000100000001000000010000000000000000100000000000000000000000100000001000000010000000100000000000000001000000000000000000000001000000010000000100000001000000000000000010000000000000000000000010000000100000001000000010000000000000000100000000000000000000000100000001000000010000000100000000

72.实现上述矩阵所需异或操作的数目即camellia算法p函数电路所耗异或逻辑门数目。然而,目前已知的优化矩阵实现的启发式算法搜索效率受限于矩阵大小和稠密度,具体来说,随着矩阵的维度和稠密度增加,算法生成矩阵实现方案的速度降低,这导致算法搜索矩阵优化实现的效率不高,也因此使得密码算法p函数实现代价的优化效果差强人意。由于上述原因,既有启发式算法中,只有paar提出的算法paar1和后来的学者对其进行改进后提出的算法rpaar1能快速的给出camellia算法p函数的优化实现方案,具体实现代价(异或门数)如下表所示:

73.表1算法paar1和rpaar1优化camellia算法p函数矩阵结果对比

74.优化前paar1rpaar1288176165

75.由图1所示流程图可知,camellia算法p函数的输入为(z1,z2,

…

,z8),其中camellia算法p函数的输出为(z

′1,z

′2,

…

,z

′8),其中由算法p-函数可知,其输入输出变量满足如下关系式:

[0076][0077][0078][0079][0080][0081][0082][0083][0084]

于是camellia算法p函数可以由元素属于上的矩阵表示如下,其中“1”对应f2上8

×

8的单位矩阵。

[0085][0086]

s2,优化有限域上矩阵的实现。

[0087]

将密码算法p函数表示成元素属于有限域的矩阵,通过优化上矩阵的实现构造算法p函数的优化实现方案。保持与图1所示算法p函数输入输出信号一致的符号,将矩阵的输入变量和输出变量分别记为(z1,z2,

…

,z8)和(z

′1,z

′2,

…

,z

′8),其中zi和z

′i均属于

[0088]

下面给出本发明优化上的矩阵的具体步骤。

[0089]

s2.1,初始化异或操作可能的输入变量组成的集合s。

[0090]

将异或操作可能的输入组成的集合记为s,s的初值为元素属于上矩阵的所有输入组成的集合,对于camellia算法p函数对应的矩阵,s={z1,z2,

…

,z8},其中转到s2.2。

[0091]

s2.2,给出利用集合s中的元素生成矩阵输出变量的异或操作方案集合imp。

[0092]

给出利用集合s中的元素{z1,z2,

…

,z8}生成矩阵输出变量(z

′1,z

′2,

…

,z

′8)的方案,记矩阵的实现为imp,imp是由一系列形如的操作组成的集合,矩阵的实现代价即集合imp中这类操作的数量。转到s2.3。

[0093]

此时集合imp中的操作方案可以是随机生成的,并非是最优异或操作方案集合,需要进行后续的步骤进行优化。

[0094]

s2.3,遍历集合imp,消除其中的冗余异或操作。

[0095]

由于硬件工艺库的不同,异或门有2-输入异或门和3-输入异或门,对应逻辑单元

的输入变量数分别为2和3。考虑到集合imp中的操作均由2-输入异或门实现,一方面,imp中的异或操作得到的结果可能存在重复,也就是说,存在两个不同的操作{b,c}和{d,e},的结果等于另一方面,在imp集合中,可能存在两个重复的异或操作,即,存在针对这两种情形,均删除重复的操作,仅保留其中之一,并根据删除的异或操作更新imp中剩余操作的操作数。转到s2.4。

[0096]

s2.4,初步优化集合imp中的操作数。

[0097]

设经过步骤s2.3处理后的集合imp中的异或操作对应的矩阵实现深度为d,将集合imp中的异或操作按深度分为d个集合。从第二层开始,遍历之前的每一层,从中选择两个元素做异或,并将异或后得到的结果保存到集合s中。利用更新的集合s生成新的矩阵实现(具体实现可和步骤s2.2相同),若该实现消耗异或操作数较之前有所减少,则用新生成的实现替换imp,转到步骤s2.3;否则,若异或操作数并未减少,转到s2.5。

[0098]

进一步地,s2.4包括子步骤:

[0099]

s2.4.1,根据深度d,将集合imp中的异或操作分为d个不同的集合,记为imp1,imp2,

…

,impd,impj(j=1,2,

…

,d)由一组形如的异或操作构成,对应矩阵实现中第j层所消耗的异或操作组成的集合,其中j=1,2,

…

,d。

[0100]

s2.4.2,假设当前层记为l(2≤l≤d),当前层之前的层为第1层一直到第l-1层,接着从这些层中的异或操作组成的集合imp1,imp2,

…

,imp

l-1

中遍历选择两个操作,将异或得到的结果加入到集合s中。集合s得到更新,利用更新后的s集合有可能找到矩阵异或数消耗更少的实现。

[0101]

s2.4.3,利用更新后的集合s生成矩阵实现,根据新生成的矩阵实现,比较该实现消耗的异或操作数与当前imp集合中异或操作总数,若新生成的实现所需异或操作较少,表明一种更优的实现已经找到,因此,用该实现替换掉当前的集合imp,由于矩阵实现得到更新,需重新开始优化过程,因此,转到s2.3;否则,若新生成的实现所需异或数并未减少,则表明矩阵实现并没有得到优化,此时如果第1层一直到第l-1层消耗的异或操作未被遍历完,继续遍历过程。如果上述遍历过程已结束,并且l《d,则令l=l 1并回到步骤s2.4.2,直至l=d,并且从所有小于d的层中遍历选择两个异或操作的过程完成为止。

[0102]

s2.5,进一步减少集合imp中的操作数。

[0103]

将集合imp中的异或操作展开成关于输入变量zi的线性表达式,其中设集合imp中异或操作的数量为n,则扩展之后可得到n个关于zi的线性表达式,n个表达式与矩阵的输入变量之间的关系可由矩阵表示,即得到一个n

×

8的矩阵,该矩阵中的元素为上的0或1,因此可以用既有的启发式算法搜索其优化实现。转到s2.6。

[0104]

既有启发式算法的搜索效率受到如矩阵大小、矩阵稠密度等因素的影响,过多的调用既有启发式算法在速度上并不一定占据优势;而在本发明实施例的搜索过程中,异或操作是展开成元素属于有限域的矩阵,并且,给定一种矩阵的实现。

[0105]

s2.6,重复上述步骤s2.1至s2.5预设次数,即重新生成新的集合imp,并对新的集合imp执行消除冗余异或操作和优化操作,最后保留异或操作数最小的集合imp,其对应的矩阵实现也最优。

[0106]

利用上述步骤,得到了如表2所示camellia算法p函数在上对应矩阵的优化实现,该实现由16个异或操作构成。

[0107]

表2 camellia算法p函数在上对应矩阵的实现

[0108][0109]

在目前被提出的搜索矩阵优化实现的启发式算法中,适用于优化维数小于64的矩阵的有paar1、rpaar1、bp、rnbp、a1以及a2,表3给出了上述启发式算法生成的矩阵实现所需异或操作数,其中第二行为上8x

×

8的矩阵的优化实现所需异或操作的数量。由于camellia算法p函数表示成上8

×

8的矩阵时,该矩阵由上的“0”和“1”构成,分别对应f2上8

×

8的零矩阵和8

×

8的单位矩阵,因此,上8

×

8矩阵的实现代价乘以8即该矩阵对应在f2上的矩阵的实现代价,如表3第三行所示,即camellia算法p函数硬件实现电路所需异或逻辑门的数量。

[0110]

表3现有启发式算法优化矩阵实现结果对比

[0111][0112]

由表2的实现可知,本发明涉及的上8

×

8矩阵的实现需要进行16次异或操作,对应16

×

8=128个异或逻辑门,比较表1和表3第三行的结果可知,本发明的camellia算法p函数硬件实现所需异或门数最少,为目前已知最优。

[0113]

如图2所示,camellia算法p函数在上对应矩阵的优化实现可以根据深度分为四层。

[0114]

(1)第一层的输入信号为:z1,z2,z3,z4,z5,z6,z7,z8,输出信号为:z9,z

10

,z

11

,z

12

。第一层需进行4次异或操作,分别为:一层需进行4次异或操作,分别为:

[0115]

(2)第二层的输入信号为:z5,z6,z7,z8,z9,z

10

,z

11

,z

12

,输出信号为:z

20

,z

18

,z

13

,z

15

。第二层需进行4次异或操作,分别为:。第二层需进行4次异或操作,分别为:

[0116]

(3)第三层的输入信号为:z9,z

10

,z

11

,z

12

,z

13

,z

15

,z

18

,z

20

,输出信号为:z

22

,z

19

,z

14

,z

17

,分别对应矩阵的输出信号z

′8,z

′6,z

′7,z

′5。第三层需进行4次异或操作,分别为:。第三层需进行4次异或操作,分别为:

[0117]

(4)第四层的输入信号为:z

13

,z

14

,z

15

,z

17

,z

18

,z

19

,z

20

,z

22

,输出信号为:z

23

,z

21

,z

16

,z

24

,分别对应矩阵的输出信号z

′1,z

′3,z

′4,z

′2。第四层需进行4次异或操作,分别为:。第四层需进行4次异或操作,分别为:

[0118]

s3、确定有限域上矩阵的最优实现后,确定camellia算法p函数的门级逻辑电路。

[0119]

由图1可知,camellia算法p函数的输入以字节为单位,因此,为了得到camellia算法p函数的门级逻辑电路,需将表2中的实现按比特展开。camellia算法p函数对应一个f2上64

×

64的二元矩阵,记该矩阵的输入信号为(x1,x2,

…

,x

64

),输出信号为(y1,y2,

…

,y

64

),则上述输入信号与图1所示基于字节的变量zi(i=1,2,

…

,8)之间的关系为:z1=(x1,x2,

…

,x8),z2=(x9,x

10

,

…

,x

16

),z3=(x

17

,x

18

,

…

,x

24

),z4=(x

25

,x

26

,

…

,x

32

),z5=(x

33

,x

34

,

…

,x

40

),z6=(x

41

,x

42

,

…

,x

48

),z7=(x

49

,x

50

,

…

,x

56

),z8=(x

57

,x

58

,

…

,x

64

)。上述输出信号与图1所示基于字节的变量z

′i(i=1,2,

…

,8)之间的关系为:z

′1=(y1,y2,

…

,y8),z

′2=(y9,y

10

,

…

,y

16

),z

′3=(y

17

,y

18

,

…

,y

24

),z

′4=(y

25

,y

26

,

…

,y

32

),z

′5=(y

33

,y

34

,

…

,y

40

),z

′6=(y

41

,y

42

,

…

,y

48

),z

′7=(y

49

,y

50

,

…

,y

56

),z

′8=(y

57

,y

58

,

…

,y

64

)。

[0120]

本发明利用图2所示camellia算法p函数的实现中各层之间的关系并根据表2所示上矩阵的优化实现中的异或操作将camellia算法p函数的实现分为十六个模块,其中模块一、模块二、模块三和模块四在同一层并行执行,模块五、模块六、模块七和模块八在同一层并行执行,模块九、模块十、模块十一和模块十二在同一层并行执行,模块十三、模块十四、模块十五和模块十六在同一层并行执行,对每一个模块的分析如下:

[0121]

(1)第一模块

[0122]

第一模块的输入字节为z1(p函数的输入)和z6(p函数的输入),输出字节为z9。即,

[0123]

第一模块的输入信号为:

[0124]

x1,x2,x3,x4,x5,x6,x7,x8,x

41

,x

42

,x

43

,x

44

,x

45

,x

46

,x

47

,x

48

.

[0125]

第一模块的输出信号为:

[0126][0127]

第一模块包括8个异或逻辑门,对应8个异或操作分别为:

[0128][0128]

[0129]

上述变量中,表示字节z9中的第i比特,i=1,2,

…

,8。

[0130]

(2)第二模块

[0131]

第二模块的输入字节为z3(p函数的输入)和z8(p函数的输入),输出字节为z

10

。即,

[0132]

第二模块的输入信号为:

[0133]

x

17

,x

18

,x

19

,x

20

,x

21

,x

22

,x

23

,x

24

,x

57

,x

58

,x

59

,x

60

,x

61

,x

62

,x

63

,x

64

.

[0134]

第二模块的输出信号为:

[0135][0136]

第二模块包括8个异或逻辑门,对应8个异或操作分别为:

[0137][0137][0138]

上述变量中,表示字节z

10

中的第i比特,i=1,2,

…

,8。

[0139]

(3)第三模块

[0140]

第三模块的输入字节为z4(p函数的输入)和z5(p函数的输入),输出字节为z

11

。即,

[0141]

第三模块的输入信号为:

[0142]

x

25

,x

26

,x

27

,x

28

,x

29

,x

30

,x

31

,x

32

,x

33

,x

34

,x

35

,x

36

,x

37

,x

38

,x

39

,x

40

.

[0143]

第三模块的输出信号为:

[0144][0145]

第三模块包括8个异或逻辑门,对应8个异或操作分别为:

[0146][0146][0147]

上述变量中,表示字节z

11

中的第i比特,i=1,2,

…

,8。

[0148]

(4)第四模块

[0149]

第四模块的输入字节为z2(p函数的输入)和z7(p函数的输入),输出字节为z

12

。即,

[0150]

第四模块的输入信号为:

[0151]

x9,x

10

,x

11

,x

12

,x

13

,x

14

,x

15

,x

16

,x

49

,x

50

,x

51

,x

52

,x

53

,x

54

,x

55

,x

56

.

[0152]

第四模块的输出信号为:

[0153][0154]

第四模块包括8个异或逻辑门,对应8个异或操作分别为:

[0155][0155][0156]

上述变量中,表示字节z

12

中的第i比特,i=1,2,

…

,8。

[0157]

(5)第五模块

[0158]

第五模块的输入字节为z7(p函数的输入)和z9(由第一模块生成),输出字节为z

20

。即,

[0159]

第五模块的输入信号为:

[0160]

x

49

,x

50

,x

51

,x

52

,x

53

,x

54

,x

55

,x

56

,

[0161]

第五模块的输出信号为:

[0162][0163]

第五模块包括8个异或逻辑门,对应8个异或操作分别为:

[0164][0164][0165]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8.

[0166]

(6)第六模块

[0167]

第六模块的输入字节为z5(p函数的输入)和z

10

(由第二模块生成),输出字节为z

18

。即,

[0168]

第六模块的输入信号为:

[0169]

x

33

,x

34

,x

35

,x

36

,x

37

,x

38

,x

39

,x

40

,

[0170]

第六模块的输出信号为:

[0171][0172]

第六模块包括8个异或逻辑门,对应8个异或操作分别为:

[0173][0173][0174]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0175]

(7)第七模块

[0176]

第七模块的输入字节为z6(p函数的输入)和z

11

(由第三模块生成),输出字节为z

13

。即,

[0177]

第七模块的输入信号为:

[0178]

x

41

,x

42

,x

43

,x

44

,x

45

,x

46

,x

47

,x

48

,

[0179]

第七模块的输出信号为:

[0180][0181]

第七模块包括8个异或逻辑门,对应8个异或操作分别为:

[0182][0182][0183]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0184]

(8)第八模块

[0185]

第八模块的输入字节为z8(p函数的输入)和z

12

(由第四模块生成),输出字节为z

15

。即,

[0186]

第八模块的输入信号为:

[0187]

x

57

,x

58

,x

59

,x

60

,x

61

,x

62

,x

63

,x

64

,

[0188]

第八模块的输出信号为:

[0189][0190]

第八模块包括8个异或逻辑门,对应8个异或操作分别为:

[0191][0191][0192]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0193]

(9)第九模块

[0194]

第九模块的输入字节为z

11

(由第三模块生成)和z

20

(由第五模块生成),输出字节为z

22

(z'8)。即,

[0195]

第九模块的输入信号为:

[0196][0197]

第九模块的输出信号为:

[0198][0199]

即y

57

,y

58

,y

59

,y

60

,y

61

,y

62

,y

63

,y

64

。

[0200]

第九模块包括8个异或逻辑门,对应8个异或操作分别为:

[0201][0201][0202]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0203]

(10)第十模块

[0204]

第十模块的输入字节为z

12

(由第四模块生成)和z

18

(由第六模块生成),输出字节为z

19

(z'6)。即,

[0205]

第十模块的输入信号为:

[0206][0207]

第十模块的输出信号为:

[0208][0209]

即y

41

,y

42

,y

43

,y

44

,y

45

,y

46

,y

47

,y

48

.

[0210]

第十模块包括8个异或逻辑门,对应8个异或操作分别为:

[0211][0211][0212]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0213]

(11)第十一模块

[0214]

第十一模块的输入字节为z

10

(由第二模块生成)和z

13

(由第七模块生成),输出字

节为z

14

(z'7)。即,

[0215]

第十一模块的输入信号为:

[0216][0217]

第十一模块的输出信号为:

[0218][0219]

即y

49

,y

50

,y

51

,y

52

,y

53

,y

54

,y

55

,y

56

.

[0220]

第十一模块包括8个异或逻辑门,对应8个异或操作分别为:

[0221]21][0222]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0223]

(12)第十二模块

[0224]

第十二模块的输入字节为z9(由第一模块生成)和z

15

(由第八模块生成),输出字节为z

17

(z'5)。即,

[0225]

第十二模块的输入信号为:

[0226][0227]

第十二模块的输出信号为:

[0228][0229]

即y

33

,y

34

,y

35

,y

36

,y

37

,y

38

,y

39

,y

40

.

[0230]

第十二模块包括8个异或逻辑门,对应8个异或操作分别为:

[0231][0231][0232]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8.

[0233]

(13)第十三模块

[0234]

第十三模块的输入字节为z

18

(由第六模块生成)和z

22

(由第九模块生成),输出字节为z

23

(z'1)。即,

[0235]

第十三模块的输入信号为:

[0236][0237]

第十三模块的输出信号为:

[0238][0239]

即y1,y2,y3,y4,y5,y6,y7,y8。

[0240]

第十三模块包括8个异或逻辑门,对应8个异或操作分别为:

[0241][0241]

[0242]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0243]

(14)第十四模块

[0244]

第十四模块的输入字节为z

19

(由第十模块生成)和z

20

(由第五模块生成),输出字节为z

21

(z'3)。即,

[0245]

第十四模块的输入信号为:

[0246][0247]

第十四模块的输出信号为:

[0248][0249]

即y

17

,y

18

,y

19

,y

20

,y

21

,y

22

,y

23

,y

24

。

[0250]

第十四模块包括8个异或逻辑门,对应8个异或操作分别为:

[0251][0251][0252]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0253]

(15)第十五模块

[0254]

第十五模块的输入字节为z

14

(由第十一模块生成)和z

15

(由第八模块生成),输出字节为z

16

(z'4)。即,

[0255]

第十五模块的输入信号为:

[0256][0257]

第十五模块的输出信号为:

[0258][0259]

即y

25

,y

26

,y

27

,y

28

,y

29

,y

30

,y

31

,y

32

。

[0260]

第十五模块包括8个异或逻辑门,对应8个异或操作分别为:

[0261][0261][0262]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0263]

(16)第十六模块

[0264]

第十六模块的输入字节为z

13

(由第七模块生成)和z

17

(由第十二模块生成),输出字节为z

24

(z'2)。即,

[0265]

第十六模块的输入信号为:

[0266][0267]

第十六模块的输出信号为:

[0268][0269]

即y9,y

10

,y

11

,y

12

,y

13

,y

14

,y

15

,y

16

。

[0270]

第十六模块包括8个异或逻辑门,对应8个异或操作分别为:

[0271][0271][0272]

上述变量中,表示字节zj中的第i比特,i=1,2,

…

,8。

[0273]

图3中所有模块均为异或门电路的集成,各模块的电路实现已由图4-19具体给出。由于各模块所需异或门电路总数达到目前已知最优,图4-19给出的电路实现降低了算法线性部件的实现代价。基于上述实现,本发明可以减少camellia算法p函数的实现成本以及面积,从而达到优化整体算法硬件实现的目的。

[0274]

本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。