1.本发明属于集成电路领域,具体来说,涉及一种包含过温保护及外部使能功能的电路结构。

背景技术:

2.为了避免温度过高导致器件损坏,在很多集成电路产品,特别是功率集成电路产品中,需要有过温保护功能,即在超过一定温度时使产品中大多数电路不工作。为了使集成电路产品拥有待机工作模式,很多集成电路产品需要有外部使能功能。很多电源类、功率类集成电路产品同时需要上述两种功能。

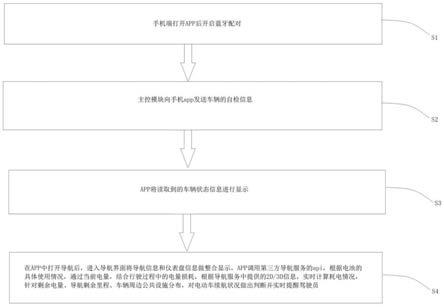

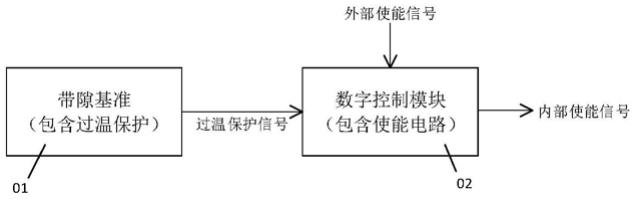

3.如图1所示,一种常用的包含过温保护及外部使能功能的系统构架。带隙基准01为其他模块提供零温度系数电压和正温度系数电流。带隙基准01包含过温保护功能,输出过温保护信号至数字控制模块02。数字控制模块02包含使能电路,接收过温保护信号和外部使能信号,在计算之后输出内部使能信号,用以使能或关闭其他功能模块。数字控制模块02通常用cmos构成,这是因为cmos器件静态功耗低、速度快、集成度高,适合用于具有一定规模的数字电路。

4.如图2所示,另一种常用的包含保护功能及外部使能功能的系统构架。过温保护功能被集成于保护模块04当中。保护模块04通常还包含过流保护、过压保护等功能。不包含过温保护功能的带隙基准03需要为保护模块04提供偏置,包括实现过温保护功能所必须的正温度系数电流。保护模块04输出过温保护信号至数字控制模块02。数字控制模块02接收包括过温保护信号在内的保护信号以及外部使能信号,在计算之后输出内部使能信号,用以使能或关闭其他功能模块。

5.如图1和图2所示,实现过温保护及外部使能功能可以有不同的系统构架,但通常都依赖带隙基准提供正温度系数电流,并且需要cmos数字电路进行计算并输出数字化的内部使能信号。对于部分集成电路产品,不需要带隙基准提供零温度系数电压,因此为了过温保护功能而采用带隙基准会造成功耗和芯片面积的浪费。对于部分集成电路产品,由于工艺限制(例如标准双极工艺、互补双极工艺)不包含cmos器件,无法实现静态功耗低、集成度高的数字控制模块。因此对于这些不需要带隙基准、不包含cmos器件,但又需要过温保护功能和外部使能功能的集成电路产品,需要设计一种电路结构,它同时包含过温保护功能和外部使能功能,并且不需要cmos器件的系统构架。

6.有鉴于此,特提出本发明。

技术实现要素:

7.本发明的目的是:解决现有过温保护及外部使能功能电路必须配套使用带隙基准及cmos数字电路,造成诸如不需要带隙基准或不包含cmos器件但又需要过温保护功能和外部使能功能的集成电路产品,采用带隙基准会造成功耗和芯片面积的浪费、无cmos器件又无法实现静态功耗低的问题。为了解决传统电路的问题,以简洁的、工艺适应性更强的电路

实现过温保护及外部使能功能,本发明提供一种不依赖cmos器件、不需要带隙基准的新型电路结构。

8.为此,本发明提供一种过温保护及使能控制电路,如图3所示,包括正温度系数电流产生电路11,使能控制电路12,使能信号输出电路13,迟滞电路14。

9.所述正温度系数电流产生电路11产生正温度系数电流,输入到使能控制电路12;使能控制电路12接收外部使能信号,输出过温信号经迟滞电路14产生迟滞信号给正温度系数电流产生电路11;使能控制电路12输出使能控制信号,经使能信号输出电路13,输出内部使能信号。

10.所述温保护及使能控制电路,电流源可采用npn、pnp电流镜,也可采用jfet电流源等不同方式实现。

11.所述温保护及使能控制电路,其中包含的任意二极管均可采用基极和集电极短接的npn或pnp替代。

12.所述温保护及使能控制电路,其使能控制电路和使能信号输出电路可以进行镜像设计,使外部使能信号和内部使能信号分别为高电平或低电平有效。

13.所述温保护及使能控制电路,可以在外部使能信号输入处增加元器件,以调解外部使能信号的阈值电压。

14.所述温保护及使能控制电路的运作原理如下:

15.正温度系数电流产生电路11产生正温度系数电流,该电流流经电阻可以产生正温度系数电压。使能控制电路12接收正温度系数电流,在其内部电阻上产生正温度系数电压。当正温度系数电压超过一定阈值(称为过温电压阈值)时,使过温信号和使能控制信号发生跳变。使能控制电路12接收外部使能信号,并据此控制使能控制信号。外部使能信号不能改变过温信号。当正温度系数电流使使能控制电路12中正温度系数电压超过过温电压阈值时,或外部使能信号表征“使能无效”时,使能控制信号表征“使能无效”;否则,使能控制信号表征“使能有效”。使能信号输出电路13接收使能控制信号,并输出内部使能信号,用以使能或关闭部分或其他全部芯片内部电路。迟滞电路14接收过温信号,输出迟滞信号。正温度数电流产生电路11接收迟滞信号。当迟滞信号有效时,正温度系数电流增大,进而使使能控制电路12的内部正温度系数电压增大。因此,当发生芯片过温时,芯片温度必须降至比过温阈值更低才能使芯片恢复正常工作状态。这种现象称为“迟滞”,迟滞现象有利于芯片的可靠性。当且仅当正温度系数电流使使能控制电路12中的正温度系数电压超过过温电压阈值时,过温信号有效。当且仅当过温信号有效时,迟滞信号有效。

16.与现有技术相比,本发明的有益效果为:

17.电路结构简单,有源器件仅包含npn、pnp、二极管,不包含任何nmos、pmos器件,适用于标准双极、互补双极、bicmos、bcd等多种工艺。

18.本发明所述的技术方案,广泛应用于不需要带隙基准、不包含cmos器件,但又需要过温保护功能和外部使能功能的集成电路产品领域。

附图说明

19.图1是一种传统的过温保护及使能电路系统结构示意图。

20.图2是另一种传统的过温保护及使能电路系统结构示意图。

21.图3是本发明过温保护及使能控制电路系统结构示意图。

22.图4是本发明正温度系数产生电路结构示意图。

23.图5是本发明使能控制电路结构示意图。

24.图6是本发明使能信号输出电路结构示意图。

25.图7是本发明过温保护及使能电路的一种电路原理示意图。

26.图8是本发明过温保护及使能电路的一种具体电路结构示意图。

具体实施方式

27.结合图3-图8,对本发明的实施例详述如下:

28.如图3所示,本发明的电路系统包含4个部分,即正温度系数电流产生电路11,使能控制电路12,使能信号输出电路13,迟滞电路14。

29.如图4所示,正温度系数电流产生电路11可由电流源i1,npn器件n1、n2、n3、n4,以及电阻r1构成。

30.如果n1、n2、n3、n4的发射极面积比例为n1:n2:n3:n4,则正温度系数电流等于其中k为玻尔兹曼常数,t为热力学温度,q为元电荷,r1为图4中电阻元件r1的阻值。显然,正温度系数电流与电流源i1的电流大小无关,并且正温度系数电流与热力学温度成正比。

31.如图5所示,使能控制电路12可由电流源i2、i3,pnp器件p1、p2、p3,npn器件n5、n6,电阻r2、r3、r4,以及二极管器件d2构成。

32.en端口为外部使能端口。当en电压较低时,可将使能控制信号下拉至较低电压。此时芯片处于外部关断状态。当芯片供电电压正常,且不在外部关断状态时,称芯片处于外部使能状态。

33.当芯片温度较高时,正温度系数电流升高,导致r3两端电压升高至p1的开启电压(也即正温度系数电压升至过温电压阈值),此时p1的集电极输出电流,使r2两端电压升高导致n5开启。n5的集电极电流导致r4两端电压升高,使n6的基极电压降低,从而使n6的基极-发射极电压小于开启电压。此时如果芯片处于外部使能状态,由于n6的集电极没有电流,p3的集电极也不输出电流,故使能控制信号被电流源i3下拉至较低电压。使使能控制信号刚好被下拉的温度,称为过温保护温度。

34.合理的设计应是i2经p2镜像至p3集电极的电流大于i3的电流,故如果正温度系数电流没有大到使p1开启,则电流源i2经由p2镜像之后,使p3的集电极电流大于i3的电流。如果芯片处于外部使能状态,则使能控制信号会被p3的集电极电流上拉至较高电压。

35.当芯片处于外部使能状态,且芯片温度低于过温保护温度时,使能控制信号被上拉至较高电压;否则使能控制信号为较低电压。使能控制信号电压的高或低可用于控制使能信号输出电路。

36.如图6所示,使能信号输出电路13可由电流源i4,pnp器件p4、p5,以及npn器件n7、n8构成。

37.p5输出内部使能信号的方式为一种可选的输出方式。当p5输出上拉电流时,芯片功能关闭;当p5不输出电流时,芯片正常工作。vbias为芯片内部偏置电压。当使能控制信号

高于vbias时,i4的电流全部经n7流过,故n8的集电极没有电流,此时p5的集电极不输出电流,芯片正常工作;当使能控制信号低于vbias时,p5的集电极输出上拉电流,此时芯片受此信号控制的电路均不工作。

38.如图7所示,包含图4、图5、图6所示的正温度系数电流产生电路11、使能控制电路12、使能信号输出电路13的完整过温保护及使能电路的一种实施例的电路示意图,其中迟滞电路14由二极管d1构成。n3的集电极输出正温度系数电流。p3的集电极连接n7的基极、d2的阳极以及电流源i3的上端,此结点电压为使能控制信号。d1的阴极电压为过温信号,d1的电流为迟滞信号。p5的集电极输出内部使能信号。

39.当芯片温度较低时,n3的集电极电流较低,而r3两端的电压值等于n3的集电极电流乘以r3的阻值,通过参数调整使此时r3两端的电压值低于p1的开启电压,因此p1的集电极不输出电流。这导致r2两端电压为零,因此n5的集电极也不输出电流,故r4两端电压几乎为零,n6的基极电压约等于vcc电压,n6的发射极电压约等于vcc-v

ben6

,其中v

ben6

为n6的基极-发射极电压。这导致d1的正向电压小于其开启电压,因此电流源i2的电流全部从n6的发射极流过,经过p2的镜像,p3的集电极输出的电流值与电流源i2的电流值成一定比例。经过参数调整,使电流源i3的电流值小于p3的集电极输出的电流值,则此时如果外部使能端口en悬空,则p3的集电极电流会将n7的基极电压拉高至高于n8的基极电压vbias,从而使芯片进入使能有效状态。

40.当芯片温度较高时,n3的集电极电流升高至超过过温保护温度,导致r3两端电压升高至p1的开启电压,此时p1的集电极输出电流,使r2两端电压升高导致n5开启。n5的集电极电流导致r4两端电压升高,使n6的基极电压降低,从而使n6的基极-发射极电压小于开启电压,而d1的正向电压达到开启电压,因此电流源i2的电流全部从d1流过。由于n6的集电极没有电流,因此p3的集电极也不输出电流,故n7的基极电压被电流源i3下拉至低于vbias,芯片进入使能无效状态。

41.当芯片温度过高导致使能无效时,电流源i2的电流经由d1流入电阻r3和p1的基极,这使芯片必须要下降到更低的温度方能使p1关断从而进入使能有效状态。导致芯片从使能有效状态进入使能无效状态的温度为t1,导致芯片从使能无效状态恢复到使能有效状态的温度为t2,其中t1>t2。t1为保护温度,t1-t2称为迟滞温度。通过设置r3的阻值可以调整t1,通过设置i2的大小可以调整t2,以上调整均可在仿真软件中准确模拟。

42.二极管d1、d2可由能实现二极管功能的其他器件替代,如基极、集电极短接的npn或pnp。

43.r5是为了避免n5的基极电流过大导致器件可靠性降低。

44.p5的集电极为内部使能信号的输出结点,当使能有效时,p5的集电极不输出电流,此时芯片正常工作,过温保护及使能电路不影响芯片其他部分电路的工作;当使能无效时,p5的集电极输出上拉电流,受此信号控制的电路均不工作,芯片功耗也因此降到待机功耗。

45.n7的基极电压被与n8的基极电压vbias比较。当n7的基极电压比n8的基极电压高时,电流源i4的电流全部流过n7的发射极,因此n8、p4、p5均无电流,此时芯片为使能有效状态。当n7的基极电压比n8的基极电压低时,电流源i4的电流全部流过n8,经过p4的镜像,p5会输出上拉电流,此时芯片为使能无效状态。

46.如果芯片温度并未造成p1开启,则p3集电极正常输出电流。此时如果en端口悬空,

则n7的基极电压高于n8的基极电压,p5集电极无电流,芯片处于使能有效状态;如果en端口电压较高,d2处于反偏状态或正偏电压未导致导通状态,则en端口不会对电路造成影响,芯片同样处于使能有效状态;如果en端口电压较低,d2处于正向导通状态,则n7的基极电压仅比en端口电压高约0.7v,当en电压低于vbias-0.7v时,会导致芯片进入使能无效状态。

47.en使能/关断芯片的阈值电压可通过vbias电压进行调整。

48.en与过温保护信号使芯片进入使能无效状态的机制,实际上实现了析取的逻辑,即当且仅当en低于使能阈值或芯片过温时,芯片进入使能无效状态。

49.如图8所示,电流源i1由p6和r6构成,经由p7和n9镜像之后,电流源i2和i4分别由n10和n11构成。电流源i3由pjfet器件j1构成。电流源i3没有采用从n9镜像的npn电流源的原因是:如果i3采用npn,则当en电压很低时,该npn可能进入饱和区,p7的集电极电流可能全部从该npn的寄生器件上流过,从而影响n10和n11的正常工作。

50.d1和d2均由基极和集电极短接的npn构成。

51.n9和r7、r8、r9、r10生成vbias电压。

52.综上所述,本发明所述的过温保护及使能电路结构,实现了过温保护和外部信号使能功能,完全不采用mos器件,适用于标准双极、互补双极、bicmos、bcd等包含npn、pnp器件的工艺。由于不包含带隙基准电路和数字电路,结构简单,特别适合于不需要带隙基准和数字电路控制的功率型集成电路,如功率运算放大器等。

53.需要说明的是,以上所述的实施方案应理解为说明性的,而非限制本发明的保护范围,本发明的保护范围以权利要求书为准。本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。