1.本发明涉及集成电路设计领域,尤其涉及一种带预充电功能的低功耗电源系统及其控制方法。

背景技术:

2.低功耗产品应用中,电源系统通常会带有dcdc(直流转直流电压转化器)模块来节省功耗,电源系统还会带有睡眠唤醒功能,当系统无需工作时,电源系统可掉电部分掉电,最大限度的节省功耗。

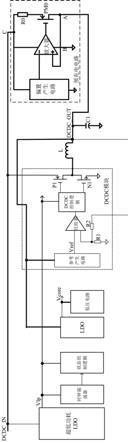

3.传统的带dcdc模块的低功耗电源睡眠唤醒系统,如图1所示,假设芯片供电电压为vdd,当芯片正常工作时,芯片供电输入dcdc_in分别给超低功耗ldo(低压差线性稳压器)与集成dcdc模块供电,低功耗ldo输出为vlp,为不掉电模块供电,dcdc模块输出通过电感l和电容c1滤波后降压为dcdc_out,假设电压值为v1,dcdc_out一方面给dcdc模块提供反馈信号接到内部电阻r2,另一方面给集成ldo提供供电电压,ldo输出为vcore,为低压电路供电。vlp下的时钟振荡器提供计时时钟,状态控制逻辑用于控制芯片各个模块的开启与关闭。当芯片进入睡眠状态时,dcdc模块关闭,p1、n1管处于关闭状态,dcdc_out处于放电状态,电容c1上的电压下降为0,即此时ldo的供电电压降低为0,ldo的输出vcore也将降为0,系统达到低功耗睡眠状态。当系统需要重新唤醒时,由于ldo和dcdc模块内部的参考产生等电路的供电此时为0,所以根据超低功耗下的不掉电控制逻辑,首先必须将dcdc模块的pmos管p1打开,通过电感对片外电容c1进行充电至vdd,然后再打开ldo和dcdc模块,此时dcdc才能正常工作,输出dcdc_out逐渐由vdd下降到v1。

4.如图2所示,0到t1时刻,芯片处于正常工作状态,dcdc_out为,ldo输出电压vcore为v2,芯片工作电流为i1;t1到t2时刻,芯片处于睡眠状态,dcdc_out由v1下降到0,ldo输出电压由v2下降到0,芯片睡眠电流为i2,i2由不可掉电部分工作电流组成;t2到t3时刻,芯片处于唤醒状态,dcdc_out由0上升到供电电压vdd,ldo输出电压由0上升到v2,芯片电流由i2迅速上升到i3,假设p1导通电阻为r,忽略电感与电容的作用,i3约等于;t3到t4时刻,dcdc_out逐渐由vdd下降到v1,ldo输出电压保持v2不变,芯片电流由i3迅速下降到i4,i4为dcdc未开启时的芯片电流;t4时刻后,dcdc输出v1,芯片恢复正常工作状态。

5.但是,这种低功耗电源系统的睡眠唤醒过程存在以下几个缺点:1、唤醒过程中,电流i3由电源电压和p1导通电阻决定,过大的脉冲电流大小会影响到电子产品的emi电磁干扰规范认证。

6.2、在反复的睡眠与唤醒过程中,电容c1上的电荷反复的被充放,这些能量并没有被电路所消耗,为无用功耗,增加了产品的平均功耗。

7.3、dcdc模块在t2到t4时刻,没有工作,没有起到降低功耗的作用。

技术实现要素:

8.发明目的:为了解决现有技术中低功耗电源系统在睡眠后的唤醒过程中,充电脉冲电流过大导致电磁干扰、以及造成额外功耗损失的问题,本发明提供一种带预充电功能的低功耗电源系统及其控制方法。

9.技术方案:一种带预充电功能的低功耗电源系统,包括超低功耗ldo模块、dcdc模块、lc滤波器、ldo模块及预充电电路,所述超低功耗ldo模块、dcdc模块、lc滤波器、ldo模块依次连接,所述预充电电路包括偏置产生电路、放大器、限流元件及开关管,系统供电电压为偏置产生电路及放大器供电,偏置产生电路输出端连接放大器反相输入端,开关管输入端通过限流元件连接系统供电电压,开关管输出端连接放大器同相输入端和lc滤波器的输出端,开关管的驱动端连接放大器输出端。

10.进一步地,所述放大器的供电负端连接最低电位或lc滤波器的输出端。

11.进一步地,所述限流元件为电阻,所述开关管为第一pmos管,第一pmos管的输入端为源极,第一pmos管的输出端为漏极,第一pmos管的驱动端为栅极。

12.进一步地,所述放大器为差分电压放大器,所述偏置产生电路包括第二pmos管和第三pmos管,第二pmos管的栅极与放大器的偏置端均连接超低功耗ldo输出的偏置电压,第二pmos管漏极与第三pmos管源极连接放大器反相输入端,第二pmos管源极接系统供电电压,第三pmos管栅极连接超低功耗ldo输出电压,第三pmos管漏极接地。

13.进一步地,ldo模块、dcdc模块开启时,预充电电路关闭;ldo模块、dcdc模块关闭时,预充电电路开启。

14.进一步地,还包括不掉电模块,所述不掉电模块连接超低功耗ldo的输出端。

15.一种上述带预充电功能的低功耗电源系统的控制方法,包括以下步骤:当从正常工作状态进入睡眠状态时,ldo模块及dcdc模块关闭,预充电电路开启;当从睡眠状态被唤醒,进入正常工作状态时,ldo模块及dcdc模块开启,预充电电路关闭。

16.本发明提供一种带预充电功能的低功耗电源系统及其控制方法,相比较现有技术,存在以下有益效果:1、在睡眠过程中,对电容进行预充电,使得输出电压近似正常工作时输出的电压值,电容上的电压几乎保持正常工作的输出电压不变,在唤醒时,无需对电容充电,直接打开ldo与dcdc模块,芯片即可进入正常工作状态。由于唤醒时不会对电容充电,不会产生过大的脉冲电流,因此不会影响到电子产品的emi电磁干扰规范认证;2、由于电容上的电荷不会反复被充放,不会产生多余的无用功耗,降低了产品的平均功耗;3、dcdc模块从唤醒时刻起就打开工作,直到开始进入睡眠状态,增加了dcdc模块工作的时长,进一步提升降低功耗的效果。

附图说明

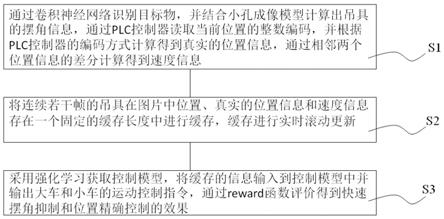

17.图1是传统的带dcdc模块的低功耗电源睡眠唤醒系统结构示意图;图2是芯片在睡眠唤醒和正常工作状态切换时节点的变化行为示意图;图3是实施例一带预充电功能的低功耗电源系统的示意图;

图4是实施例一预充电电路的一种具体电路的原理图;图5是实施例一中芯片在睡眠唤醒和正常工作状态切换时节点的变化行为示意图;图6是实施例二带预充电功能的低功耗电源系统的示意图。

具体实施方式

18.下面结合附图和具体实施例对本发明做进一步解释说明。

19.实施例一:如图3,一种带预充电功能的低功耗电源系统,包括超低功耗ldo模块、dcdc模块、lc滤波器、ldo模块及预充电电路,所述超低功耗ldo模块、dcdc模块、lc滤波器、ldo模块依次连接。系统供电电压dcdc_in为超低功耗ldo与dcdc模块供电,超低功耗ldo输出电压vlp,为不掉电模块及dcdc内的控制逻辑单元提供电压。dcdc模块的输出连接电感l与电容c1构成的lc滤波器,滤波后的电压为ldo模块供电,ldo模块输出vcore,为低压电路供电。

20.如图3中的预充电电路,所述预充电电路包括偏置产生电路、放大器、限流元件及开关管。在本实施例中,限流元件为电阻r0,开关管采用第一pmos管pm0,pm0的输入端为源极,pm0的输出端为漏极,pm0的驱动端为栅极。系统供电电压dcdc_in为偏置产生电路及放大器供电,偏置产生电路可产生一个与系统正常工作输出电压v1相近似的近似值vx,偏置产生电路输出端连接放大器反相输入端,第一pmos管pm0源极通过电阻r0连接系统供电电压dcdc_in,第一pmos管漏极连接放大器同相输入端及lc滤波器输出端(图中dcdc_out点),第一pmos管的栅极连接放大器输出端,放大器的供电负端连接最低电位gnd。

21.其中,偏置产生电路与放大器可以采用多种具体电路实现。本实施例中给出如图4的具体电路示例,所述放大器为差分电压放大器,由pm1、pm3、pm4、nm1、nm2组成。所述偏置产生电路包括第二pmos管pm2和第三pmos管pm5,pm2的栅极与放大器的偏置端(即e点)均连接超低功耗ldo产生的偏置电压,pm2漏极与pm5源极输出电压vx,通过设计pm5的尺寸使得偏置产生电路输出vx电压为vlp vth,且近似等于v1。vx连接放大器反相输入端,pm2源极接系统供电电压,pm5栅极(即d点)连接超低功耗ldo输出的电压vlp,pm5漏极接地。

22.该电源系统的控制方法,相比较现有技术,需要在进入唤醒状态时关闭ldo模块及dcdc模块,同时开启预充电电路,对lc滤波器中的电容c1进行预充电,使其上的电压基本保持在正常工作输出电压值。当电源系统从睡眠状态被唤醒时,预充电电路关闭,ldo模块与dcdc模块开启,直接进入正常工作状态,ldo模块与dcdc模块正常工作。

23.电阻r0的作用是避免pm0导通,运放还未正常工作时,dcdc_in与dcdc_out之间产生一个大的瞬时电流,这个瞬时电流不大于,vdd为系统供电电压值,v2为vcore在正常工作状态时的电压值。c点连接系统供电电源dcdc_in,b点连接了陈lc滤波器输出端dcdc_out,a点连接芯片最低电位gnd。当系统正常工作时,pm0关闭,充电支路不对电容c1进行充电。当系统进入睡眠状态,ldo关闭,dcdc模块关闭,由于实际电路关断电流不为0,假设关断电流大小为i0,此时电容c1上的电荷将缓慢泄露到gnd,电容c1上的电压将缓慢下降到0。在进入睡眠状态,关闭ldo和dcdc的同时,开启预充电电路,在预充电电路中的负反馈环路的作用下,dcdc_out将等于vx,预充电支路的电流大小将等于漏电电流大小i0,且随着i0

的变化而自适应变化,当芯片从睡眠状态切换至唤醒状态时,无需对电容c1进行充电,由于电容c1上的电压一直维持在近似dcdc正常工作时的输出电压,直接打开dcdc以及ldo,系统便可直接进入正常工作状态。

24.如图5所示,系统正常工作时,即0到t1时刻,dcdc模块输出电压为v1,ldo模块输出电压vcore,芯片电流为i1;系统进入睡眠状态时,即t1到t2时刻,ldo模块、dcdc模块关闭,预充电电路打开,dcdc_out被预充电至vx,约等于v1,此时芯片睡眠电流为i0 i2,实际设计中i0远小于i2;当芯片被唤醒时,t2时刻之后dcdc模块、ldo模块打开,预充电电路关闭,直接进入正常工作状态,dcdc模块、ldo模块正常工作。

25.图5相比较图2而言,系统在唤醒过程中,没有产生脉冲电流i3,从而保证了电子产品的emi电磁干扰规范认证,也避免了t2时刻到t4时刻,dcdc未开启而增加的额外功耗。由于电容c1在睡眠唤醒过程中,没有反复的充放电,从而节省了充放电带了的额外功耗损失,由于预充电电流i0远比芯片睡眠电流i2小,所以预充电电路并没有增加电源系统功耗。

26.实施例二:实施例二与实施例一相比,区别在于预充电电路中的b点不是连接最低电位gnd,而是同a端一样,连接到dcdc_out,如图6所示。这样放大器本身消耗的电流也可以成为预充电电流i0的一部分,进一步节省了电源系统的功耗。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。