1.本发明涉及执行事件处理的处理器和事件处理方法。

背景技术:

2.事件处理单元(epu:event processing unit)被用作代替主cpu执行各种事件处理的处理器(运算单元)。epu是如下结构:具有多个由程序计数器(pc)、通用寄存器等构成的硬件上下文(以下,称为线程),按照优先级选择线程,由1个运算装置执行与线程对应的序列(例如,参照专利文献1)。与线程对应的序列存储在程序存储器中,各线程的pc表示要执行的程序存储器上的位置(地址)。运算装置从所选择的线程的pc所表示的程序存储器的地址读入(获取(fetch))程序代码,执行与该代码对应的运算。

3.在epu中输入与各线程对应的事件。然后,各线程在被输入事件而有效化时,取得正在执行指令或请求执行指令的run(执行)状态和等待执行指令的wait(等待)状态。从run状态向wait状态的转变是根据线程所执行的指令产生的。关于从wait状态向run状态,在发生了向该线程输入的事件时或者经过了由内部计时器测量出的时间时发生。通过指令和事件输入来控制各线程的指令执行的开始和停止,在必要时进行执行必要的指令的动作。

4.使线程转变为wait状态的指令有evtwait指令。evtwait指令在操作数中具有输入事件编号。当执行evtwait指令时,该线程从run状态转变为wait状态,当发生与所指定的输入事件编号相应的事件时,从wait状态转变为run状态。

5.现有技术文献

6.专利文献

7.专利文献1:日本特开2019-101543号公报

技术实现要素:

8.发明要解决的课题

9.需要测量在执行evtwait指令后直到返回至run状态为止的时间。例如,在电源的负载较轻时,在进行间歇动作而实现低功耗化的电源系统所使用的epu中,通过基于evtwait指令的等待状态和基于来自输出电源电压的降低的检测机构的事件输入的重新开始动作来实现间歇动作。此时,有时通过测量从电源的等待到重新开始为止的时间,估计等待中的负载,并用于从间歇动作切换为通常动作的判定。

10.现状是在执行evtwait指令之前,使外部计时器启动,通过参考刚重新开始后的计时器的计数值,测量出从等待到重新开始为止的时间。在该方式中,除了消耗外部计时器资源之外,外部计时器的控制的工夫会直接影响线程的程序大小和执行时间。在有时也必须以几百ns执行控制循环的、要求严格的实时性的电源系统中,成为绝对无法忽视的处理时间。

11.本发明正是鉴于这样的问题而完成的,其目的在于提供一种能够在不消耗外部计时器资源的情况下实时地测量在执行evtwait指令之后直到返回至run状态为止的时间的

处理器和事件处理方法。

12.用于解决课题的手段

13.本发明的处理器和事件处理方法为了达成上述的目的,如下这样构成。

14.本发明的处理器根据指定了等候事件的事件等候指令,从正在执行指令或请求执行指令的执行状态转变为等待执行指令的等待状态,根据所述等候事件的发生,从所述等待状态转变为所述执行状态,该处理器的特征在于,具有:计时计数器,其从预先设定的初始值起开始计数;事件输入控制部,其检测对事件的发生进行通知的事件输入;等候事件检测部,其根据所述事件输入,检测所述等候事件;状态控制部,其根据所述事件等候指令,从所述执行状态转变为所述等待状态,并且输出对所述计时计数器指示计数开始的计数开始信号,随着检测出所述等候事件,从所述等待状态转变为所述执行状态,并且输出指示由所述计时计数器进行的计数结束的计数结束信号;以及测量值寄存器,其根据来自所述状态控制部的所述计数结束信号的输出,取入并保持所述计时计数器的计数值。

15.此外,本发明的事件处理方法是一种处理器的事件处理方法,该处理器根据指定了等候事件的事件等候指令,从正在执行指令或请求执行指令的执行状态转变为等待执行指令的等待状态,根据所述等候事件的发生,从所述等待状态转变为所述执行状态,该事件处理方法的特征在于,具有以下步骤:事件输入控制部检测对事件的发生进行通知的事件输入;等候事件检测部根据所述事件输入,检测所述等候事件;状态控制部根据所述事件等候指令,从所述执行状态转变为所述等待状态,并且输出计数开始信号,随着检测出所述等候事件,从所述等待状态转变为所述执行状态,并且输出计数结束信号;计时计数器根据来自所述状态控制部的所述计数开始信号的输出,从初始值起开始计数,并且根据来自所述状态控制部的所述计数结束信号的输出,结束计数;以及测量值寄存器根据来自所述状态控制部的所述计数结束信号的输出,取入并保持所述计时计数器的计数值。

16.发明效果

17.本发明的处理器起到如下效果:上位系统通过参考初始值以及测量值寄存器的计数值,能够在不消耗外部计时器资源的情况下,实时地测量在执行事件等候指令之后直到返回至执行状态的时间。

附图说明

18.图1是示出本发明的处理器的实施方式的结构的框图。

19.图2是说明图1所示的线程的状态转变的说明图。

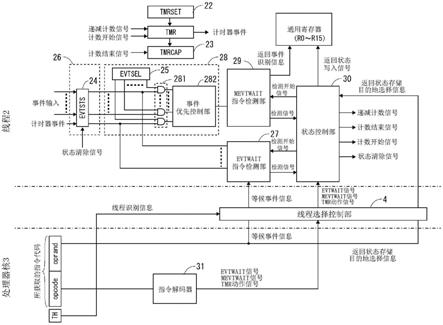

20.图3是示出图1所示的处理器核、线程选择控制部以及线程内的事件控制部的详细结构的框图。

21.图4是示出伴随wait期间的测量请求的基于evtwait指令的图1所示的处理器的动作的流程图。

22.图5是说明图1所示的计数计时器的动作的说明图。

23.图6是说明本发明的处理器的向电源系统的应用例的说明图。

24.图7是示出伴随wait期间的测量请求的基于mevtwait指令的图1所示的处理器的动作的流程图。

25.图8是说明图1所示的计数计时器的动作的说明图。

具体实施方式

26.下面,根据附图对本发明的优选实施方式进行说明。

27.本实施方式的处理器1是替代未图示的主cpu等上位系统执行各种事件处理的事件处理单元(epu:event processing unit),参照图1,具有2个线程2(20、21)、处理器核3、线程选择控制部4、系统总线受控器(bus slave)i/f 5、系统总线主控器(bus master)6、指令存储器访问i/f 7、数据存储器访问i/f 8和存储器9。另外,在本实施方式中,将线程2的数量设为了2个,但对线程2的数量未特别限制。

28.在线程2中,作为上下文,具有32比特的通用寄存器组r0~r15、存储64比特的运算的累计的存储区域acc、9比特的计数计时器tmr、设定计数计时器tmr的计数定时的设定区域prescaler、32比特浮动小数点运算(fpu)的动作模式以及状态的设定区域fpuflag/mode、堆栈指针sp、程序计数器pc、运算结果的进位标志c和比较结果保持区域t。此外,线程2除了上述的上下文以外,还具有事件控制部21,该事件控制部21控制输入事件以及输出事件。另外,线程2的结构要素除了本发明所必需的计数计时器tmr和事件控制部21以外,只要是通用的cpu的结构,则也可以采用任意的结构。

29.处理器核3由从存储器9获取指令代码的机构、解释所获取的代码是何种指令的指令解码器、运算器以及处理数据访问指令的机构构成。在处理器核3中,作为运算器,具有整数运算器int和浮动小数点运算器fpu。整数运算器int由加减法逻辑运算电路alu、比较电路cmp和乘法器mul构成,并且浮动小数点运算器fpu由加减法器add、除法器div和乘法器mul构成,依照指令将这些结构组合起来执行运算。

30.数据访问指令由寄存器间访问指令、存储器访问指令、系统总线访问指令构成。处理器核3根据寄存器间访问指令,经由线程选择控制部4进行寄存器之间的数据传输。此外,处理器核3根据存储器访问指令,经由数据存储器访问i/f 8进行从存储器9的读入以及向存储器9的写入。并且,处理器核3根据系统总线访问指令,经由系统总线主控器6进行对与系统总线10连接的各种外围模块的读入或写入。

31.线程选择控制部4按照优先级从来自各线程2(20、21)的指令执行请求中选择1个线程并将上下文传递至处理器核3。另外,优先级可以考虑预先设定的固定优先级(例如线程编号越小则优先级越高等)、轮次循环(通过使执行刚停止后的线程的优先级最低来使优先级在线程2之间循环的方式)、使固定优先级和轮次循环混合存在的方式等。

32.系统总线受控器i/f 5是线程2(20、21)与系统总线10之间的接口,对从主cpu等上位系统经由系统总线10的访问进行处理。上下文的初始设定、动作开始/停止以及向存储器的程序配置也是经由系统总线受控器i/f 5进行的。

33.系统总线主控器6是处理器核3与系统总线10之间的接口,具有按照由处理器核3发出的系统总线访问指令来控制对系统总线10的访问的功能。

34.指令存储器访问i/f 7是处理器核3与存储器9之间的接口,接收来自处理器核3的指令获取请求和获取地址,进行对存储器9的访问。

35.数据存储器访问i/f 8是处理器核3与存储器9之间的接口,依照由处理器核3发出的数据存储器访问指令,控制对存储器9的访问。此外,数据存储器访问i/f 8也对来自系统总线受控器i/f 5的存储器访问进行处理。因此,数据存储器访问i/f 8具有仲裁来自处理器核3和系统总线10的访问的功能。

36.存储器9是存储用于执行事件的程序以及数据的存储区域。在本实施方式中,将指令以及数据存储到1个存储器9中。而且,存储器9具有与指令存储器访问i/f 7连接的1个只读端口、和与数据存储器访问i/f 8连接的1个读写端口的共计2个端口。

37.参照图2,线程2在stop状态(停止状态)、正在执行指令或请求执行指令的run状态(执行状态)和等待执行指令的wait状态(等待状态)之间进行状态转变。stop状态的线程2不发出指令执行的请求而停止。在复位等初始化时,成为stop状态。run状态的线程2输出指令的执行的请求。由线程选择控制部4选择出的线程2接收指令执行请求,运算部(处理器核3)进行指令执行。wait状态的线程2临时使指令执行停止。

38.从stop状态向run状态的状态转变基于由主cpu等上位系统对控制寄存器的设定或来自其他线程2的有效化指令。此外,从run状态向wait状态的状态转变基于evtwait指令(事件等候指令)或mevtwait指令(多个事件等候指令)的执行。从wait状态向run状态的状态转变是基于了检测出等候事件的发生。从run状态向stop状态的状态转变和从wait状态向stop状态的状态转变是基于了由主cpu等上位系统对epu的控制寄存器的设定、来自其他线程2的无效化指令。

39.图3中示出了处理器核3、线程选择控制部4和线程2(事件控制部21)的详细结构。

40.处理器核3在未图示的指令获取机构中,从存储器9中获取由线程选择部选择出的线程的指令代码,并且将所选择的线程保持为线程识别信息。指令代码被分离为操作码(opcode)和操作数(oprand)。操作码表示指令的种类,操作数表示该指令所附带的数据、信息。处理器核3具有指令解码器31,指令解码器31对操作码进行解码,在指令代码是evtwait指令的情况下,输出表示是evtwait指令的evtwait信号,在指令代码是mevtwait指令的情况下,输出表示是mevtwait指令的mevtwait信号。此外,指令解码器31对操作码进行解码,在指令代码是请求wait状态的期间(以下,wait期间)的测量的指令代码的情况下,也输出表示使计数计时器tmr的动作有效的tmr动作信号。在是evtwait指令的情况下,操作数成为表示等候哪个事件的等候事件信息,在是mevtwait指令的情况下,操作数成为选择保存返回状态的寄存器的返回状态保存目的地选择信息。

41.线程选择控制部4根据线程识别信息来选择执行指令代码的线程2,将等候事件信息、evtwait信号、mevtwait信号、tmr动作信号和返回状态存储目的地选择信号传递至所选择的线程2。

42.线程2的事件控制部21具有tmrset寄存器22、tmrcap寄存器23、evtsts寄存器24和evtsel寄存器25,并作为事件输入控制部26、evtwait指令检测部27、mevtwait事件控制部28、mevtwait指令检测部29和状态控制部30发挥功能。

43.计数计时器tmr根据来自状态控制部30的计数开始信号,将tmrset寄存器22所设置的初始值加载为计数器值。对tmrset寄存器22的初始值的设置是从上位系统经由系统总线受控器i/f 5进行的。此外,也可以将初始值包含于指令代码的操作数中,对每个指令代码进行设置。

44.计数计时器tmr根据来自状态控制部30的递减计数信号,在prescaler所设定的递减计数定时,对计数器值进行递减计数。然后,当在递减计数信号中,计数器值成为0时,计数计时器tmr输出计时器事件。

45.tmrcap寄存器23根据来自状态控制部30的计数结束信号,取入计数计时器tmr的

计数器值。

46.evtsts寄存器24是对每个事件分配1比特的状态寄存器,作为检测所发生的事件的事件输入控制部26发挥功能。根据事件输入(事件的发生),evtsts寄存器24的相应的状态比特成为1,由此检测所发生的事件。另外,事件输入除了从外部功能模块的输入以外,还有从计数计时器tmr输出的计时器事件。根据从状态控制部输出的状态清除信号,evtsts寄存器24的相应的状态比特从1成为0,成为未检测到事件的状态。

47.evtwait指令检测部27根据来自状态控制部30的检测开始信号,等候与等候事件对应的evtsts寄存器24的状态比特成为1。然后,当检测到与等候事件对应的evtsts寄存器24的状态比特成为了1时,将检测信号输出至状态控制部30。

48.evtsel寄存器25是对每个事件分配1比特的状态寄存器,设定以mevtwait指令等候的多个事件。evtsel寄存器25的设定是从上位系统经由系统总线受控器i/f 5进行的。此外,也可以将evtsel寄存器25的设定包含于指令代码的操作数中,对每个指令代码进行设置。

49.evtsel寄存器25作为如下部件发挥功能:选择部281,其通过对evtsts寄存器24和evtsel寄存器25按照每个比特进行and运算,选择要等候的事件;事件优先控制部282,其进行同时检测多个要等候的事件的情况下的优先控制;以及mevtwait事件控制部28,其检测以mevtwait指令等候的事件的发生并输出至mevtwait指令检测部29。以下,将由mevtwait事件控制部28检测到的事件称作mevtwait事件。另外,关于由事件优先控制部282进行的优先控制,考虑有预先设定的固定优先级、轮次循环、使固定优先级和轮次循环混合存在的方式等。

50.mevtwait指令检测部29根据来自状态控制部30的检测开始信号,等候mevtwait事件控制部28检测出mevtwait事件。然后,mevtwait指令检测部29在由evtwait事件控制部28检测到mevtwait事件时,将检测信号输出至状态控制部30,并且将返回事件识别信息作为用于确定所检测到的mevtwait事件的信息输出至通用寄存器组r0~r15。

51.通用寄存器组r0~r15在从状态控制部30接收到指定了返回状态存储目的地(寄存器r0~r15中的任意寄存器)的返回状态写入信号时,将返回事件识别信息写入所指定的寄存器r0~r15中的任意寄存器。由此,通过在从mevtwait指令返回之后,确认返回事件识别信息,判别出在mevtwait指令之后能够以哪个事件返回,能够对返回后的处理进行切换。

52.状态控制部30根据evtwait信号,将检测开始信号输出至evtwait指令检测部27,使线程2从run状态转变为wait状态。然后,状态控制部30根据来自evtwait指令检测部27的检测信号,使线程2从wait状态转变为run状态而重新开始线程的指令执行,并且将状态清除信号输出至evtsts寄存器24。

53.状态控制部30根据mevtwait信号,将检测开始信号输出至mevtwait指令检测部29,使线程2从run状态转变为wait状态。然后,状态控制部30根据来自mevtwait指令检测部29的检测信号,使线程2从run状态转变为wait状态而重新开始线程的指令执行,并且将状态清除信号输出至evtsts寄存器24,将指定了返回状态存储目的地的返回状态写入信号输出至通用寄存器组r0~r15。

54.此外,状态控制部30在被输入了evtwait信号或mevtwait信号、以及tmr动作信号时,输出计数开始信号。然后,在wait状态的期间内,输出递减计数信号,并且在从wait状态

向run状态的转变时,输出计数结束信号。

55.接着,参照图4和图5,详细地说明伴随wait期间的测量请求的基于evtwait指令的处理器1的动作。

56.参照图4,处理器核3从由线程选择控制部4选择出的线程的程序计数器pc所表示的存储器地址中获取指令代码(步骤s101),并且将所选择的线程编号保持为线程识别信息。

57.接着,处理器核3的指令解码器31对操作码进行解码,将表示是evtwait指令的evtwait信号和表示使计数计时器tmr的动作有效的tmr动作信号输出至线程选择控制部4(步骤s102)。

58.此外,处理器核3将线程识别信息和操作数的等候事件信息输出至线程选择控制部4(步骤s103)。

59.接着,线程选择控制部4根据线程识别信息来选择执行指令代码的线程2,将等候事件信息传递至所选择的线程2的evtwait指令检测部27(步骤s104),并且将evtwait信号以及tmr动作信号传递至状态控制部30(步骤s105)。

60.接着,状态控制部30根据evtwait信号,将检测开始信号输出至evtwait指令检测部27,使线程2从run状态转变为wait状态(步骤s106)。

61.此外,状态控制部30根据tmr动作信号,将计数开始信号输出至计数计时器tmr,在wait状态的期间内,输出递减计数信号(步骤s107)。

62.根据计数开始信号,如图5所示,tmrset寄存器22所设置的初始值x作为计数值被加载到计数计时器tmr中。然后,计数计时器tmr的计数值根据在wait状态期间所输入的递减计数信号,在prescaler所设定的递减计数定时进行递减计数。

63.evtwait指令检测部27根据来自状态控制部30的检测开始信号,等候与等候事件对应的evtsts寄存器24的状态比特成为1、即等候事件的发生(步骤s108)。

64.当在步骤s108中,与等候事件对应的evtsts寄存器24的状态比特成为1时,evtwait指令检测部27将检测信号输出至状态控制部30(步骤s109)。

65.状态控制部30根据来自evtwait指令检测部27的检测信号,使线程2从wait状态转变为run状态,执行与evtwait指令对应的处理(步骤s110),并且将计数结束信号输出至tmrcap寄存器23(步骤s111),进而将状态清除信号输出至evtsts寄存器24(步骤s112),结束事件等候动作。

66.根据计数结束信号,如图5所示,在tmrcap寄存器23中取入计数结束信号的输入时的计数计时器tmr的计数器值y。由此,上位系统通过参考tmrset寄存器22以及tmrcap寄存器23的计数值,能够掌握wait期间。即,能够将对tmrset寄存器22的初始值x与tmrcap寄存器23中所取入的计数器值y 1的差值乘以递减计数周期而得的值测量为从evtwait指令的执行起到检测出等候事件为止的wait期间。另外,tmrcap寄存器23的复位定时也可以由上位系统适当设定。

67.在电源系统中,如图6所示,使电源的负载较轻时的pwm输出进行间歇动作而实现低功耗化。当在时刻t0检测到输出电流的降低时,识别为轻负载,使电源控制停止。然后,输出电压根据输出电容器的电荷容量而电压下降。然后,当在时刻t1,输出电压低于阈值电压v

th

时,重新开始电源控制而使输出电压恢复。通过该间歇动作,在电源控制停止期间,未发

生基于电源控制的开关动作,可以期待效率提高。

68.这样的间歇动作能够通过基于evtwait指令的wait状态和基于来自输出电压的降低的检测机构的事件输入的重新开始动作(run状态)来实现。在该情况下,在检测到输出电流的降低的时刻t0向处理器1输入将输出电压的到阈值电压v

th

为止的降低设为等候事件的evtwait指令,并转变为wait状态。

69.在检测到输出电压的到阈值电压v

th

为止的降低的时刻t1,检测等候事件。由此,测量时刻t0到时刻t1的电源控制停止期间作为wait期间,根据电源控制停止期间、下降电压和外部负载电容来估算停止期间中的消耗电流。因此,能够估计等待中的负载,并用于从间歇动作切换为通常动作的判定,能够进行提高轻负载时的效率的控制。

70.参照图7,处理器核3从由线程选择控制部4选择出的线程的程序计数器pc所表示的存储器地址中获取指令代码(步骤s201),并且将所选择的线程编号保持为线程识别信息。

71.接着,处理器核3的指令解码器31对操作码进行解码,将表示是mevtwait指令的mevtwait信号和表示使计数计时器tmr的动作有效的tmr动作信号输出至线程选择控制部4(步骤s202)。

72.此外,处理器核3将线程识别信息和操作数的返回状态存储目的地选择信息输出至线程选择控制部4(步骤s203)。

73.接着,线程选择控制部4根据线程识别信息来选择执行指令代码的线程2,将mevtwait信号以及tmr动作信号传递至状态控制部30(步骤s204)。另外,由上位系统在evtsel寄存器25中设定以mevtwait指令等候的多个mevtwait事件、以及计时器事件(步骤s205)。

74.接着,状态控制部30根据mevtwait信号,将检测开始信号输出至mevtwait指令检测部29,使线程2从run状态转变为wait状态(步骤s206)。

75.此外,状态控制部30根据tmr动作信号,将计数开始信号输出至计数计时器tmr,在wait状态的期间内,输出递减计数信号(步骤s207)。

76.根据计数开始信号,如图8所示,tmrset寄存器22所设置的初始值x作为计数值被加载到计数计时器tmr中。然后,计数计时器tmr的计数值根据在wait状态期间所输入的递减计数信号,在prescaler所设定的递减计数定时进行递减计数。

77.mevtwait指令检测部29根据来自状态控制部30的检测开始信号,等候mevtwait事件控制部28检测出mevtwait事件、即要等候的多个mevtwait事件中的任意事件的发生(步骤s208),并且等候mevtwait事件控制部28检测出计时器事件(步骤s209)。

78.当在步骤s208中由mevtwait事件控制部28检测到mevtwait事件时,mevtwait指令检测部29将检测信号输出至状态控制部30(步骤s210),并且将返回事件识别信息作为用于确定所检测到的mevtwait事件的信息输出至通用寄存器组r0~r15(步骤s211)。

79.状态控制部30根据来自mevtwait指令检测部29的检测信号,将指定了返回状态存储目的地的返回状态写入信号输出至通用寄存器组r0~r15(步骤s212)。由此,来自mevtwait指令检测部29的返回事件识别信息被写入由返回状态写入信号所指定的寄存器r0~r15中的任意寄存器。

80.然后,状态控制部30根据来自mevtwait指令检测部27的检测信号,使线程2从wait

状态转变为run状态,执行与mevtwait指令对应的处理(步骤s213)。在执行处理时,通过参考所指定的寄存器r0~r15中的任意寄存器中所写入的返回事件识别信息,能够根据所发生的事件,对处理进行切换。

81.接着,状态控制部30将计数结束信号输出至tmrcap寄存器23(步骤s214),进而将状态清除信号输出至evtsts寄存器24(步骤s215),结束事件等候动作。

82.根据计数结束信号,如图8的(a)所示,在tmrcap寄存器23中取入计数结束信号的输入时的计数计时器tmr的计数器值y。由此,上位系统通过参考tmrset寄存器22以及tmrcap寄存器23的计数值,能够掌握wait期间。即,能够将对tmrset寄存器22的初始值x与tmrcap寄存器23中所取入的计数器值y 1的差值乘以递减计数周期而得的值测量为从evtwait指令的执行起到检测出等候事件为止的wait期间。另外,tmrcap寄存器23的复位定时也可以由上位系统适当设定。

83.如图8的(b)所示,当计数计时器tmr的计数器值成为0而输出计时器事件、并且在步骤s209中由mevtwait事件控制部28检测到计时器事件时,mevtwait指令检测部29将检测信号输出至状态控制部30(步骤s216),并且将确定所检测到的计时器事件的返回事件识别信息输出至通用寄存器组r0~r15(步骤s217)。

84.状态控制部30根据来自mevtwait指令检测部27的检测信号,将指定了返回状态存储目的地的返回状态写入信号输出至通用寄存器组r0~r15(步骤s218)。由此,来自mevtwait指令检测部29的返回事件识别信息被写入由返回状态写入信号所指定的寄存器r0~r15中的任意寄存器。

85.然后,状态控制部30根据来自mevtwait指令检测部27的检测信号,使线程2从wait状态转变为run状态,执行与计时器事件对应的处理(步骤s219)。在执行处理时,通过参考所指定的寄存器r0~r15中的任意寄存器中所写入的返回事件识别信息,能够执行与计时器事件对应的处理。

86.接着,状态控制部30将状态清除信号输出至evtsts寄存器24(步骤s220),使事件等候动作结束。另外,状态控制部30也将计数结束信号输出至tmrcap寄存器23,但由于计数计时器tmr的计数器值成为0,因此tmrcap寄存器23中未产生变化。

87.由此,能够识别出根据mevtwait指令即使等待一定时间也没有发生正等待的等候事件的情况,并执行与不同于通常时的处理的计时器事件对应的处理。对tmrset寄存器22所设置的初始值x乘以递减计数周期而得的时间成为等待mevtwait事件的超时时间。

88.如以上所说明的那样,根据本实施方式,一种处理器1,其根据指定了等候事件的evtwait指令(事件等候指令),从正在执行指令或请求执行指令的run状态(执行状态)转变为等待执行指令的wait状态(等待状态),根据等候事件的发生,从wait状态转变为run状态,该处理器1的特征在于,具有:计时计数器tmr,其从初始值起开始计数;事件输入控制部26,其检测对事件的发生进行通知的事件输入;evtwait指令检测部27(等候事件检测部),其根据事件输入,检测等候事件;状态控制部30,其根据evtwait指令,从run状态转变为wait状态,并且输出对计时计数器tmr指示计数开始的计数开始信号,随着检测出等候事件,从wait状态转变为run状态,并且输出指示由计时计数器tmr进行的计数结束的计数结束信号;以及tmrcap寄存器23(测量值寄存器),其根据来自状态控制部30的计数结束信号的输出,取入并保持计时计数器tmr的计数值。

89.根据该结构,上位系统通过参考tmrset寄存器22(初始值)以及tmrcap寄存器23的计数值,能够掌握wait期间,并能够在不消耗外部计时器资源的情况下,实时地测量在执行evtwait指令之后直到返回至run状态为止的时间(wait期间)。

90.并且,在本实施方式中,状态控制部30根据指定了多个等候事件的mevtwait指令(多个事件等候指令),从run状态转变为wait状态,并且输出对计时计数器tmr指示计数开始的计数开始信号,随着mevtwait指令检测部29(等候事件检测部)检测出由mevtwait指令指定的多个等候事件中的任意事件,从wait状态转变为run状态,并且输出计数结束信号,该计数结束信号指示由计时计数器tmr进行的计数结束。

91.根据该结构,能够将多个事件指定为等候事件。

92.并且,在本实施方式中,计时计数器tmr在计数值达到设定值时,将计时器事件作为事件输入来输出,mevtwait指令检测部29将计时器事件检测为多个等候事件之一。

93.根据该结构,能够识别出即使等待一定时间也不发生等候事件的情况。

94.并且,本实施方式具有通用寄存器r0~r15(识别信息寄存器),该通用寄存器保持等候事件识别信息,该等候事件识别信息确定由mevtwait指令检测部29检测到的等候事件。

95.根据该结构,由于能够利用通用寄存器r0~r15所保持的等候事件识别信息,识别所发生的等候事件,因此能够根据发生的等候事件,对处理进行切换。

96.另外,本发明不限定于上述各实施方式,可知在本发明的技术思想的范围内,能够对各实施方式进行适当变更。另外,上述结构部件的数量、位置、形状等不限于上述实施方式,可以成为适合实施本发明的数量、位置、形状等。另外,在各图中,对相同结构要素标注相同标号。

97.标号说明

98.1:处理器;

99.2:线程;

100.3:处理器核;

101.4:线程选择控制部;

102.5:系统总线受控器i/f;

103.6:系统总线主控器;

104.7:指令存储器访问i/f;

105.8:数据存储器访问i/f;

106.9:存储器;

107.21:事件控制部;

108.22:tmrset寄存器;

109.23:tmrcap寄存器;

110.24:evtsts寄存器;

111.25:evtsel寄存器;

112.26:事件输入控制部;

113.27:evtwait指令检测部;

114.28:mevtwait事件控制部;

115.29:mevtwait指令检测部;

116.30:状态控制部;

117.31:指令解码器。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。