1.本实用新型属于电池技术领域,尤其涉及一种带隔离驱动的降压拓扑电路及电池管理系统。

背景技术:

2.新能源汽车逐步成为汽车工业的发展趋势,现有的新能源汽车电池缺乏一个合理可靠的bms管理系统,bms系统是指对电池进行管理和控制的系统,其中被管理和控制的电池可以包括锂电池组,也可以包括其它类型的电池组。锂电池充放电过程中,由于单体之间差异,电压容易出现不稳定的变化,很容易造成电池之间的电池电压不一致,造成某些单体过充或者过放,严重的影响电池寿命,故需要电池管理系统对单体电压进行管理。

技术实现要素:

3.本实用新型的目的在于提供一种带隔离驱动的降压拓扑电路,旨在解决现有技术中因电源输出的电压出现不稳定变化,而导致过充或过放、影响电池寿命的技术问题。

4.为实现上述目的,本实用新型实施例提供一种带隔离驱动的降压拓扑电路,包括电源输入电路,所述电源输入电路用于提供稳压直流电,降压拓扑输出电路,所述降压拓扑输出电路与所述电源输入电路连接,所述降压拓扑输出电路用于输出稳压直流电;隔离驱动电路,所述隔离驱动电路与所述降压拓扑输出电路连接,所述隔离驱动电路用于隔离所述电源输入电路与所述降压拓扑输出电路的信号;主控电路,所述主控电路与所述隔离驱动电路连接,所述主控电路用于控制所述隔离驱动电路的信号输出。

5.可选地,所述隔离驱动电路包括光耦隔离电路与驱动分离电路,所述光耦隔离电路与所述主控电路和驱动分离电路连接,所述驱动分离电路与所述降压拓扑输出电路连接。

6.可选地,所述光耦隔离电路包括光耦隔离器、第三三极管与第八三极管,所述光耦隔离器的输入端与所述主控电路连接,所述光耦隔离器的输出端与所述第三三极管和第八三极管连接,所述第三三极管和所述第八三极管与所述驱动分离电路连接。

7.可选地,所述驱动分离电路包括第一驱动分离电路、第二驱动分离电路、第三驱动分离电路和第四驱动分离电路,所述第一驱动分离电路、所述第二驱动分离电路、所述第三驱动分离电路和所述第四驱动分离电路均与所述第三三极管和第八三极管连接,所述第一驱动分离电路、所述第二驱动分离电路、所述第三驱动分离电路和所述第四驱动分离电路还与所述降压拓扑输出电路连接。

8.可选地,所述降压拓扑输出电路包括第一场效应管、第二场效应管、第三场效应管、第四场效应管和电流传感器,所述第一场效应管与所述第一驱动分离电路连接,所述第二场效应管与所述第二驱动分离电路连接,所述第三场效应管与所述第三驱动分离电路连接,所述第四场效应管与所述第四驱动分离电路连接,所述第一场效应管、所述第二场效应管、所述第三场效应管和所述第四场效应管均与所述电流传感器连接,所述电流传感器与

所述电源输出电路连接。

9.可选地,所述主控电路包括主控芯片与电平转换芯片,所述主控芯片与所述电源输入电路连接,所述主控芯片还与电平转换芯片连接,所述电平转换芯片与所述光耦隔离电路连接。

10.可选地,所述电源输入电路包括直流电源输入电路、辅助电源电路与驱动电源电路;所述直流电源输入电路与所述降压拓扑输出电路连接,所述辅助电源电路与所述驱动电源电路连接。

11.可选地,所述驱动电源电路包括驱动芯片、第一mos管、第二mos管、第一变压器与第三变压器;所述驱动芯片与所述辅助电源电路连接,所述驱动芯片与所述第一mos管与第二mos管连接,所述第一mos管与所述第一变压器连接,所述第一变压器与所述第三变压器连接,所述第三变压器与所述第二mos管连接。

12.可选地,所述辅助电源电路包括功率开关芯片、第二变压器与第三十二光耦,所述第二变压器与所述直流电源输入电路连接,所述第二变压器还与所述第三十二光耦的输入端连接,所述第三十二光耦的输出端与所述功率开关芯片连接,所述功率开关芯片与所述第二变压器连接。

13.本实用新型实施例提供的带隔离驱动的降压拓扑电路中的上述一个或多个技术方案至少具有如下技术效果之一:

14.本实用新型通过设置所述隔离驱动电路,使所述电源输入电路与降压拓扑输出电路隔离,能够有效防止电压出现不稳定跳变,减少输出信号对输入端造成的影响;还通过设置所述降压拓扑输出电路,有效控制电压降低,减少电压的波动,并提供稳定的电压输出。

15.一种电池管理系统,所述电池管理系统包括所述的带隔离驱动的降压拓扑电路,本实用新型实施例提供的电池管理系统中的上述一个或多个技术方案至少具有如下技术效果之一:

16.因所述电池管理系统包括所述具有电池保护电路,故所述电池管理系统亦能实现在使用过程中提供稳定电压输出的功能。

附图说明

17.为了更清楚地说明本实用新型实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

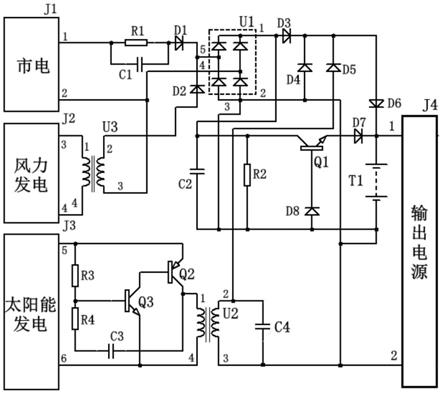

18.图1为本实用新型实施例提供的带隔离驱动的降压拓扑电路及电池管理系统的电路原理图;

19.图2为本实用新型实施例提供的电源输入电路的电路原理图;

20.图3为本实用新型实施例提供的降压拓扑输出电路的电路原理图;

21.图4为本实用新型实施例提供的采样保护电路的电路原理图;

22.图5为本实用新型实施例提供的主控电路的电路原理图;

23.图6为本实用新型实施例提供的隔离驱动电路的电路原理图。

24.其中,图中各附图标记:

25.电源输入电路—100

ꢀꢀꢀꢀꢀ

直流电源输入电路—110

ꢀꢀꢀꢀ

辅助电源电路—120

26.驱动电源电路—130

ꢀꢀꢀꢀꢀ

降压拓扑输出电路—200

ꢀꢀꢀꢀ

采样保护电路—300

27.电流采样电路—310

ꢀꢀꢀꢀꢀ

电压采样电路—320

ꢀꢀꢀꢀꢀꢀꢀꢀ

过流保护电路—330

28.温度采样电路—340

ꢀꢀꢀꢀꢀ

主控电路—400

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

烧录仿真电路—410

29.电平转换电路—420

ꢀꢀꢀꢀꢀ

串口隔离电路—430

ꢀꢀꢀꢀꢀꢀꢀꢀ

铁电存储电路—440

30.隔离驱动电路—500

ꢀꢀꢀꢀꢀ

光耦隔离电路—510

ꢀꢀꢀꢀꢀꢀꢀꢀ

驱动分离电路—520

具体实施方式

31.下面详细描述本实用新型的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本实用新型的实施例,而不能理解为对本实用新型的限制。

32.在本实用新型实施例的描述中,需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型实施例和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

33.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本实用新型实施例的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

34.在本实用新型实施例中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本实用新型实施例中的具体含义。

35.在本实用新型的一个实施例中,如图1-图6所示,提供一种带隔离驱动的降压拓扑电路,包括:电源输入电路100,所述电源输入电路100用于提供稳压直流电,所述输入电路100的输出端连接有一bat 连接端与一bus-连接端;降压拓扑输出电路200,所述降压拓扑输出电路200与所述电源输入电路100连接,所述降压拓扑输出电路200用于输出稳压直流电,所述降压拓扑输出电路200的输出端连接有所述bat 连接端与一bat-连接端;隔离驱动电路500,所述隔离驱动电路500与所述降压拓扑输出电路200连接,所述隔离驱动电路500用于隔离所述电源输入电路100与所述降压拓扑输出电路200的信号;主控电路400,所述主控电路400与所述隔离驱动电路500连接,所述主控电路400用于控制所述隔离驱动电路500的信号输出。

36.本实用新型通过设置所述隔离驱动电路500,使所述电源输入电路100与降压拓扑输出电路200隔离,能够有效防止电压出现不稳定跳变,并且使得输出信号对输入端不会造成影响;还通过设置所述降压拓扑输出电路200与所述电源输入电路100连接,有效控制电压降低,减少电压的波动,并提供稳定的电压输出。

37.具体地,在本实用新型的另一个实施例中,如图1和图6所示,所述隔离驱动电路500包括光耦隔离电路510与驱动分离电路520,所述光耦隔离电路510与所述主控电路400和驱动分离电路520连接,所述驱动分离电路520与所述降压拓扑输出电路200连接。

38.进一步地,所述光耦隔离电路510包括光耦隔离器u15、第三三极管q3与第八三极管q8,所述光耦隔离器u15的第一引脚与一 5v连接端和一第六十八电容c68的一端连接,所述第六十八电容c68的另一端接地;所述光耦隔离器u15的第三引脚与一第一百零七电阻r107的一端连接,所述第一百零七电阻r107的另一端与所述电平转换芯片u12的第二十一引脚连接;所述光耦隔离器u15的第四引脚接地,所述光耦隔离器u15的第五引脚与一第五电阻r5的一端和一第一百零九电阻r109的一端连接,所述第五电阻r5的另一端和所述第一百零九电阻r109的另一端均与所述第三三极管q3的基极和所述第八三极管q8的基极连接;所述光耦隔离器u15的第六引脚与一 15v连接端连接,所述第三三极管q3的集电极亦与一 15v连接端连接,所述第三三极管q3的发射极与所述第八三极管q8的发射极和所述驱动分离电路520连接,所述第八三极管q8的集电极与一-7v连接端连接。所述主控芯片u2发出的驱动信号在经过电平转换后由所述光耦隔离器u15进行信号隔离放大后,发送至所述驱动分离电路520。

39.进一步地,所述驱动分离电路520包括第一驱动分离电路520、第二驱动分离电路520、第三驱动分离电路520和第四驱动分离电路520;

40.所述第一驱动分离电路520包括第六二极管d6,所述第六二极管d6的正极与一第二十八电阻r28的一端和所述第三三极管q3的发射极连接,所述第六二极管d6的负极与一第二十九电阻r29的一端连接,所述第二十八电阻r28的另一端和所述第二十九电阻r29的另一端均与所述降压拓扑输出电路200连接。

41.所述第二驱动分离电路520包括第二十四二极管d24,所述第二十四二极管d24的正极与一第三十二电阻r32的一端和所述第三三极管q3的发射极连接,所述第二十四二极管d24的负极与一第三十三电阻r33的一端连接,所述第三十二电阻r32的另一端和所述第三十三电阻r33的另一端均与所述降压拓扑输出电路200连接。

42.所述第三驱动分离电路520包括第二十七二极管d27,所述第二十七二极管d27的正极与一第五十七电阻r57的一端和所述第三三极管q3的发射极连接,所述第二十七二极管d6的负极与一第六十六电阻r66的一端连接,所述第五十七电阻r57的另一端和所述第六十六电阻r66的另一端均与所述降压拓扑输出电路200连接。

43.所述第四驱动分离电路520包括第三十二极管d30,所述第三十二极管d30的正极与一第九十三电阻r93的一端和所述第三三极管q3的发射极连接,所述三十二极管d30的负极与一第九十四电阻r94的一端连接,所述九十三电阻r93的另一端和所述第九十四电阻r94的另一端均与所述降压拓扑输出电路200连接。

44.具体地,在本实用新型的另一个实施例中,如图1和图3所示,所述降压拓扑输出电路200包括第一场效应管q6、第二场效应管q9、第三场效应管q10、第四场效应管q11、第十二极管d10、第三二极管d3、第四二极管d4、第五二极管d5、第一电感l1和电流传感器hct1,所述第一场效应管q6的栅极与所述第二十八电阻r28的另一端连接,所述第一场效应管q6的发射极、所述第二场效应管q9的发射极、所述第三场效应管q10的发射极与所述第四场效应管q11的发射极均接地,所述的第一场效应管q6的集电极与所述第十二极管d10的正极连

接、所述第二场效应管q9的集电极与所述第三二极管d3的正极连接、所述第三场效应管q10的集电极与所述第四二极管d4的正极连接,所述第四场效应管q11的集电极与所述第五二极管d5的正极连接,所述第十二极管d10的负极、第三二极管d3的负极、第四二极管d4的负极和第五二极管d5的负极均与所述bat 连接端连接,所述第一场效应管q6的集电极、第二场效应管q9的集电极、第三场效应管q10的集电极和第四场效应管q11的集电极均与所述第一电感l1的一端连接,所述第一电感l1的另一端与所述电流传感器hct1的第五引脚连接,所述电流传感器hct1的第一引脚与所述 5v连接端连接,所述电流传感器hct1的第二引脚接地,所述电流传感器hct1的第三引脚与所述第十二电感l12的另一端连接;所述电流传感器hct1的第四引脚与所述bat-连接端连接。由此,所述主控电路400发出信号经所述光耦隔离电路510及所述驱动分离电路520的隔离后,由所述驱动分离电路520将信号分别发送至所述第一场效应管q6、所述第二场效应管q9、所述第三场效应管q10与所述第四场效应管q11,降低实时电压。

45.具体地,在本实用新型的另一个实施例中,如图1和图5所示,所述主控电路400包括主控芯片u2与电平转换芯片u12,所述主控芯片u2与所述电源输入电路100连接,所述主控芯片u2还与电平转换芯片u12连接,所述电平转换芯片u12与所述光耦隔离电路510连接。所述电平转换芯片u12的第三引脚与一第六电阻r6的一端连接,所述第六电阻r6的另一端与所述主控芯片u2的第二十九引脚和一第七电阻r7的一端连接,所述电平转换芯片u12的第四引脚与一第八电阻r8的一端连接,所述第八电阻r8的另一端与所述主控芯片u2的第二十八引脚连接;所述电平转换芯片u12的第十一引脚、第十二引脚和第十三引脚均接地;所述电平转换芯片u12的第二十引脚与第二十一引脚所述光耦隔离器u15的第三引脚连接。所述电平转换电路420将主控电路400输出3.3v的电平信号转换成5v的电平信号并输出至所述光耦隔离电路510。

46.本实施例中,所述电平转换芯片u12的芯片型号优选为74lvxc3245mtcx或者其同类型芯片。

47.具体地,在本实用新型的另一个实施例中,如图1和图2所示,所述电源输入电路100包括直流电源输入电路110、辅助电源电路120与驱动电源电路130。进一步地,所述直流电源输入电路110包括第一继电器rly1、第三继电器rly3、第四继电器rly4、第一y电容cy1和第二y电容cy2;所述第一继电器rly1的第一引脚与一第八端口cn8的第一引脚连接,所述第八端口的第一引脚接入电源,所述第一继电器rly1的第四引脚与一第四三极管q4集电极连接,所述第一继电器rly1的基极与所述第八端口cn8的第八引脚连接,所述第八引脚接入一软启动器(无显示),所述第一继电器rly1的第二引脚输出一dc 端,所述第一继电器rly1的第三引脚输出一bat 连接端。

48.所述第三继电器rly3的第三引脚与所述dc 端连接,所述第三继电器rly3的第四引脚与所述第一y电容cy1的一端连接,所述第一y电容cy1的另一端与所述第二y电容cy2的一端连接并接地;所述第二y电容cy2的另一端与所述第四继电器rly4的第四引脚连接,所述第四继电器rly4的第三引脚与一dc-端连接。所述第三继电器rly3的第一引脚为常闭引脚,所述第三继电器rly3的第二引脚为常开引脚,所述第三继电器rly3的第五引脚与所述第八端口cn8的第一引脚连接;所述第四继电器rly4的第一引脚为常闭引脚,所述第四继电器rly3的第二引脚为常开引脚,所述第四继电器rly4的第五引脚与所述第八端口cn8的第

一引脚连接。

49.具体地,在本实用新型的另一个实施例中,如图1和图4所示,所述驱动电源电路130包括驱动芯片u13、第一mos管q1、第二mos管q2、第一变压器t1和第二变压器t3,所述驱动芯片u13的第一引脚与一九十九电阻r99的一端连接,所述第九十九电阻r99的另一端与一第九十七电阻r97的一端连接,所述第九十七电阻r97的另一端与一 12v连接端连接;所述驱动芯片u13的第二引脚、第三引脚和第四引脚均接地;所述驱动芯片u13的第五引脚与一第一百五十五电阻r155的一端连接,所述第一百五十五电阻r155的另一端与所述第二mos管q2的栅极连接,所述第二mos管q2的源极接地;所述驱动芯片u13的第六引脚与所述第二mos管q2的漏极连接;所述驱动芯片u13的第七引脚与一第一百零二电阻r102的一端连接,所述第一百零二电阻的另一端与所述第一mos管q1的栅极连接;所述驱动芯片u13的第八引脚与一第一百零一电容c101的一端连接,所述第一百零一电阻c101的另一端与所述驱动芯片u13的第六引脚连接;所述第一mos管q1的漏极与一第一百五十七电阻r157的一端、一第一百零七电容c107的一端和一第一百零八电容c108的一端均连接,所述第一百五十七电阻r157的另一端、所述第一百零七电容c107的另一端与所述第一百零八电容c108的另一端均与所述第一变压器t1的第二引脚连接;所述第二mos管q2的漏极与所述第一mos管q1的源极连接,所述第二mos管q2的漏极还与所述第一变压器t1的第一引脚连接;所述第一变压器t1的第一引脚还与所述第三变压器t3的第一引脚连接,所述第一变压器t1的第二引脚与所述第三变压器t3的第二引脚连接。所述第一变压器t1的第四引脚与一第一二极管d1的正极连接,所述第一变压器t1的第三引脚接地;所述第三变压器t3的第四引脚与一第二十一二极管d21的正极连接,所述第二十一二极管d21的负极与一隔离驱动电路500连接,所述第三变压器t3的第三引脚接地,所述第三变压器t3的次级绕组输出一 15v连接端与一-7连接端。所述驱动芯片u13的第五引脚为低侧栅极驱动引脚,通过所述第二mos管q2的栅极与该低侧栅极驱动引脚连接,驱动低压侧电压值至所述第三变压器t3;所述驱动芯片u13的第七引脚为高侧栅极驱动引脚,通过所述第一mos管q1的栅极与该高侧栅极驱动引脚连接,驱动高压侧电压至所述第一变压器t1。

50.所述辅助电源电路120包括第二变压器t2、功率开关芯片u42,热敏电阻rt5,第三十二光耦u32;所述bat 连接端与一第三十七二极管d37的正极连接,所述第三十七二极管d37的负极与所述第二变压器t2的第三引脚连接,所述第三十七二极管d37的负极还与一第八十六电解电容c86的正极连接,所述第八十六电解电容c86的负极接地;所述bus-连接端与所述热敏电阻rt5的一端连接,所述热敏电阻rt5的另一端接地;所述第二变压器t2的第一引脚与一第四十四二极管d44的正极连接,所述第四十四二极管d44的负极与所述第二变压器t2的第三引脚连接;所述第二变压器t2的第十四引脚与一第四十二二极管d42的正极和一第二百五十五电阻r255的一端连接,所述第二百五十五电阻r255的另一端与一第九十电容c90的一端连接,所述第九十电容c90的另一端和所述第四十二二极管d42的负极均与一第十七电感l17的一端连接,所述第十七电感l17的一端与一 12v_1连接端,所述第十七电感l17的另一端与一 12v连接端连接;所述第二变压器t2的第十一引脚与一第四十六二极管d42的负极和一第四百四十五电阻r445的一端连接,所述第四百四十五电阻r445的另一端与一第一百四十三电容c143的一端连接,所述第一百四十三电容c143的另一端和所述第四十六二极管d46的正极均与一-12v连接端连接。

51.所述第二变压器t2的第五引脚与一第十九二极管d19的正极连接,所述第十九二极管d19的负极与一第二百五十四电阻r254的一端连接,所述第二百五十四电阻r254的另一端接地;所述第二百五十四电阻r254的另一端还与所述第三十二光耦u32的输出端的集电极连接,所述第三十二光耦u32的输出端发射极与所述功率开关芯片u42的第三引脚;所述第二百五十四电阻r254的另一端还与所述功率开关芯片u42的第四引脚连接;所述功率开关芯片u42的第一引脚与第二引脚均接地,所述功率开关芯片u42的第五引脚、第六引脚、第七引脚和第八引脚均与所述第二变压器t2的第一引脚连接。所述功率开关芯片u42通过第三引脚与所述第三十二光耦u32连接,获取反馈电压,并对基准源进行比较后控制,当开关电源输出的电压低于工作范围时,通过比较放大控制开关时间控制电路使开通时间变长,从而使输出的电压提升。本实施例中,所述功率开关芯片u42的芯片型号优选为viper22或者其同类型芯片。

52.所述第三十二光耦u32的输入端正极与一第二百五十九电阻r259的一端和一第二百六十电阻r260的一端连接,所述第二百六十电阻r260的另一端与所述 12v_1连接端连接,所述第二百五十九电阻r259的另一端与所述第三十二光耦u32的输入端负极连接,所述第三十二光耦u32的输入端负极与一第一百三十六电容c136的一端连接,所述第一百三十六电容的c136的另一端与一第二百五十七电阻r257的一端连接,所述第二百五十七电阻r257的另一端与一第二百八十电阻r280的一端和一第二百五十八电阻r258的一端连接,所述第二百八十电阻r280的另一端与所述 12v连接端连接,所述第二百五十八电阻r258的另一端接地。

53.进一步地,所述 12v连接端与一第四降压芯片u4的第五引脚连接,所述第四降压芯片u4的第二引脚接地,所述第四降压芯片u4的第六引脚与一第三电感l3的一端和一第七十七电容c77的一端连接,所述第三电感l3的另一端与一 5v连接端连接,所述第四降压芯片u4的第一引脚与所述第七十七电容c77的另一端连接,所述第四降压芯片u4的第三引脚与所述第三电感l3的另一端连接并接地。

54.进一步地,所述 5v连接端与一第三降压芯片u3的第三引脚连接,所述第三降压芯片u3的第一引脚接地,所述第三降压芯片u3的第二引脚与一 3.3v连接端和一第四电感l4的一端连接,所述第四电感l4的另一端与一 3.3va连接端和一第四十一电容c41的一端连接,所述第四十一电容c41的另一端接地。

55.进一步地,所述 5v连接端与一第二十六降压芯片u26的第一引脚连接,所述第二十六降压芯片u26的第三引脚接地,所述第二十六降压芯片u26的第二引脚与一ref3v连接端连接,所述ref3v连接端为基准电压连接端。

56.本实施例中,所述第四降压芯片u4的芯片型号优选为mp2451dt或者其同类型芯片;所述第三降压芯片u3的芯片型号优选为ams1117-3.3或者其同类型芯片;所述第二十六降压芯片u26的芯片型号优选为ref3030aidbzr或者其同类型芯片。

57.具体地,在本实用新型的另一个实施例中,如图1、图3和图4所示,本电池管理系统还包括采样保护电路300。

58.所述采样保护电路300包括电流采样电路310、电压采样电路320、过流保护电路330与温度采样电路340。所述电源输出电路200与所述电流采样电路310连接,所述电流采样电路310与所述主控芯片u2和所述过流保护电路330连接,所述主控芯片u2还与所述电压

采样电路320、温度采样电路340和所述过流保护电路330连接。

59.进一步地,所述电流采样电路310包括第十二电感l12、第一运算放大器u1a与电流传感器hct1,所述电流传感器hct1的第五引脚与所述电源输出电路200连接,所述电流传感器的第三引脚与所述第十二电感l12的一端连接,所述第一运算放大器u1a的第三引脚与一第七十七电阻r77的一端和一第五十一电容c51的一端连接,所述第五十一电容c51的另一端接地,所述第七十七电阻r77的另一端与一第七十三电阻的一端和一第七十六电阻的一端连接,所述第七十六电阻的另一端接地,所述第七十三电阻的另一端与第十二电感l12的另一端连接;所述第一运算放大器u1a的第二引脚与所述第一运算放大器u1a的第一引脚连接,形成负反馈电路,所述第一运算放大器u1a的第一引脚与一第七十八电阻r78的一端连接,所述第七十八电阻r78的另一端与所述主控芯片u2的第九引脚连接。在本实施例中,所述电流传感器hct1通过与所述电源输出电路200连接,实时采集所述电源输出电路200的电流值,并经过所述第十二电感l12接入所述第一运算放大器u1a的输入端,由所述第一运算放大器u1a输出信号至所述主控芯片u2的第九引脚,使所述主控芯片获取实时所述电源输出电路200的实时电流值。

60.进一步地,所述过流保护电路330包括第二运算放大器u57a,所述第二运算放大器u57a的第三引脚与一第十八电阻r18的一端、一第二十三电阻r23的一端、一第七十电阻r70的一端和一第四十六电容c46的一端连接,所述第十八电阻r18的另一端与所述电源输入电路100连接,所述第二十三电阻r23的另一端、所述第七十电阻r70的另一端与所述第四十六电容c46的另一端均接地;所述第二运算放大器u57a的第二引脚与一第七十一电阻r71的一端连接并接地,所述第七十一电阻r71的另一端与所述第七十八电阻r78的另一端连接;所述第二运算放大器u57a的第一引脚与所述主控芯片u2的第一引脚连接。通过将所述第一运算放大器u1a的输出端与所述第二运算放大器u57a的输入端第二引脚相互连接,且所述第二运算放大器u57a的输入端的第三引脚与所述电源输入电路100中的基准电压连接,使经过所述第一运算放大器u1a放大的电流信号与基准电压比较,输出电平信号进行过流保护。

61.进一步地,所述电压采样电路320包括第五运算放大器u20a、第六运算放大器u20b、第七运算放大器u20c与第八运算放大器u20d;所述第六运算放大器u20b的第六引脚与一第一百二十七电阻r127、一第一百二十六电阻r126、一第一百二十五电阻r125、一第一百二十四电阻r124、一第一百二十三电阻r123、一第一百二十二电阻r122和一第一百二十一电阻r121依次串联后与所述bat-连接端连接。所述第六运算放大器u20b的第五引脚与一第一百三十五电阻r135、一第一百三十四电阻r134、一第一百三十三电阻r133、一第一百三十二电阻r132、一第一百三十一电阻r131、一第一百三十电阻r130和一第一百二十九电阻r129依次串联后与所述bat 连接端连接;所述第六运算放大器u20b的第七引脚与所述第五运算放大器u20a的第三引脚连接,所述第五运算放大器u20b的第二引脚与所述第五运算放大器u20b的第一引脚连接,所述第五运算放大器u20b的第一引脚与所述主控芯片u2的第七引脚连接;所述第七运算放大器u20c的第九引脚与一第四十电阻r40、一第三十九电阻r39、一第三十八电阻r38、一第三十七电阻r37、一第三十六电阻36、一第二十六电阻26与第二十四电阻r24依次串联后与所述bus-连接端连接;所述第七运算放大器u20c的第十引脚与一第四十八电阻r48、一第四十七电阻r47、一第四十六电阻r46、一第四十五电阻r45、一第四十四电阻r44、一第四十三电阻r43与一第四十二电阻r42依次串联后与所述bat 连接端连

接;所述第七运算放大器u20c的第八引脚与所述第八运算放大器u20d的第十二引脚连接,所述第八运算放大器u20d的第十三引脚与所述第八运算放大器u20d的第十四引脚连接,所述第八运算放大器u20d的第十四引脚与所述主控芯片u2的第八引脚连接。通过采集所述电源输入电路100与所述电源输出电路200的电压,并将电压信号反馈到所述主控芯片u2中,由所述主控芯片u2对电压进行调节,防止电路出现过压的现象。

62.进一步地,所述温度采样电路340包括第一温度采集端口cn1、第九温度采集端口cn9、第三运算放大器u6a和第四运算放大器u57b。所述第一温度采集端口cn1的第一引脚与一第七电感l7的一端连接,所述第七电感l7的另一端与所述电源输入电路100中的基准电压连接,所述第一温度采集端口cn1的第二引脚与一第八电感l8的一端连接,所述第八电感l8的另一端与一第八十二电阻r82的一端连接,所述第八十二电阻r82的另一端与所述第四运算放大器u57b的第五引脚连接,所述第四运算放大器u57b的第六引脚与所述第四运算放大器u57b的第七引脚连接,所述第四运算放大器u57b的第七引脚与一第八十三电阻r83的一端连接,所述第八十三电阻r83的另一端与所述主控芯片u2的第五引脚连接。所述第九温度采集端口cn9的第一引脚与一第二电感l2的一端连接,所述第二电感l2的另一端与所述电源输入电路100中的基准电压连接,所述第九温度采集端口cn9的第二引脚与一第六电感l6的一端连接,所述第六电感l6的另一端与一第七十九电阻r79的一端连接,所述第七十九电阻r79的另一端与所述第三运算放大器u6a的第三引脚连接,所述第三运算放大器u6a的第二引脚与所述第三运算放大器u6a的第一引脚连接,形成负反馈电路,所述第三运算放大器u6a的第一引脚与一第八十电阻r80的一端连接,所述第八十电阻r80的另一端与所述主控芯片u2的第六引脚连接。通过所述第一温度采集端口cn1与所述第九温度采集端口cn9采集温度信号,分别经过所述第三运算放大器u6a与所述第四运算放大器u57b的输入端,由所述第三运算放大器u6a与所述第四运算放大器u57b的输出端将温度采样信号反馈至所述主控芯片u2。

63.进一步地,所述主控芯片u2的第十四引脚与一第五三极管q5的基极连接,所述第五三极管q5的发射极接地,所述第五三极管q5的集电极与一第二继电器rly2的第四引脚连接,所述第二继电器rly2的第三引脚与一第二风扇端口cn2的第一引脚连接,所述第二风扇端口cn2的第二引脚接地。由此,当温度采样信号反馈至所述主控芯片u2温度超出工作范围时,所述主控芯片u2实时控制风扇进行降温操作。

64.具体地,在本实用新型的另一个实施例中,如图1和图5所示,所述主控芯片u2还与一铁电存储电路440连接,所述铁电存储电路440包括铁电存储芯片u5,所述铁电存储芯片u5的第八引脚与所述 3.3v连接端和一第四十二电容c42的一端连接,所述铁电存储芯片u5的第四引脚与所述第四十二电容c42的另一端连接并接地,所述铁电存储芯片u5的第七引脚接地,所述铁电存储芯片u5的第五引脚与所述主控芯片u2的第三十一引脚和所述一第六十三电阻r63的一端连接,所述第六十三电阻r63的另一端与所述 3.3v连接端连接,所述铁电存储芯片u5的第六引脚与所述主控芯片u2的第三十六引脚和一第六十二电阻r62的一端连接,所述第六十二电阻r62的另一端与所述 3.3v连接端连接。

65.具体地,在本实用新型的另一个实施例中,如图1和图5所示,所述主控芯片u2还与一串口隔离电路430连接,所述串口隔离电路430包括数据发送电路432与数据接收电路431。所述数据接收电路431包括第二十三极管q20与第七十五光耦u75,所述第二十三极管

q20的集电极与一第四十九电阻r49的一端和一第九十八电阻r98的一端连接,所述第四十九电阻的另一端与所述主控芯片u2的第四十八引脚连接,所述第九十八电阻r98的另一端与所述 3.3v连接端连接,所述第二十三极管q20的发射极接地,所述第二十三极管q20的基极与一第一百三十六电阻r136的一端连接,所述第一百三十六电阻r136的另一端与所述第七十五光耦u75的输出端发射极连接,所述第七十五光耦的输出端集电极与所述 3.3v连接端连接,所述第七十五光耦u75的输入端正极与所述 3.3v连接端连接,所述第七十五光耦u75的输入端负极与一第八端口cn8的第三引脚连接。

66.进一步地,所述数据发送电路432包括第七十九光耦u79和第三十三极管q30,所述第七十九光耦u79的正极与所述 3.3v连接端连接,所述第七十九u79的负极与所述主控芯片u2的第四十七引脚连接,所述第七十九光耦u79的输出端集电极与所述 3.3v连接端和一第一百一十四电阻r114的一端连接,所述第一百一十四r114的另一端与一第一百一十一电阻r111的一端连接,所述第一百一十一电阻r111的另一端与所述第八端口cn8的第四引脚连接,所述第一百一十四r114的另一端还与所述第三十三极管q30的集电极连接,所述第三十三极管q30的基极与所述第七十九光耦u79的发射极连接,所述第三十三极管q30的发射极接地。

67.具体地,在本实用新型的另一个实施例中,如图1和图5所示,所述主控芯片u2与一烧录仿真电路410连接,所述烧录仿真电路410包括烧录仿真芯片j45,所述烧录仿真芯片j45的第一引脚与所述主控芯片u2的第二十一引脚和一第六十四电阻r64的一端连接,所述第六十四电阻r64的另一端与所述 3.3v连接端连接,所述烧录仿真芯片j45的第三引脚与所述主控芯片u2的第二十引脚和一第六十五电阻r65的一端连接,所述第六十五电阻r65的另一端与所述 3.3v连接端连接,所述主控芯片u2的第五引脚与所述 3.3v连接端连接,所述烧录仿真芯片j45的第七引脚与所述主控芯片u2的第二十二引脚连接,所述烧录仿真芯片j45的第九引脚和第十一引脚均与所述主控芯片u2的第二十三引脚连接,所述烧录仿真芯片j45的第十三引脚与一第六十八电阻r68的一端连接,所述第六十八电阻r68的另一端与所述 3.3v连接端连接,所述烧录仿真芯片j45的十四引脚与一第六十九电阻r68的一端连接,所述第六十九电阻r69的另一端与所述 3.3v连接端连接,所述烧录仿真芯片j45的第四引脚、第六引脚、第八引脚、第十引脚与第十二引脚均接地,所述烧录仿真芯片j45的第二引脚与一第六十七电阻r67的一端连接,所述第六十七电阻r67的另一端接地。

68.以上所述仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。