技术特征:

1.一种用于操作包括多个区块的集成电路芯片的方法,所述方法包括:确定用于计算的执行的集成电路的区块的配置;当所述区块的所述配置满足第一标准时,在第一模式中操作所述集成电路,包括:在所述集成电路的所述区块中的每一个处同时接收用于所述计算的相应输入数据;和当所述区块的所述配置满足第二标准时,在第二模式中操作所述集成电路,包括:在第一时间,在所述集成电路的第一组区块的每个区块处同时接收用于所述计算的相应第一输入数据;在所述第一时间,将用于所述计算的相应第二输入数据存储在多个延迟寄存器的每一个中,每个延迟寄存器与所述集成电路的第二组区块中的区块相对应;在第二时间,从所述延迟寄存器释放所述第二输入数据,并在所述第二组区块的每个区块处接收释放的相应第二输入数据。2.根据权利要求1所述的方法,其中确定用于所述计算的执行的所述区块的配置包括确定可操作用于执行所述计算的区块的数量和百分比中的一个或多个。3.根据权利要求2所述的方法,其中所述第一标准包括可操作用于执行所述计算的区块的数量或百分比小于阈值数量或百分比,以及其中所述第二标准包括可操作用于执行所述计算的区块的数量或百分比大于阈值数量或百分比。4.根据权利要求1所述的方法,其中确定用于所述计算的执行的所述区块的配置包括确定可操作用于执行所述计算的区块的列的数量。5.根据权利要求4所述的方法,其中所述第一标准包括可操作用于执行所述计算的区块的列的数量或百分比小于阈值数量或百分比,以及其中所述第二标准包括可操作用于执行所述计算的区块的列的数量或百分比大于阈值数量或百分比。6.根据权利要求1所述的方法,包括确定所述区块的所述配置是否满足所述第一标准或所述第二标准。7.根据权利要求1所述的方法,其中在第二模式中操作所述集成电路包括操作复用器以启用所述延迟寄存器。8.根据权利要求7所述的方法,其中在第一模式中操作所述集成电路包括操作所述复用器以禁用所述延迟寄存器。9.根据权利要求1所述的方法,其中所述第一时间是第一时钟周期,并且所述第二时间是下一时钟周期。10.根据权利要求1所述的方法,其中在所述第一模式中同时接收相应输入数据包括在每个区块处接收输入数据的向量。11.根据权利要求1所述的方法,其中在第一模式中操作所述集成电路包括操作所述集成电路的所述区块中的每一个来处理所述相应输入数据。12.根据权利要求1所述的方法,其中在第二模式中操作所述集成电路包括:操作第一组的区块中的每一个来处理所述相应第一输入数据;和操作第二组的区块中的每一个来处理从所述延迟寄存器释放的所述相应第二输入数据。

13.根据权利要求1所述的方法,包括从编译器接收所述第一标准和所述第二标准的指示。14.一种集成电路,包括:多个延迟寄存器,每个延迟寄存器连接到对应的第一总线线路;多个区块,所述区块的第一组的每个区块连接到对应的第二总线线路,并且所述区块的第二组的每个区块连接到所述第一总线线路中的对应的一条;以及控制器,被配置为:确定用于计算的执行的第一组区块和第二组区块的配置;当所述区块的所述配置满足第一标准时,控制集成电路在第一模式中操作,在所述第一模式中,经由所述第一总线线路和所述第二总线线路在所述多个区块的每一个处同时接收用于所述计算的相应输入数据;和当所述区块的所述配置满足第二标准时,控制所述集成电路在第二模式中操作,其中:在第一时间,在所述第一组区块的每个区块处同时接收用于所述计算的相应第一输入数据;在所述第一时间,将用于所述计算的第二输入数据存储在所述延迟寄存器中的每一个中;和在第二时间,从所述延迟寄存器释放所述第二输入数据,并且在所述第二组区块的每个区块处接收相应第二输入数据。15.根据权利要求14所述的集成电路,包括连接到每个第二总线线路的复用器。16.根据权利要求14所述的集成电路,其中所述区块以二维阵列布置。17.根据权利要求14所述的集成电路,其中所述集成电路包括专用集成电路(asic)。18.根据权利要求14所述的集成电路,其中每个区块包括:多个计算单元;耦合到所述计算单元的存储器;以及可控总线线路,其被配置为向所述区块输送数据或从所述区块输送数据。19.根据权利要求14所述的集成电路,其中所述区块中的至少之一被配置为充当所述控制器。20.根据权利要求14所述的集成电路,包括通信接口。

技术总结

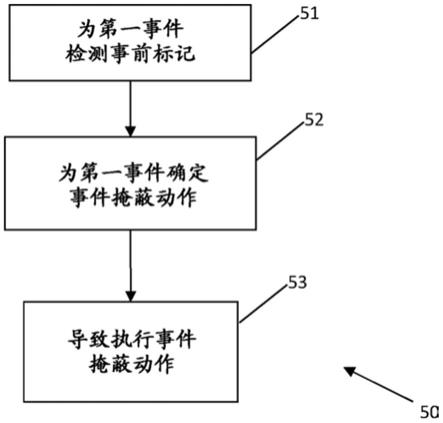

一种用于操作包括多个区块(202a-202d)的集成电路芯片的方法,包括确定用于计算的执行的区块的配置。当区块的配置满足第一标准时,集成电路在第一模式中操作,包括在区块(202a-202d)中的每一个处同时接收相应输入数据(208a,208b)。当区块的配置满足第二标准时,集成电路在第二模式中操作,包括:在第一时间,在第一组区块的每个区块(202a,202b)处同时接收相应第一输入数据(208a,208b);在第一时间,将相应第二输入数据(208a,208b)存储在多个延迟寄存器(212a,212b)的每一个中,每个延迟寄存器与第二组区块中的区块(202c,202d)相对应;在第二时间,从延迟寄存器(212a,212b)释放第二输入数据,并在第二组区块的每个区块(202c,202d)处接收释放的相应第二输入数据。202d)处接收释放的相应第二输入数据。202d)处接收释放的相应第二输入数据。

技术研发人员:R.波普

受保护的技术使用者:谷歌有限责任公司

技术研发日:2020.08.14

技术公布日:2022/3/22

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。