1.本发明涉及矩阵阵列检测器和实现该检测器的方法。本发明可用于产生可见图像,但不限于该领域。例如,可以生成压力或温度图或化学势或电势的二维表示。这些图或表示形成物理量的图像。本发明特别适用于采用电离辐射(例如x射线)的成像设备中的有源矩阵阵列检测器,该有源矩阵阵列检测器例如用于检测目的,诸如为tft板,tft代表“薄膜晶体管”。

背景技术:

2.在矩阵阵列检测器中,像素代表检测器的基本敏感元件。各个像素将其受到的物理效应转换为电信号。在矩阵阵列读取级收集来自各个像素的电信号,然后被数字化以能够被处理和存储以形成图像。例如,像素由对物理效应敏感并传递电荷电流的区域形成。物理效应可以是传递光子流的电磁辐射,并且因此将按照这种类型的辐射来解释本发明,并且电荷电流依赖于敏感区接收的光子流。推广到任何矩阵阵列检测器是很简单的。

3.矩阵阵列图像检测器包括:行导体,各个行导体连接同一行的像素;以及列导体,各个列导体连接同一列的像素。列导体连接到转换器电路,转换器电路通常设置在矩阵阵列的边缘,该边缘可以被称为“列的足部(foot)”。

4.各个像素通常包括光敏元件或光电检测器,其例如可以是光电二极管、光敏电阻器或光电晶体管。有大尺寸的光敏矩阵阵列,其可能有按行和列排列的数百万个像素。各个像素还包括电子电路,电子电路例如包括开关、电容器和电阻器,在电子电路的下游存在致动器。包括光敏元件和电子电路的组件允许产生和收集电荷。该电子电路通常允许在电荷转移之后重置在各个像素中收集的电荷。致动器的作用是将电子电路收集的电荷转移或复制到列导体中。当致动器从行导体接收到进行转移的指令时执行该转移。致动器的输出对应于像素的输出。措辞“行导体”和“列导体”完全是任意的。当然可以交换这些措辞。

5.在这种类型的检测器中,像素分两个阶段工作:图像捕获阶段,在该图像捕获阶段中,像素的电子电路积累光敏元件产生的电荷,以及读取阶段,在该读取阶段中,所收集的电荷被由致动器转移或复制到列导体中。

6.在读取阶段,由行导体向矩阵阵列的同一行的所有致动器发送读取指令。该行中的各个像素通过向与该像素相关联的列导体发送其电信息而被读取,该电信息例如为电荷、电压、电流、频率等。

7.对于一个图像帧,可以在对应于帧持续时间的一部分的行选择时间内在对矩阵阵列的行进行扫描的方向上依次选择像素行,从而允许将适当的信号(例如电压)施加到相关行的像素。因此,选择行对应于在相应的行选择时间内施加高电平信号,该高电平信号控制相应像素行的开关器件的导通状态。在该行选择时间之外,通过施加适当的低电平信号将开关器件保持在关断状态。例如,当开关器件是晶体管,而施加的信号是电压时,通常的做法是用vgon来表示与高电平对应因而与开关晶体管的导通状态对应的电压,用vgoff来表示与低电平对应并且与开关晶体管的关断状态对应的电压。

8.行可以由包括串联的一个或更多个移位寄存器的控制电路控制,各移位寄存器包括多个级联级,各个级适用于根据行选择操作的顺序(例如垂直扫描)来切换向针对矩阵阵列的相应行的像素的致动器施加的信号的高电平和低电平。控制电路可以在集成电路中实现,同一个集成电路能够例如具有用于矩阵阵列中的多个行的多个控制电路。该集成电路可以例如在矩阵阵列的外部,并且通过有线方式连接到矩阵阵列,例如通过柔性带状电缆。该控制电路也可以安装在承载像素的板上,如以本技术人的名义提交的专利申请wo2012/152836a1中所描述的。

9.这使得可以减少施加到板上的信号的数量,从而减少用于将板连接到其周围电子装置的柔性连接器的尺寸和数量。这种集成的控制电路架构通过减少部件数量并且简化制造工艺,显着地简化了检测器架构。

10.然而,该架构规定了矩阵行被驱动的顺序。该顺序是由控制电路与矩阵行的连接规定的。在某些情况下,可能期望改变控制矩阵行的顺序。更具体地,可能希望将多个像素分组在一起以共同地读出。这种分组在一起,在文献中称为“分箱”,允许提高所读出的各个像素的信噪比。将像素分组在一起的另一优点是提高了检测器的灵敏度。然而,分组在一起会对空间分辨率产生负面影响。

11.在来自各个像素的信息是电荷的情况下,可以通过在共用电容器上重新分配来自将被分组在一起的像素的电荷来实现像素的分组,该共用电容器例如设置在位于列的足部处的转换器电路中。这可以在诸如在专利申请wo2012/152836a1中描述的检测器中通过连续读出各行像素来实现。然而,在这样的检测器中,将连续行的像素分组在一起并不能提高检测器的读出速度,也不能因此增加由检测器产生的图像的频率。

技术实现要素:

12.本发明旨在通过提供一种检测器来克服上述所有或一些问题,针对该检测器的控制电路允许传统的顺序读出或将属于连续行的像素分组在一起,从而提高了读出速度。本发明在以下检测器中是特别有利的,该检测器将控制电路与像素产生在同一基板上。

13.为此,本发明的一个主题是一种矩阵阵列检测器,所述矩阵阵列检测器包括:

14.像素的阵列,所述像素对物理效应敏感并且沿像素行和竖列排列成矩阵,各个像素根据所述物理效应生成信号,所述像素的所述行物理地排序;

15.行导体,各个行导体允许驱动一行像素;

16.驱动器模块,各个驱动器模块与一个行导体相关联,各个驱动器模块向所述行导体中的一个行导体传递选择信号,所述驱动器模块分布在多个组中,所述多个组根据所述像素的所述行的顺序交织,

17.其中,各个组的所述驱动器模块按照与所讨论的驱动器模块组相关联的行的物理顺序来彼此链接,各个驱动器模块组的链接独立于一个或更多个其他驱动器模块组的链接。

18.有利地,所述矩阵阵列检测器还包括用于生成多个令牌的模块,各个令牌被传递到各个驱动器模块组的第一驱动器模块的输入,在各组驱动器模块中,各个模块的输出连接到具有更高序号的模块的输入,所述驱动器模块在其各组中是按照像素行的顺序排序的,该像素行的导体由所讨论的驱动器模块传递所述选择信号。

19.有利地,所述像素和所述驱动器模块是在同一基板上制造的,所述基板是基于仅n型薄膜晶体管或仅p型薄膜晶体管的。

20.本发明的另一个主题是使用根据本发明的矩阵阵列检测器的方法,其中,属于不同组并且与连续行导体连接的驱动器模块能够接收同时控制信号以同时驱动连续行,或接收交替控制信号以分别驱动连续行。

附图说明

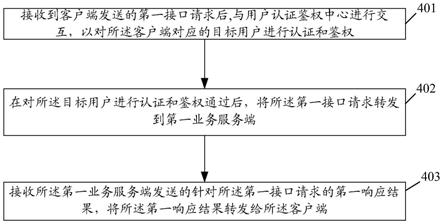

21.通过阅读以示例方式给出的实施方式的详细描述,将更好地理解本发明并且进一步的优点将变得明显,该描述由附图示出,其中:

22.图1示出了可以在根据本发明的检测器中实现的示例性像素矩阵阵列;

23.图2示出了根据本发明的示例性检测器;

24.图3示出了可以在图2的检测器中实现的多个驱动器模块的一个示例性实施方式;

25.图4示出了可以在图2的检测器中实现的多个驱动器模块的另一示例性实施方式;

26.图5示出了图4的驱动器模块的详细示例;

27.图6以时序图的形式示出了实现了驱动器模块的检测器的操作的示例,驱动器模块如图5所示并且被链接成仅一个组;

28.图7以时序图的形式示出了实现了驱动器模块的检测器的操作的示例,驱动器模块如图5所示并且被链接成两个组以对检测器的像素进行单独读出;

29.图8以时序图的形式示出了实现了驱动器模块的检测器的操作的示例,驱动器模块如图5所示并且被链接成两个组以对检测器的像素进行共同读出。

30.为了清楚起见,在各个图中相同的元件将带有相同的附图标记。

具体实施方式

31.以下描述是参照包括被称为像素的多个基础电子电路的矩阵阵列检测器而提供的,各个基础电子电路包括对物理量敏感的元件。在所描述的示例中,基础电子电路是对光辐射敏感的像素。很明显,本发明可用于对任何形式的物理量敏感的其他检测器,其允许产生例如压力图或温度图。

32.图1示意性地示出了矩阵阵列检测器的检测区10。为了方便理解,检测区包含两行两列的矩阵。形成了四个像素p,各个像素位于一行一列的交叉处。当然,实际的矩阵阵列通常要大得多,并且具有大量的行和列。像素矩阵阵列属于允许产生数字化图像的矩阵阵列检测器12。

33.各个像素p包括光敏区和电子处理电路,光敏区在这里由光电二极管d表示,电子处理电路在图1的示例中由单个晶体管t形成。用于部件d和t的附图标记后面是分别表示行序号i和i 1以及列序号j和j 1的两个坐标。行和列是按照它们在像素矩阵阵列中占据的物理顺序来排序的。所示出的像素分别具有一个晶体管,因此其也称为1t像素,其功能将在下面进一步描述。

34.通常,一般做法是生产包括薄膜场效应晶体管的像素矩阵阵列,薄膜场效应晶体管以tft来命名(“薄膜晶体管”的简称)。tft可以基于金属氧化物,例如基于非晶或晶体氧化铟、镓和锌的晶体管,其以缩写igzo来命名。可以采用其他tft系列,例如有机tft、非晶硅

tft或多晶硅tft。在这最后一种类型的tft中,有些是在低温下合成的。它们以“低温多晶硅”的首字母缩写ltps来命名。

35.同一列的像素p连接到列导体col。该导体允许收集来自与其连接的像素的信息。同一行的像素p连接到行导体l,行导体l携带信号vg从而允许控制对应的像素行。

36.在重置操作之后发生的图像捕获阶段中,光电二极管d接收的照射降低其阴极的电势。该图像捕获阶段之后是读取阶段,其中,光电二极管d的电势被读取。为此,晶体管t被导通,因此晶体管t充当开关,其通过施加到其栅极的控制信号vg来控制。

37.当通过信号vg选中时,列导体col被使用以从对应列中的像素收集信息。

38.可以在具有较简单的像素的检测器中实现本发明,特别是通过用由信号vg导通的简单二极管代替晶体管t。也可以在具有包括多个晶体管的像素的检测器中实施本发明。特别地,已知实现3t像素,其除了上述读取晶体管外,还包括用于光电二极管的重置晶体管和跟随器晶体管。在这种类型的3t像素中,第二行导体传送重置信号,该重置信号允许控制对晶体管进行重置。

39.图2示意性地示出了整个检测器12。检测器12包括形成基板的板14,检测区10的部件在该基板上产生。向所有行导体l传递控制信号的驱动器模块16设置在同一板14上。或者,可以在与板14不同的基板上制造驱动器模块16。然而,将驱动器模块16与像素p制造在同一基板上可以限制将板14与其周围部件连接的连接。

40.检测器12包括连接到列导体col的读取电路18。读取电路18通常在与板14不同的基板上产生。读取电路18通过带状电缆与板14连接。

41.检测器12包括电路20,该电路20允许驱动驱动器模块16并且允许取得来自读取电路18的信号,特别是为了对信号进行复用。

42.图3示出了四个驱动器模块16的第一示例性实施方式,各个驱动器模块被配置成驱动一行像素。清楚地理解,本发明可以针对更多行像素来实施。更具体地,由sr_a(n)表示的第一驱动器模块的输出out_a(n)连接到行导体l(i),该行导体l(i)传送针对第i行的读出信号vg。由sr_b(n)表示的第二驱动器模块的输出out_b(n)连接到行导体l(i 1),该行导体l(i 1)传送针对第i 1行的读出信号vg。由sr_a(n 1)表示的第三驱动器模块的输出out_a(n 1)连接到行导体l(i 2),该行导体l(i 2)传送针对第i 2行的读出信号vg。由sr_b(n 1)表示的第四驱动器模块的输出out_b(n 1)连接到行导体l(i 3),该行导体l(i 3)传送针对第i 3行的读出信号vg。行和驱动器模块按图3的顺序排序。更具体地,在单独读出各行像素的情况下,先读出第i行,然后读出第i 1行,然后读出第i 2行,最后读出第i 3行。如将进一步看到的,驱动器模块被配置成还允许通过将连续成对的行分组在一起来读出。

43.在所示出的示例中,驱动器模块分布在两组中:驱动器模块sr_a(n)和驱动器模块sr_a(n 1)在第一组a中,驱动器模块sr_b(n)和驱动器模块sr_b(n 1)在第二组b中。本发明可以用更多组驱动器模块来实现。行也被分为两个组:一方面是针对行l(i)和行l(i 2)的组la,另一方面是针对行l(i 1)和行l(i 3)的组lb。驱动器模块组a与行的组la相关联,而驱动器模块组b与行的组lb相关联。行的组la和lb以及驱动器模块组a和b是交织的。更具体地,在各个组中,驱动器模块是按照矩阵阵列的行的物理顺序排序的。对于两个驱动器模块组a和b,按照矩阵阵列的行的物理顺序,第一组a的第一驱动器模块sr_a(1)驱动矩阵阵列的第一行l(1)。第二组b的第一驱动器模块sr_b(1)驱动第二行l(2)。第一组a的第二驱动器

模块sr_a(2)驱动第三行l(4)。第二组b的第二个驱动器模块sr_b(2)驱动第四行l(1),依此类推,直到矩阵阵列的最后一行。更一般地,对于驱动器模块的k个组,使用以下标记法:

44.i:当前行在矩阵阵列的行的物理顺序中的序号,

45.j:模块在其组中的序号,

46.k:组的序号,在1到k之间,

47.第i行由序号为k的组的序号为j的模块驱动,其中:

48.i=(j-1)k k。

49.将行和驱动器模块分布在彼此关联的各个组中使得可以不同地驱动行的组,并且特别是通过调整驱动器模块的各个组的同步并且因此通过调整行的组的驱动。

50.图3示出了允许驱动器模块的特别简单的连接的一个实施方式。清楚地理解,其他连接也是可能的。各个驱动器模块分别包括使得可以接收针对所讨论的模块的命令的输入in_a(n)、in_b(n)、in_a(n 1)、in_b(n 1);和使得可以分别驱动相关联的行的输出out_a(n)、out_b(n)、out_a(n 1)、out_b(n 1)。在各个组中,驱动器模块按照与所讨论的组相关联的行的顺序彼此链接。一组的链接独立于驱动器模块的一个或更多个其他组的链接。更具体地,在所示出的示例中,输出out_a(n)与输入in_a(n 1)连接,并且输出out_b(n)与输入in_b(n 1)连接。

51.检测器12包括生成模块30,其使得可以生成第一令牌in_a,第一令牌in_a被传递到组a的第一驱动器模块sr_a(n)的输入。生成模块30还使得可以生成第二令牌in_b,第二令牌in_b被传递到组b的第一驱动器模块sr_b(n)的输入。驱动器模块的链接使得令牌可以从一个驱动器模块行进到同一个组中的下一驱动器模块。更一般地,生成模块30使得可以生成与驱动器模块组相同数量的令牌。

52.此外,驱动器模块接收一个或更多个控制信号:针对组a的“n控制a”和针对组b的“n控制b”。这些控制信号例如为时钟,令牌按照该时钟的速率从一个模块传送到同一组中的另一模块。控制信号可以由生成模块30生成,生成模块30可以设置在板14上或设置在与板14分开的基板上,例如在电路20中。在各个驱动器模块之间的用于控制信号的连接和在接续的模块之间的从输出到输入的连接可以在板14上进行,因此不需要外部连接。

53.检测器12可以以各种方式来操作,通过以矩阵阵列的行的顺序依次生成各个行的信号vg(其允许对检测器12的像素进行单独读出),或者通过在两个组中具有相同序号的模块中同时生成信号vg。换言之,信号vg由驱动器模块sr_a(n)和sr_b(n)同时发送,然后由驱动器模块sr_a(n 1)和sr_b(n 1)同时发送,其允许将发源于不同行的像素的信息分组在一起。通过改变令牌in_a和in_b以及潜在的驱动器模块控制信号的发送时间,可以在检测器读出的两种类型(即单独读出或按像素组读出)之间进行选择。两个令牌的同时发送允许按组读出。两个令牌的交替发送允许单独读出。

54.通过将驱动器模块分布在两组中,能够将两行像素的读出分组在一起。更一般地,k个组可以将k个行的读出分组在一起。以组数的约数对行进行分组也是可能的。例如,对于四组驱动器模块,可以根据针对各个组的令牌和相应控制信号的发送中的偏移量,单独读出矩阵阵列、按两行形成的组读出矩阵阵列或按四行形成的组读出矩阵阵列。

55.图4示出了四个驱动器模块16的另一示例性实施方式,各个驱动器模块被配置成驱动一行像素。在该示例中,各个驱动器模块包括输入级e和输出级s。输入级e传递针对对

应的输出级s的激活信号outa或outb。在由输入级激活的情况下,对应的输出级发送此处由gateline表示的针对驱动器模块的输出信号。具有两个级的该示例对应于在上述专利申请wo2012/152836a1中描述的方案。令牌在同一组的两个连续驱动器模块之间的发送是通过发送到具有较高序号的模块的输入级的输入的激活信号来实现的。允许发送令牌的各个模块的输入级及其连接形成了移位寄存器。各个输出级形成放大器,其允许激活信号适应于信号vg的特性。

56.图5较详细地示出了图4的驱动器模块中的一个的图。形成根据本发明的行寻址器件的集成结构可以主要包括单一类型的晶体管tft,即p型或n型,n型因其较好的性能而是优选的。因此,下文描述的所有晶体管可以是单一n型或p型的薄膜晶体管tft。

57.图5所示的结构对应于一个有利实施方式,其中行寻址器件的各个级n包括输入级50和输出级51。对于行寻址器件的级n,输入级50和输出级51各自包括例如上面参照图3描述的行寻址级n中包括的大部分元件。应当注意,在所描述的示例性实施方式中,矩阵阵列的各个行n与寻址器件的级n相关联。然而,在图中未描述的另选示例中,可以设想以下行寻址器件结构:其中给定级控制多个行,或者其中一些行不由级来控制。

58.因此,针对行寻址器件的级n的输入级50可以由移位寄存器形成,该移位寄存器包括将激活信号out(n)呈现为输出的输出行。输入级50可以包括针对输入级的输出晶体管t30,其在激活输出out(n)处发送时钟信号的脉冲。针对输入级的输出晶体管t30的栅极可以连接到行寻址器件的输入级的内部节点,其源极可以连接到激活输出out(n)并且其漏极可以接收来自第一时钟clk1的信号。针对输入级的升压电容器c20可以连接在针对输入级的输出晶体管t30的栅极与源极之间。针对输入级的第一控制晶体管t10可以对针对输入级的输出晶体管t30的栅极进行预充电。针对输入级的第一控制晶体管t10的源极因此连接到针对输入级的输出晶体管t30的栅极。针对输入级的第一控制晶体管t10的栅极和漏极由针对前一行n-1的寻址器件的级n-1的激活输出out(n-1)来控制。

59.针对输入级的第二控制晶体管t20能够对针对输入级的输出晶体管t30的栅极放电。针对输入级的第二控制晶体管t20的漏极因此连接到针对输入级的输出晶体管t30的栅极。针对输入级的补偿电容器c10可以有利地设置在来自第二时钟clk2的信号之间,其与来自第一时钟clk1的信号相位相反。

60.有利地,针对输入级的放电晶体管t40可以连接到针对行寻址器件的级n的输入级50的激活输出out(n)。输入级的放电晶体管t40的栅极连接到针对输入级的第二控制晶体管t20的栅极;其还连接到针对下一级n 1的激活输出信号out(n 1)。

61.类似地,行寻址器件的级n的输出级51可以由移位寄存器形成,该移位寄存器包括将信号sn呈现为输出的输出行。输出级51可以包括针对输出级的输出晶体管t31,其在输出sn处发送时钟信号的脉冲。输出晶体管t31的栅极可以连接到行寻址器件的级的内部节点,其源极可以连接到输出sn,并且其漏极可以接收来自第三时钟clk3的信号。针对输出级的升压电容器c21可以连接在针对输出级的输出晶体管t31的栅极与源极之间。针对输出级的第一控制晶体管t11能够对针对输出级的输出晶体管t31的栅极进行预充电。针对输出级的第一控制晶体管t11的源极因此连接到针对输出级的输出晶体管t31的栅极。针对输出级的第一控制晶体管t11的栅极和漏极由针对寻址器件的级n的输入级50的激活输出out(n)控制。

62.针对输出级的第二控制晶体管t21能够对针对输出级的输出晶体管t31的栅极放电。针对输出级的第二控制晶体管t21的漏极因此连接到针对输出级的输出晶体管t31的栅极。针对输出级的补偿电容器c11可以有利地设置在来自第四时钟clk4的信号之间,其与来自第三时钟clk3的信号相位相反。第三clk3和第四时钟clk4的特殊之处在于其占空比可以是不同的,并且其各自处于其高电平的周期的总和对应于第一时钟clk1和第二时钟clk2的周期。

63.有利地,针对输出级的放电晶体管t41可以连接到行寻址器件的级n的输出级51的输出sn,传递针对行n的激活信号。针对输出级的放电晶体管t41的栅极连接到针对输出级的第二控制晶体管t21的栅极;其还连接到下一级n 1的激活输出out(n 1)。

64.根据本发明的另一具体特征,输入级50还包括针对输入级tr的重置晶体管,该重置晶体管的栅极由重置信号的脉冲来控制。针对输入级tr的重置晶体管的源极可以连接到针对输入级的第二控制晶体管t20的源极。针对输入级tr的重置晶体管的漏极可以连接到针对输入级的第二控制晶体管t20的漏极。

65.同样,输出级51也包括针对输出级tr的重置晶体管,该重置晶体管的栅极以及针对该输入级的重置晶体管的栅极由重置信号的脉冲来控制。针对输出级tr的重置晶体管的源极可以分别连接到针对输出级的第二控制晶体管t21的源极和针对输出级的放电晶体管t41的源极,并且分别连接到针对输入级的第二控制晶体管t20的源极和针对输入级的放电晶体管t40的源极。针对输出级tr的重置晶体管的漏极可以连接到针对输入级的第二控制晶体管t21的漏极。

66.因此,重置脉冲使得可以在输入级50和输出级51中的各个晶体管上施加关断状态。

67.此外,输出级51可以包括行重置晶体管tl。行重置晶体管tl由特定信号经由其栅极来控制。行重置晶体管tl的漏极连接到针对输出级的输出晶体管t31的源极。行重置晶体管tl的源极可以连接到晶体管t20、t40、t21和t41的源极。针对级n的行重置晶体管tl可以将行n上的电压强制为低状态。行重置晶体管tl使得可以控制行上的电压,即相对于级的输出级的输出,并向其施加低阻抗电压,特别是在“死区时间”期间。具体地,按照通常方式,例如x射线检测器的驱动包括重置阶段,接着是施加x射线或“x窗口”的阶段,然后是读出阶段。在x窗口期间,x射线在光电二极管中转换为电子;x窗口的持续时间相对较长,通常长达3.2秒,因此行重置晶体管tl使得可以避免矩阵阵列中的任何漂移。

68.再次有利地,各个输出级51可以包括矩阵阵列重置开关,矩阵阵列重置开关例如由矩阵阵列重置晶体管tlon形成,使得可以执行矩阵阵列的完全重置。矩阵阵列重置晶体管tlon可以由施加到其栅极和其漏极的矩阵阵列重置信号来控制。矩阵阵列重置晶体管tlon的源极可以连接到针对输出级的输出晶体管t31的源极。对矩阵阵列重置晶体管tlon进行控制的矩阵阵列重置信号可以是电压vgoff或激活电压vgon。当矩阵阵列重置晶体管tlon被激活时,即当激活电压vgon被施加时,激活电压随后被施加到整个矩阵阵列。

69.在实践中,矩阵阵列的完全重置可以根据由矩阵阵列重置晶体管tlon的激活定义的顺序进行足够的持续时间,然后激活行重置晶体管tl使得可以将行设置回到电压vgoff。

70.图6以时序图的形式例示了设置在单个组中的图5的驱动器模块的操作,如专利申请wo2012/152836a1中所描述的。单个令牌in被发送到针对第一驱动器模块的输入级e的控

制晶体管t10的栅极和漏极。时钟clk1和clk2相位是相反的,高电平和低电平的份额相等。时钟clk3和clk4的相位也相反,其周期时间是时钟clk1和clk2的周期时间的一半。时钟clk4的高电平持续时间比时钟clk3的长。

71.图6还示出了针对四个连续行的信号out(n)。各个信号out(n)相对于前一信号偏移了时钟clk1的半个周期。还示出了针对相同的四个行的信号gateline(n)。在两个连续信号gateline的两个高电平之间观察到死区时间tm。该死区时间对应于时钟clk3的高电平持续时间。时钟clk3高电平的最短持续时间是保证晶体管t31的栅极充电所需要的。不可能通过将驱动器模块直接链接在单个组中来消除这个死区时间。

72.相反地,通过将驱动器模块分布在多个组中,对于像素的单独读出,可以用另一组的信号gateline的高电平来掩蔽同一组的两个连续模块之间的死区时间。

73.图7以时序图的形式例示了检测器12的操作的一个示例,该检测器12实施如图5所示的并且被链接成两组以用于检测器的像素的单独读出的驱动器模块。对于第一组a,存在令牌ina和四个时钟clk1a、clk2a、clk3a和clk4a。时钟clk1a与clk2a的相位是相反的。时钟clk3a与clk4a的相位也是相反的,其周期时间是时钟clk1和clk2的周期时间的一半。与图6中描述的时钟不同,四个时钟clk1a、clk2a、clk3a和clk4a具有相同的其各自高电平和低电平份额。

74.在图7中,还示出了针对组b的令牌inb和四个时钟clk1b、clk2b、clk3b和clk4b。相对于组a,b组的信号偏移了时钟clk1a的周期的四分之一。

75.对于组a,两个信号outa(1)和outa(2)以及两个信号gateline(1)和gateline(3)对应于组a的两个连续驱动器模块。信号gateline(1)和gateline(3)使得可以驱动矩阵阵列的序号为1和3的行。同样地,对于b组,两个信号outb(1)和outb(2)以及两个信号gateline(2)和gateline(4)对应于组b的两个连续驱动器模块。信号gateline(2)和gateline(4))可以驱动矩阵阵列的序号为2和4的行。换句话说,组a的驱动器模块生成针对矩阵阵列的奇数行的信号gateline,并且组b的驱动器模块生成针对矩阵阵列的偶数行的信号gateline。

76.两个组的交织使得可以延长时钟clk3a的高电平的持续时间。因此可以在没有连续两行之间的死区时间的情况下确保晶体管t31的栅极的充电。具体地,组a的驱动器模块的晶体管t31的栅极在组b的信号gateline处于高电平期间被充电。

77.图8以时序图的形式例示了检测器12的另一操作示例,检测器12实现如图5所示的驱动器模块,驱动器模块仍然被链接成两组而这次用于连续行的像素的共同读出的。换句话说,连续的偶数行和奇数行被同时读出。在借助图8描述的操作中,令牌ina与令牌inb同时发送。同样,时钟clk1a、clk2a、clk3a和clk4a与相应的时钟clk1b、clk2b、clk3b和clk4b同时发送。因此,信号outa(1)与outa(2)、outa(3)与outa(4)、gateline(1)与gateline(2)、gateline(3)与gateline(4)是同时的。

78.图8的操作类似于图6的操作,在信号gateline(2)与gateline(3)之间具有死区时间tm。为了限制该死区时间的持续时间,时钟clk3a和clk3b的高电平的持续时间短于这些相同时钟的低电平的持续时间。

79.配备有彼此链接的多组驱动器模块的检测器12使得可以根据需要选择各种操作模式,特别是矩阵阵列的像素的单独读出,同时提供了消除矩阵阵列的两个连续行的两个

读出之间的任何死区时间的可能性。检测器12还使得可以将源自多个像素的信号分组在一起以进行共同读出。

80.针对像素p的矩阵阵列的读出,给出了两个操作示例。在图1的图中,行导体l用于驱动晶体管t(i,j)的断开。该晶体管用于各个像素p(i,j)的读出和重置两者。对于读出和重置,可以以相同或不同的方式来驱动像素,例如单独读出和集体重置。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。