1.本发明涉及一种片上存储空间动态配置方法,属于cache空间配置技术领域。

背景技术:

2.众核处理器架构中控制核主要负责控制及任务分发调度等功能,计算核主要完成计算加速任务。少量的控制核与大量的计算核是众核处理器架构中的一个经典结构。计算核直接访问主存性能开销太大,所以一般都配备有多级存储层次,采用主存与片上存储器是其中的一个典型配置,在此配置下,每个计算核具有一块高速的本地局部数据存储空间,该空间可配置成完全由软件管理的常规片上本地/局部数据存储器(local data memory,ldm),也可部分容量配置成硬件自动管理的数据cache,两种管理方式的容量配比分档可调。针对不同的应用场景,cache与ldm的作用各有优缺点,传统方式是在程序启动时配置好cache与ldm的容量。

3.众核处理器架构中计算核的本地局部数据存储空间配置成软件管理的ldm时,计算核可以使用访问ldm空间的load/store的方式加以访问,也可以使用发起异步dma的方式实现ldm与外界(主存或者其他计算核的ldm)的数据批量交换,这种使用方式下,一般要求dma访问的数据量比较大,连续性较好,访问ldm空间的访存操作性能比较高;部分空间配置为数据cache时,计算核可以通过访问主存空间的load/store的方式对该空间加以访问,这种访问方式对访问数据的连续性以及数据量都没有要求,使用方式比较灵活,但是访问主存的访存操作的性能比较差,同时因为众核处理器计算核数量很多,难以通过硬件保证cache一致性,需要软件来保证控制核-计算核、计算核之间cache的一致性。

4.众核处理器发展至今,对软件管理的局部数据存储空间的技术使用已经比较成熟,但是对于众多计算核中cache的应用尚无统一的规范。对于ldm/cache这种配置方式来说,传统方式是在程序启动时配置好cache与ldm的容量,但是,因为ldm与cache的使用方式不同,他们所适用的应用场景、对程序特征的需求也不相同。计算核的本地局部数据存储空间的总容量是不变的,固定的ldm/cache配置使得当其中一项的空间不足时,无法有效利用另外一项的空间来提升程序的性能。

技术实现要素:

5.本发明的目的是提供一种片上存储空间动态配置方法,其可以避免固定配置下因为ldm或者cache容量不足造成的性能损失,最大程度发挥其性能优势。

6.为达到上述目的,本发明采用的技术方案是:提供一种片上存储空间动态配置方法,包括以下步骤:s1、读取输入参数,根据硬件提供的可支持的cache容量配置大小,判断该输入参数是否为硬件所支持的容量大小的一种,如果是,则进行下一步,并将该输入参数记为new_cache_size,否则报错退出并提醒该输入参数错误;s2、读取硬件的ldm配置寄存器,获取当前配置下的cache容量大小,记为old_

cache_size;s3、获取计算核栈空间大小及计算核的栈指针;s4、对new_cache_size和old_cache_size进行比较,如果new_cache_size大于old_cache_size,则转到s5执行,否则转到s6执行;s5、在ldm空间中分配一块与计算核栈空间大小相等的局存空间mem_a,并将计算核栈空间转移至新分配的该局存空间中;s6、通过判回答字确认本计算核相关的dma操作均已完成,通过硬件的memb指令确认本计算核之前发出的访存操作均已完成;s7、刷新计算核cache以保证cache一致性,将ldm配置寄存器的值置为new_cache_size以对cache容量重新进行配置,通过硬件的memb指令确保后续的访存操作使用新的配置;s8、对new_cache_size和old_cache_size进行比较,如果new_cache_size大于old_cache_size,则转到s9执行,否则转到s10执行;s9、将mem_a中的计算核栈空间重新转移至紧挨着新的cache空间的ldm空间中,释放mem_a空间,转到s11执行;s10、将计算核栈空间转移至紧挨着新的cache空间的ldm空间中;s11、将计算核栈指针指向新的计算核栈空间末尾位置,配置结束。

7.上述技术方案中进一步改进的方案如下:1. 上述方案中,将所述配置方法封装为函数接口供用户使用,所述输入参数为用户希望配置的cache容量。

8.由于上述技术方案的运用,本发明与现有技术相比具有下列优点:本发明提供了在运行时动态配置cache与ldm的方法,可以根据程序不同阶段的特征对cache以及ldm的需求灵活配置其容量,避免固定配置下因为ldm或者cache容量不足造成的性能损失,最大程度发挥其性能优势。

附图说明

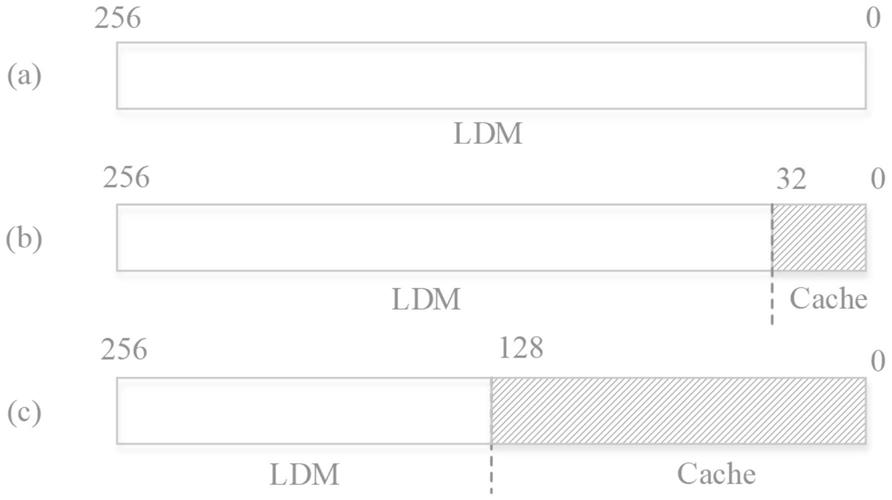

9.附图1为本发明提出的计算核ldm/cache配置结构图;附图2为本发明提出的计算核栈空间分配示意图;附图3为本发明方法流程图。

具体实施方式

10.实施例:本发明提供一种片上存储空间动态配置方法,具体包括以下步骤:s1、读取输入参数,根据硬件提供的可支持的cache容量配置大小,判断该输入参数是否为硬件所支持的容量大小的一种,如果是,则进行下一步,并将该输入参数记为new_cache_size,否则报错退出并提醒该输入参数错误;s2、读取硬件的ldm配置寄存器,获取当前配置下的cache容量大小,记为old_cache_size;s3、获取计算核栈空间大小及计算核的栈指针;s4、对new_cache_size和old_cache_size进行比较,如果new_cache_size大于

old_cache_size,则转到s5执行,否则转到s6执行;s5、在ldm空间中分配一块与计算核栈空间大小相等的局存空间mem_a,并将计算核栈空间转移至新分配的该局存空间中;s6、通过判回答字确认本计算核相关的dma操作均已完成,通过硬件的memb指令确认本计算核之前发出的访存操作均已完成;s7、刷新计算核cache以保证cache一致性,将ldm配置寄存器的值置为new_cache_size以对cache容量重新进行配置,通过硬件的memb指令确保后续的访存操作使用新的配置;s8、对new_cache_size和old_cache_size进行比较,如果new_cache_size大于old_cache_size,则转到s9执行,否则转到s10执行;s9、将mem_a中的计算核栈空间重新转移至紧挨着新的cache空间的ldm空间中,释放mem_a空间,转到s11执行;s10、将计算核栈空间转移至紧挨着新的cache空间的ldm空间中;s11、将计算核栈指针指向新的计算核栈空间末尾位置,配置结束。

11.将所述配置方法封装为函数接口供用户使用,所述输入参数为用户希望配置的cache容量。

12.对上述实施例的进一步解释如下:计算核中的本地局部数据存储空间如图1所示:其总大小为256kb,硬件支持配置成三种形式:(a)全部配置成常规片上本地局部数据存储器ldm;(b)部分配置成硬件自动管理的cache(大小为32kb),其他部分为ldm;(c)部分配置成硬件自动管理的数据cache(大小为128kb),其他部分为ldm;当配置成cache时,硬件cache采用4路组相联策略,支持硬件淘汰和装填。

13.因为众核处理器中计算核数量非常多,硬件实现计算核cache一致性的代价非常巨大,难以实现,因此计算核cache的一致性需要由软件来保证。

14.本地局部数据存储空间的配置结构由硬件的ldm配置寄存器来控制实现,给ldm配置寄存器赋以不同的值代表实现了不同的局存空间配置,此外,由于硬件不支持计算核cache的一致性,动态配置局存空间是还需要保证cache中数据的一致性问题。

15.此外,为了提升性能,一般将计算核的栈空间存放到局存空间中,在此过程中也要保证栈空间数据的正确性。计算核的栈空间在局存中的存放位置如图2所示(以cache大小32kb为例):计算核栈空间存放于ldm中,但是为了与其他的计算核数据相区分且尽量避免空间重叠冲突,计算核栈空间是紧挨着划分出的cache空间存放的。

16.本专利根据计算核的本地局部数据存储空间中cache与ldm不同的使用方式以及他们对程序性能的不同影响,通过提供封装好的函数接口,允许用户在程序运行过程中根据不同应用场景、程序特征对ldm或者cache不同的容量需求动态配置计算核ldm/cache的容量,避免固定配置下因为ldm或者cache容量不足造成的性能损失,提升程序的性能,且配置过程则对用户透明,方便用户使用。

17.根据局存空间可配置的特征,提供封装好的函数接口供程序员使用,对ldm及cache容量进行动态配置,配置过程对用户透明,避免ldm或者cache容量不足带来的性能损

失;根据配置前后cache容量对比,对计算核栈空间的转移选择不同的方式,既保证计算核栈空间不被破坏又能尽可能提高配置的速度;在配置计算核cache容量前后,通过判dma回答字、判访存操作是否结束、插入memb指令、刷新计算核cache等操作来确保计算核内部处于一个稳定的一致状态,确保cache的一致性以及程序正确性。

18.本发明提出片上存储空间动态配置方法,以封装的函数接口提供给用户使用,输入参数为用户希望配置的cache容量,具体的流程图如图3所示,简述如下:1)读取输入参数,判断该参数是否为硬件支持的可配置cache容量大小,是则进行下一步,我们将该参数记为new_cache_size;否则报错退出并提醒用户输入参数错误;2)读取硬件的ldm配置寄存器,获取当前配置下的cache容量大小,记为old_cache_size;3)获取计算核栈空间大小及计算核的栈指针;4)对new_cache_size和old_cache_size进行比较,如果new_cache_size大于old_cache_size,则转到第5步执行,否则转到第6步执行;5)在ldm空间中分配一块与计算核栈空间大小相等的局存空间mem_a,并将计算核栈空间转移至新分配的该局存空间中;6)通过判回答字确认本计算核相关的dma操作均已完成,通过硬件的memb指令确认本计算核之前发出的访存操作均已完成;7)刷新计算核cache以保证cache一致性;将ldm配置寄存器的值置为new_cache_size以对cache容量重新进行配置,通过硬件的memb指令确保后续的访存操作使用新的配置;8)如果new_cache_size大于old_cache_size,则转到第9步执行,否则转到第10步执行;9)将mem_a中的计算核栈空间重新转移至紧挨着新的cache空间的ldm空间中;释放mem_a空间;转到第11步执行;10)将计算核栈空间转移至紧挨着新的cache空间的ldm空间中;11)将计算核栈指针指向新的计算核栈空间末尾位置,配置结束。

19.假设当前配置下计算核cache容量为32kb,用户重新配置cache的输入参数为128kb,简要过程大致如下:1)读取输入参数以及硬件的ldm配置寄存器的值,new_cache_size=128kb,old_cache_size=32kb,同时获取计算核空间大小及栈指针的值,假设当前计算核栈空间大小为8kb,则计算核栈指针的值为40(32 8)kb;2)因为new_cache_size》 old_cache_size,所以我们在常规ldm空间上新申请一块8kb的空间mem_a,并将计算核栈空间上的8kb数据都转移至mem_a中;3)确认本计算核相关的dma操作以及访存操作都完成后,刷新计算核cache,将ldm配置寄存器的值置为128kb以重新配置cache的容量,插入memb指令以保证后续操作都使用新的配置;4)将mem_a中的8kb数据(计算核栈空间)都重新转移至新配置下与cache空间紧挨

着的常规ldm空间中,释放mem_a空间;更新计算核栈指针,此时计算核栈指针的值为136(128 8)kb。

20.采用上述一种片上存储空间动态配置方法时,其可以根据程序不同阶段的特征对cache以及ldm的需求灵活配置其容量,避免固定配置下因为ldm或者cache容量不足造成的性能损失,最大程度发挥其性能优势。

21.为了便于更好的理解本发明,下面将对本文中使用的术语进行简要的解释:cache:高速缓冲存储器,一种特殊的存储器子系统,介于中央处理器cpu与主存储器之间的高速小容量存储器。

22.ldm:local data memory,本地/局部数据存储器。

23.dma:direct memory access,直接内存访问,是一种不经过cpu而直接从内存存取数据的数据交换模式。

24.上述实施例只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。