技术特征:

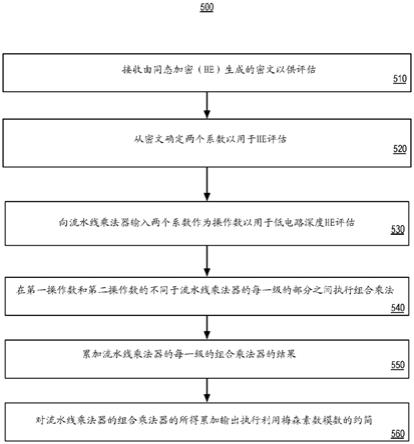

1.一种装置,包括:硬件加速器,用于:接收由同态加密(he)生成的密文以用于评估;确定密文的两个系数以用于he评估;将两个系数作为第一操作数和第二操作数输入到流水线乘法器以用于低电路深度he评估;在第一操作数和第二操作数的部分之间执行组合乘法;累加流水线乘法器的每一级处的组合乘法的结果;以及对流水线乘法器的组合乘法器的所得累加输出执行利用梅森素数模数的约简。2.根据权利要求1所述的装置,其中流水线乘法器包括多个级,并且其中多个级的数量基于第一操作数和第二操作数的输入大小。3.根据权利要求1所述的装置,其中梅森素数模数是梅森素数结构或广义梅森素数结构中的至少一个。4.根据权利要求3所述的装置,其中流水线乘法器包括额外的级以适应执行利用梅森素数模数的约简,所述梅森素数模数是广义梅森素数结构。5.根据权利要求1所述的装置,其中第二操作数的部分随着流水线乘法器的每一级而不同,并且其中第二操作数的部分从最低有效位到最高有效位被输入到流水线乘法器的级。6.根据权利要求1所述的装置,其中硬件加速器还包括组合乘法器电路、加法器电路、流水线寄存器和约简加法器电路的集合。7.根据权利要求1所述的装置,其中he评估被提供用于低电路深度应用。8.根据权利要求1所述的装置,其中用于累加组合乘法的结果的硬件加速器还包括将流水线乘法器中当前组合乘法器的对齐结果与流水线乘法器中紧接在前的数据路径的结果相累加。9.根据权利要求1所述的装置,其中通过流水线乘法器的组合乘法以流水线方式执行,使得在流水线乘法器的每个时钟周期中存在输入到流水线乘法器中的两个不同的操作数。10.一种方法,包括:由计算设备的硬件加速器接收由同态加密(he)生成的密文以用于评估;确定密文的两个系数以用于he评估;将两个系数作为第一操作数和第二操作数输入到流水线乘法器以用于低电路深度he评估;由硬件加速器在第一操作数和第二操作数的部分之间执行组合乘法;累加流水线乘法器的每一级处的组合乘法的结果;以及由硬件加速器对流水线乘法器的组合乘法器的所得累加输出执行利用梅森素数模数的约简。11.根据权利要求10所述的方法,其中流水线乘法器包括多个级,并且其中多个级的数量基于第一操作数和第二操作数的输入大小。12.根据权利要求10所述的方法,其中梅森素数模数是梅森素数结构或广义梅森素数结构中的至少一个。

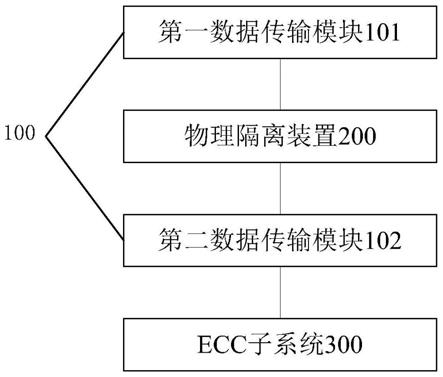

13.根据权利要求10所述的方法,其中第二操作数的部分随着流水线乘法器的每一级而不同,并且其中第二操作数的部分从最低有效位到最高有效位被输入到流水线乘法器的级。14.根据权利要求10所述的方法,其中硬件加速器包括组合乘法器电路、加法器电路、流水线寄存器和约简加法器电路的集合。15.根据权利要求10所述的方法,其中he评估被提供用于低电路深度应用。16.根据权利要求10所述的方法,其中通过流水线乘法器的组合乘法以流水线方式执行,使得在流水线乘法器的每个时钟周期中存在输入到流水线乘法器中的两个不同的操作数。17.一种系统,包括:存储器;以及可通信地耦合到存储器的硬件加速器,所述硬件加速器用于实现流水线乘法器,其包括组合乘法器电路、加法器电路、流水线寄存器和约简加法器电路的集合,所述集合用于:接收由同态加密(he)生成的密文以用于评估;确定密文的两个系数以用于he评估;将两个系数作为第一操作数和第二操作数输入到流水线乘法器以用于低电路深度he评估;在第一操作数和第二操作数的部分之间执行组合乘法;累加流水线乘法器的每一级处的组合乘法的结果;以及对流水线乘法器的组合乘法器的所得累加输出执行利用梅森素数模数的约简。18.根据权利要求17所述的系统,其中流水线乘法器包括多个级,并且其中多个级的数量基于第一操作数和第二操作数的输入大小。19.根据权利要求17-18中的任一项所述的系统,其中梅森素数模数是梅森素数结构或广义梅森素数结构中的至少一个。20.根据权利要求17-19中的任一项所述的系统,其中he评估被提供用于低电路深度应用。21.包括多个指令的至少一个机器可读介质,所述多个指令响应于在计算设备上被执行而使计算设备执行根据权利要求10-16中的任一项所述的方法。22.一种用于促进低电路深度同态加密评估的装置,其包括用于执行根据权利要求10-16中的任一项所述的方法的部件。

技术总结

各种实施例涉及低电路深度同态加密评估。一种装置的实施例包括:硬件加速器,用于:接收由同态加密(HE)生成的密文以用于评估;确定密文的两个系数以用于HE评估;将两个系数作为第一操作数和第二操作数输入到流水线乘法器以用于低电路深度HE评估;在第一操作数和第二操作数的部分之间执行组合乘法;累加流水线乘法器的每一级处的组合乘法的结果;以及对流水线乘法器的组合乘法器的所得累加输出执行利用梅森素数模数的约简。梅森素数模数的约简。梅森素数模数的约简。

技术研发人员:S

受保护的技术使用者:英特尔公司

技术研发日:2021.08.18

技术公布日:2022/3/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。