存储器系统

1.相关申请

2.本技术享受以日本专利申请2020-157075号(申请日:2020年9月18日)为基础申请的优先权。本技术通过参考此基础申请而包括基础申请的全部内容。

技术领域

3.本发明的实施方式涉及存储器系统。

背景技术:

4.读出由存储器系统所存储的数据的动作通过对与存储单元连接的字线施加判定电压而进行。在存储器系统被带出的情况下等,容易进行对该存储器系统的数据的访问的可能性高。

技术实现要素:

5.本发明要解决的技术问题在于,提供一种能够实现数据的保密性的提高的存储器系统。

6.实施方式的存储器系统,具有非易失性存储器和控制非易失性存储器的控制器。控制器构成为,基于存储器系统所存在的位置来生成与数据的加密及解密相关的信息,使用所述信息,将向非易失性存储器写入的写入数据的加密或从非易失性存储器读出的读出数据的解密中的至少一个处理设为可能的状态。

附图说明

7.图1是表示第一实施方式的第一信息处理装置的结构的一例的图。

8.图2是表示第一实施方式的基准电压信息的一例的图。

9.图3是表示第一实施方式的通信处理装置的结构的框图。

10.图4是表示第一实施方式的第一规定范围的设定的一例的图。

11.图5是表示第一实施方式的存储器芯片的结构的一例的框图。

12.图6是表示第一实施方式的存储单元阵列的构成的一例的图。

13.图7是表示第一实施方式的存储单元的阈值电压分布的一例的图。

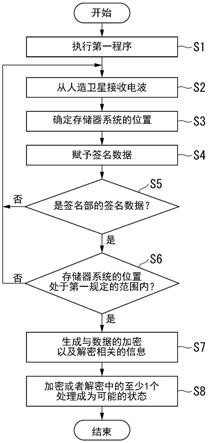

14.图8是表示第一实施方式的存储器系统的处理流程的一例的图。

15.图9是表示第一实施方式的第一变形例的cpu的结构的一例的图。

16.图10是表示第一实施方式的第一变形例的nand控制器的一例的图。

17.图11是表示第一实施方式的第一变形例的cpu及nand控制器的结构的一例的图。

18.图12是表示第一实施方式的第二变形例的存储器控制器的结构的一例的图。

19.图13是表示第二实施方式的通信处理装置的结构的一例的图。

20.图14是表示第二实施方式的存储器系统的处理流程的一例的图。

21.图15是表示第二实施方式的第一变形例的cpu的结构的一例的图。

22.图16是表示第二实施方式的第一变形例的nand控制器的结构的一例的图。

23.图17是表示第二实施方式的第一变形例的cpu及nand控制器的结构的一例的图。

24.图18是表示第二实施方式的第二变形例的存储器控制器的结构的一例的图。

25.图19是表示第三实施方式的信息处理系统的结构的一例的图。

26.图20是表示第三实施方式的第二信息处理装置的结构的一例的图。

27.图21是表示第三实施方式的通信处理装置的结构的一例的图。

28.图22是表示第三实施方式的第二规定范围的一例的图。

29.图23是表示第三实施方式的存储器系统的处理流程的一例的图。

30.图24是表示第三实施方式的第一变形例的cpu的结构的一例的图。

31.图25是表示第三实施方式的第一变形例的nand控制器的结构的一例的图。

32.图26是表示第三实施方式的第一变形例的cpu及nand控制器的结构的一例的图。

33.图27是表示第三实施方式的第二变形例的存储器控制器的结构的一例的图。

34.图28是表示与时间戳服务器连接的第四实施方式的信息处理系统的结构的一例的图。

35.图29是表示第四实施方式的第二信息处理装置的结构的一例的图。

36.图30是表示第四实施方式的通信处理装置的结构的一例的图。

37.图31是表示第四实施方式的规定的时刻的范围的一例的图。

38.图32是表示第四实施方式的存储器系统的处理流程的一例的图。

39.图33是表示第四实施方式的第一变形例的cpu的结构的一例的图。

40.图34是表示第四实施方式的第一变形例的nand控制器的结构的一例的图。

41.图35是表示第四实施方式的第一变形例的cpu及nand控制器的结构的一例的图。

42.图36是表示第四实施方式的第二变形例的存储器控制器的结构的一例的图。

具体实施方式

43.以下,参照附图对实施方式的信息处理系统进行说明。在以下的说明中,有时对具有相同或类似的功能的结构标注相同的附图标记,并省略重复的说明。在本说明书中,“基于xx”是指“至少基于xx”,也包括除了xx之外还基于其他要素的情况。另外,“基于xx”并不限定于直接使用xx的情况,也包括基于对xx进行了运算、加工的情况。“xx”是任意的要素(例如任意的信息)。

44.在本说明书中,有时将“读出”称为“读(read)”,有时将“写入”称为“写(write)”。另外,在本说明书中,“写入”、“存储”、“保存”相互以相同的意思而使用。因此,这些用语能够相互替换。在本说明书中,“连接”不限定于机械连接,包括电连接。本说明书中的构成要素“取得”并不限定于从该构成要素的外部得到的情况,也包括该构成要素自己算出的情况。在本说明书中,“每个位线”、“位线单位”能够与“每个列(column)”、“列(column)单位”相互替换。

45.另外,在本说明书中,“使用yy进行加密/解密”,不限定于直接使用yy(即,使用yy本身作为密钥信息)进行加密/解密的情况,也包括间接地使用yy(例如,使用对yy进行运算、加工而生成的密钥信息)而进行加密/解密的情况。“yy”是任意的要素(例如任意的信息)。

46.(第一实施方式)

47.<第一信息处理装置的结构>

48.图1是表示第一实施方式的第一信息处理装置10的结构的一例的图。第一信息处理装置10具备存储器系统20a和主机装置20b。在第一信息处理装置10中,基于存储器系统20a所存在的位置,限制对该存储器系统20a的访问。第一信息处理装置10例如设置于数据中心。

49.存储器系统20a与主机装置20b连接。主机装置20b例如是服务器装置、个人计算机或移动式的信息处理装置。存储器系统20a作为主机装置20b的外部存储装置发挥功能。主机装置20b能够发出针对存储器系统20a的访问请求(读请求以及写请求)。

50.存储器系统20a具备存储器控制器201、nand存储器202、天线203以及通信处理装置204。存储器控制器201与nand存储器202通过多个通道连接。天线203与通信处理装置204通过信号线连接。通信处理装置204与存储器控制器201通过信号线连接。存储器控制器201是“控制器”的一例。nand存储器202是“存储器装置”的一例。存储器控制器201、nand存储器202、天线203以及通信处理装置204例如被安装在印刷电路板上。

51.天线203接收从gnss(global navigation satellite system:全球导航卫星系统)的人造卫星发送的电波。另外,作为gnss的例子,列举出gps(global positioning system:全球定位系统)。

52.存储器控制器201包括:主机接口控制器(主机i/f控制器)2011、ram(random access memory:随机存取存储器)2012、rom(read only memory:只读存储器)2013、cpu(central processing unit:中央处理单元)2014、ecc(error correcting code:错误修正码)电路2015以及nand控制器2016。这些功能部通过总线相互连接。例如,存储器控制器201由这些功能部被安装于1个芯片而成的soc(system on a chip:片上系统)那样的半导体集成电路构成。但是,这些功能部的一部分也可以设置于存储器控制器201的外部。

53.主机i/f控制器2011在cpu2014的控制下,执行主机装置20b与存储器系统20a之间的通信接口的控制、以及主机装置20b与ram2012之间的数据转送的控制。

54.ram2012例如是sdram(synchronous dynamic random access memory:同步动态随机存取存储器)或sram(static random access memory:静态随机存取存储器),但并不限定于这些。ram2012作为用于主机装置20b与nand存储器202之间的数据转送的缓冲器发挥功能。另外,ram2012向cpu2014提供工作区域。在存储器系统20a的动作时,在ram2012中被加载已被存储于nand存储器202或rom2013中的固件(程序)。

55.cpu2014是硬件处理器的一例。cpu2014例如通过执行被加载到ram2012的固件来执行各种处理。关于cpu2014的结构和cpu2014进行的处理的详细情况在后面叙述。另外,也可以针对每个处理设置多个cpu2014。

56.ecc电路2015针对向nand存储器202写入的写入对象的数据(以下,也称为“写入数据”)进行用于纠错的编码。ecc电路2015在从nand存储器202读出的数据(以下,也称为“读出数据”)中包括错误的情况下,基于在写入动作时赋予的纠错码,对读出数据执行纠错。

57.nand控制器2016控制各通道(ch.0,ch.1)。nand控制器2016在cpu2014的控制下,执行ram2012与nand存储器202之间的数据转送的控制。

58.nand存储器202具有多个(在此为4个)非易失性半导体存储器芯片2021。在本实施

方式中,存储器控制器201具有2个通道(ch.0、ch.1)。存储器控制器201也可以具有1个或3个以上的通道。在图1所示的例子中,在各通道连接有2个存储器芯片2021。此外,也可以在各通道上连接3个以上的存储器芯片2021。各通道包括i/o(input/output)信号线、控制信号线、ce(芯片使能)信号线、ry(就绪)/by(忙碌)信号线。i/o信号线对数据、地址以及各种命令进行传输。存储器控制器201经由i/o信号线将读出命令、写入命令和擦除命令发送至存储器芯片2021。控制信号线包括we(写使能)信号线、re(读使能)信号线、(命令锁存使能)信号线、ale(地址锁存使能)信号线、wp(写保护)信号线等。ce信号线传输表示存储器芯片2021处于选择中这一情况的信号。ry/by信号线传输表示nand存储器202是否处于动作中这一情况的信号。ry/by信号线例如以高电平表示与非动作中对应的就绪状态(ry),以低电平表示与动作中对应的忙碌状态(by)。

59.在存储器系统20a的动作开始时,例如,存储于存储器芯片2021中的判定电压信息2012a被加载到ram2012中。判定电压信息2012a是在对nand存储器202的读出动作中用于决定对后述的各字线wl施加的判定电压的值的设定信息。判定电压信息2012a包括基准电压信息2012b。存储器芯片2021所包括的存储单元根据阈值电压而非易失性地存储数据。存储单元的阈值电压可能由于编程干扰(program disturb)、读干扰(read disturb)或数据保留(data retention)等应力(stress)的影响而变化,因此判定电压信息2012a也可以包括用于修正判定电压的修正值的信息。

60.图2是表示判定电压信息2012a所包括的基准电压信息2012b的一例的图。在图2中,vad~vog的值分别是对判定电压va~vg的基准值(例如初始设定值)进行表示的值。基准电压信息2012b也可以针对多个存储器芯片2021共通地设定(相同的值)。基准电压信息2012b可以针对每个存储器芯片2021单独地设定。

61.存储器控制器201基于判定电压信息2012a计算出对各字线wl施加的判定电压的值。存储器控制器201向nand存储器202指示施加计算出的值的判定电压。

62.<通信处理装置的结构>

63.图3是表示通信处理装置204的结构的一例的图。通信处理装置204作为取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、以及访问处理部204f发挥功能。通信处理装置204例如是cpu(central processing unit:中央处理单元)、fpga(field programmable gate array:现场可编程门阵列)、asic(application specific integrated circuit:专用集成电路)这样的半导体集成电路。

64.取得部204a从人造卫星经由天线203接收电波。

65.确定部204b基于取得部204a接收到的电波,确定存储器系统20a的位置。例如,确定部204b基于取得部204a从4个不同的人造卫星分别接收到的电波,确定存储器系统20a的位置。具体而言,电波中包括发送该电波的人造卫星固有的标识符的信息和发送了该电波的时刻的信息。确定部204b根据电波的传播速度(即,光速)、电波的发送时刻以及电波的接收时刻,计算存储器系统20a与4个人造卫星各自的距离。然后,确定部204b通过确定所求出的4个距离交于1个的点,来确定存储器系统20a的位置。此外,如果在计算上有3个距离的信息,则能够确定存储器系统20a的位置,但在各时刻包括由时钟的精度引起的微小的误差。因此,确定部204b进行对3个距离的信息追加另一个距离的信息来修正误差的处理。另外,位置例如由纬度及经度表示。但是,位置可以是除了纬度及经度之外还由标高来表示的位

置。

66.签名部204c对确定部204b所确定的存储器系统20a的位置数据赋予规定的签名数据。例如,签名部204c基于rsa算法,使用私钥((security key))对位置数据赋予规定的签名数据。私钥保存在例如usb(universal serial bus:通用串行总线)加密狗(dogle)等硬件安全模块设备中。通过由签名部204c进行的该处理,以后能够防止由确定部204b所确定的存储器系统20a的位置的篡改。

67.第一判定部204d判定由确定部204b所确定的存储器系统20a的位置是否处于第一规定范围内。第一规定范围被设定为能够从外部经由主机装置20b访问存储器系统20a的存储器系统20a的位置。例如,在设定某数据中心的内部作为第一规定范围的的情况下,考虑基于确定部204b的存储器系统20a的位置的确定精度以及数据中心的广度,针对数据中心的纬度和经度分别设定允许范围。第一规定范围例如在存储器系统20a的动作开始时,从存储器芯片2021被加载到ram2012中。图4是表示第一规定范围的设定的一例的图。在图4中,针对设置有存储器系统20a的纬度及经度,规定关于纬度的允许范围和关于经度的允许范围,由此示出了第一规定范围。第一判定部204d读出与这样的第一规定范围有关的信息。第一判定部204d通过将读出的第一规定范围与确定部204b所确定的存储器系统20a的位置进行比较,由此能够判定存储器系统20a的位置是否处于第一规定范围内。

68.生成部204e基于确定部204b所确定的存储器系统20a的位置,生成对数据进行加密时所使用的加密密钥。生成部204e可以生成根据存储器系统20a的位置而不同的加密密钥。加密密钥是与数据的加密及解密相关的信息的一例。例如,在第一判定部204d判定为存储器系统20a的位置处于第一规定范围内的情况下,生成部204e生成加密密钥。另外,在第一判定部204d判定为存储器系统20a的位置处于第一规定范围外的情况下,生成部204e不生成加密密钥。

69.另外,生成部204e在存储器系统20a从外部经由主机装置20b接收到数据的读出请求的情况下,基于确定部204b所确定的存储器系统20a的位置,生成在对已被加密的数据进行解密时所使用的解密密钥。生成部204e可以生成根据存储器系统20a的位置而不同的解密密钥。解密密钥是与数据的加密及解密相关的信息的一例。例如,在存储器系统20a从外部经由主机装置20b接收到数据的读出请求、且第一判定部204d判定为存储器系统20a的位置处于第一规定范围内的情况下,生成部204e生成解密密钥。另外,在存储器系统20a从外部经由主机装置20b接收到数据的读出请求、且第一判定部204d判定为存储器系统20a的位置处于第一规定范围外的情况下,生成部204e不生成解密密钥。

70.另外,生成部204e使用规定的公钥来判定对存储器系统20a的位置数据赋予的签名数据是否是签名部204c的签名数据。规定的公钥与签名部204c在签名数据的赋予中使用的私钥成对。即,规定的公钥是将签名数据解密为生成部204e能够读取的数据的公钥。

71.访问处理部204f在生成部204e生成了与数据的加密及解密相关的信息的情况下,使用生成部204e生成的与数据的加密及解密相关的信息,将cpu2014对向nand存储器202写入的数据进行加密的处理、或者cpu2014对从nand存储器202读出的数据进行解密的处理中的至少一个处理设为可能的状态。

72.例如,在存储器系统20a接收到数据的写入请求,生成部204e生成了加密密钥的情况下,访问处理部204f将生成部204e生成的加密密钥发送至存储器控制器201。存储器控制

器201的cpu2014使用加密密钥对向nand存储器202写入的写入数据进行加密。然后,存储器控制器201的nand控制器2016将加密后的数据向nand存储器202写入。

73.另外,例如,在存储器系统20a接收到数据的读出请求,生成部204e生成了解密密钥的情况下,访问处理部204f将生成部204e生成的解密密钥发送至存储器控制器201。存储器控制器201的nand控制器2016从nand存储器202读出已被加密的数据。然后,存储器控制器201的cpu2014使用生成部204e生成的解密密钥,对从nand存储器202读出的已被加密的数据进行解密。

74.<存储器芯片的结构>

75.图5是表示存储器芯片2021的结构的一例的图。存储器芯片2021例如具有i/o信号处理电路2021a、控制信号处理电路2021b、芯片控制电路2021c、ry/by生成电路2021d、命令寄存器2021e、地址寄存器2021f、行解码器2021g、列解码器2021h、数据寄存器2021i、读出放大器2021j以及存储单元阵列2021k。

76.i/o信号处理电路2021a是用于在存储器控制器201与存储器芯片2021之间收发i/o信号的缓冲电路。i/o信号处理电路2021a锁存的命令、用于指定访问目的地的地址、以及数据分别被保存在命令寄存器2021e、地址寄存器2021f、以及数据寄存器2021i中。

77.保存在地址寄存器203f中的地址包括芯片编号、行地址以及列地址。芯片编号是用于区分存储器芯片2021的识别信息。芯片编号、行地址以及列地址分别被读出到芯片控制电路2021c、行解码器2021g以及列解码器2021h。

78.控制信号处理电路2021b接受控制信号。控制信号处理电路2021b基于接受到的控制信号,执行i/o信号处理电路2021a接受到的i/o信号的保存目的地的寄存器的分配。此外,控制信号处理电路2021b将接受到的控制信号转送至芯片控制电路2021c。

79.芯片控制电路2021c是基于经由控制信号处理电路2021b接收的各种控制信号而进行状态转变的电路。芯片控制电路2021c控制存储器芯片2021的操作。

80.ry/by生成电路208d在芯片控制电路2021c的控制下使ry/by信号线的状态在就绪状态(ry)与忙碌状态(by)之间转变。

81.读出放大器2021j在读出动作中读出存储单元阵列2021k所包括的存储单元mt(参照图6)的状态。读出放大器2021j基于所读出的状态生成读出数据。读出放大器2021j将所生成的读出数据保存在数据寄存器2021i中。保存在数据寄存器2020i中的读出数据通过数据线被发送至i/o信号处理电路2021a,并从i/o信号处理电路2021a向存储器控制器201转送。

82.存储单元阵列2021k具有多个存储单元mt,并存储数据。若详细地叙述,则存储单元阵列2021k具有多个物理区块blk(参照图6)。各物理区块blk包括多个存储单元mt。物理区块blk是数据擦除的最小单位。即,存储于1个物理区块blk的全部数据一并被擦除。以下,将“物理区块”简称为“区块”。

83.关于行解码器2021g、列解码器2021h的动作,在后面叙述。

84.<存储单元阵列的结构>

85.图6是表示存储单元阵列2021k的结构的一例的图。存储单元阵列2021k例如是将多个存储单元mt配置为立体状的三维构造的nand存储器。存储单元阵列2021k具有多个区块blk(blk0,blk1,

…

)。例如,存储单元阵列2021k具有数百至数千的区块blk。

86.如图6所示,m(m为自然数)条位线bl(bl0~blm-1)分别在各区块blk中与多个(例如m个)串str连接。各串str包括1个第一选择栅极晶体管st、多个存储单元mt(mt0~mt7)及1个第二选择栅极晶体管dt。第一选择栅极晶体管st、多个存储单元mt及第二选择栅极晶体管dt按此顺序在源极线celsrc与1个位线bl之间串联连接。与不同的多个位线bl(bl0~blm-1)分别连接的多个(m个)串str构成1个串单元su。各区块blk包括多个(例如4个)串单元su(su0~su3)。

87.第一选择栅极晶体管st的控制栅极电极与第一选择栅极线(源极侧选择栅极线)sgsl连接。第一选择栅极线sgsl是对第一选择栅极晶体管st的控制栅极电极进行控制的控制信号线。第一选择栅极晶体管st基于通过第一选择栅极线sgsl施加的电压,将多个存储单元mt与源极线celsrc之间选择性地连接。第一选择栅极线sgsl也可以针对每个串单元su(su0~su3)独立地连接。

88.第二选择栅极晶体管dt的控制栅极电极与第二选择栅极线(漏极侧选择栅极线)sgdl(sgdl0~sgdl3)连接。第二选择栅极线sgdl是对第二选择栅极晶体管dt的控制栅极电极进行控制的控制信号线。第二选择栅极晶体管dt基于通过第二选择栅极线sgdl施加的电压,将多个存储单元mt与位线bl之间选择性地连接。

89.各存储单元(存储单元晶体管)mt由具有层叠栅极构造的mosfet(metal oxide semiconductor field effect transistor:金属氧化物半导体场效应晶体管)构成。层叠栅极结构例如包括隔着隧道氧化膜而形成的浮动栅极和在浮动栅极上隔着栅极绝缘膜而形成的控制栅极电极。存储单元mt的阈值电压根据蓄积于浮动栅极的电荷的数量而变化。存储单元mt通过写入而向浮动栅极注入负的电荷,通过擦除从浮动栅极抽出负的电荷。各存储单元mt能够写入2个以上的数据值中的任意1个。各存储单元mt根据阈值电压的不同,非易失性地存储1个以上的数据值中的1个。

90.在各区块blk中,各存储单元mt的控制栅极电极连接于与各自对应的字线wl连接。例如,在存储单元mt0~mt7的控制栅极电极分别连接有字线wl0~wl7。各字线wl是用于选择在存储单元阵列2021k中排列为1行(1个行row)的一组存储单元mt的控制信号线,共通地连接于这些排列为1行的一组存储单元mt。各存储单元mt设置于字线wl与位线bl的交叉部。通过对与进行读出或写入的存储单元mt连接的字线wl(以下,也称为“选择字线wl”)施加某电压,从而能够进行存储单元mt的读出或写入。关于存储单元mt的读取及写入,在后面说明。

91.在各区块blk中,在不同的串str所包括的多个存储单元mt中共通地连接有与相同地址对应的字线wl。共享字线wl的多个存储单元晶体管mt的组被称为单元单位(cell unit)cu。1个单元单位cu所包括的多个存储单元mt一并被写入数据,并且一并被读出数据。1个单元单位cu的存储空间包括1个或多个页。

92.存储器系统20a能够构成为能够在各存储单元mt中存储多个比特的值。例如,在各存储单元mt能够存储n(n≥2)比特的值的情况下,每个字线wl(单元单位cu)的存储容量与n页的大小相等。在此,作为一个例子,对各存储单元mt以存储3比特的值的三层单元(tlc:triple level cell)模式进行动作的情况进行说明。

93.在三层单元(tlc)模式中,能够在各字线wl中存储3页量的数据。将一个字线wl所包括的3个页中的先进行写入的页称为低位页(low page),将低位页之后进行写入的页称

为中间页,将中间页之后进行写入的页称为高位页(up page)。另外,也可以存在对1个字线wl所包括的多个页面的一部分或全部页面一并执行编程(即写入)的模式。

94.<存储单元的阈值电压分布>

95.图7是表示存储单元mt的阈值电压分布的图。在图7中,横轴表示存储单元mt的阈值电压,纵轴表示具有某一阈值电压的存储单元mt的数量。在各存储单元mt以三层单元(tlc)模式进行动作的情况下,存储单元mt的阈值电压分布包括8个分布(lob)。

96.根据三层单元(tlc)模式,各存储单元mt能够存储由属于高位页的数据“x”、属于中间页的数据“y”、属于低位页的数据“z”定义的8值数据“xyz”。数据“x”、数据“y”以及数据“z”的值是符号“0”或者符号“1”。

97.各存储单元mt的阈值电压被控制为属于分布er、分布a、分布b、分布c、分布d、分布e、分布f、分布g这8个分布中的任一个。各分布与8值数据“xyz”的数据值之间的对应被预先设定。例如,对分布er分配数据值“111”。对分布a分配数据值“110”。对分布b分配数据值“100”。对分布c分配数据值“000”。对分布d分配数据值“010”。对分布e分配数据值“011”。对分布f分配数据值“001”。对分布g分配数据值“101”。另外,各分布与数据值之间的对应不限定于上述。

98.在此,也使用图5对nand存储器202的行解码器2021g、列解码器2021h、数据寄存器2021i及读出放大器2021j进行说明。行解码器2021g、列解码器2021h、数据寄存器2021i及读出放大器2021j是相对于存储单元阵列2021k而言的周边电路的一部分。周边电路基于芯片控制电路2021c的控制,执行对存储单元阵列2021k的访问(读出、写入及擦除)。

99.例如在写入动作中,列解码器2021h选择与列地址对应的位线bl并激活。读出放大器2021j将由列解码器2021h选择的位线bl的电位设为0伏特。行解码器2021g对与行地址对应的字线wl施加编程脉冲。编程脉冲例如是在每次施加时电压逐渐变高的脉冲。由此,向位于所选择的位线bl与所选择的字线wl的交叉部的存储单元晶体管mt的浮动栅极注入电荷。其结果,存储单元mt的阈值电压上升。读出放大器2021j在每次施加编程脉冲时,确认写入对象的存储单元mt的阈值电压是否达到与数据寄存器2021i中存储的数据对应的电压。根据读出放大器2021j的确认结果,行解码器2021g继续施加编程脉冲,直到存储单元mt的阈值电压达到与写入的数据值对应的电压为止。

100.另一方面,在读出动作中,读出放大器2021j对位线bl预充电电源电位vcc。行解码器2021g依次向选择字线wl施加用于确定每个数据值(“111”、“110”、“100”、“000”、“010”、“011”、“001”、“101”)的分布的多种判定电位(读取电压)。另外,行解码器2021g对非选择的字线wl施加读路径电位,将属于非选择的字线wl的存储单元晶体管mt设为导通状态。读出放大器2021j通过检测通过预充电而蓄积的电荷在被施加了哪个判定电压时向源极线celsrc流出,由此判定在对象的存储单元mt中存储的数据值。

101.例如,如图7所示,在分布er与分布a之间设定判定电压va的情况下,具有小于判定电压va的阈值电压的存储单元mt被判断为属于分布er。另外,在分布a与分布b之间设定判定电压vb的情况下,具有小于判定电压vb的阈值电压的存储单元mt被判断为属于分布er或分布a。同样地,如图7所示,在相邻的2个分布之间设定判定电压,具有小于该判定电压的阈值电压的存储单元mt被判断为属于2个分布中的阈值电压低的分布(或阈值电压比该分布低的分布)。

102.<存储器系统进行的处理>

103.接着,对存储器系统20a进行的处理进行说明。图8是表示存储器系统20a的处理流程的一例的图。

104.当存储器系统20a启动时,cpu2014从nand存储器202或rom2013读出固件,并加载到ram2012。然后,cpu2014执行固件所包括的第一程序pg1(步骤s1)。这里的启动包括:存储器系统20a的电源从断开状态切换到接通状态而存储器系统20a成为能够动作的状态,或者存储器系统20a被复位之后存储器系统20a成为能够动作的状态。cpu2014执行第一程序pg1,由此存储器系统20a成为从外部经由主机装置20b接受访问请求的状态。

105.主机装置20b在从外部收到访问请求时,向存储器系统20a输出该访问请求。cpu2014经由主机i/f控制器2011收到访问请求。

106.在cpu2014收到访问请求的情况下,取得部204a从人造卫星经由天线203接收电波(步骤s2)。

107.确定部204b基于取得部204a接收到的电波,确定存储器系统20a的位置(步骤s3)。签名部204c对确定部204b所确定的存储器系统20a的位置赋予规定的签名数据(步骤s4)。通过由签名部204c进行的该处理,以后,能够防止确定部204b所确定的存储器系统20a的位置的篡改。

108.第一判定部204d判定签名数据是否是签名部204c的签名数据(步骤s5)。第一判定部204d在判定为签名数据不是签名部204c的签名数据的情况下(在步骤s5中为否),使处理返回到步骤s2。另外,第一判定部204d在判定为签名数据是签名部204c的签名数据的情况下(步骤s5为是),判定确定部204b所确定的存储器系统20a的位置是否处于第一规定范围内(步骤s6)。第一判定部204d例如从存储器控制器201的ram2012读出与第一规定范围有关的信息。第一判定部204d将所读出的第一规定范围与确定部204b所确定的存储器系统20a的位置进行比较。

109.生成部204e基于确定部204b所确定的存储器系统20a的位置,生成对数据进行加密及解密时所使用的与加密及解密相关的信息。

110.具体而言,在第一判定部204d判定为存储器系统20a的位置处于第一规定范围外的情况下(在步骤s6中为否),生成部204e不生成与数据的加密及解密相关的信息,而使处理返回到步骤s2。

111.在第一判定部204d判定为存储器系统20a的位置处于第一规定范围内的情况下(在步骤s6中为是),生成部204e生成与数据的加密及解密相关的信息(步骤s7)。生成部204e生成的与数据的加密及解密相关的信息也可以根据存储器系统20a的位置而不同。

112.在生成部204e生成了与数据的加密及解密相关的信息的情况下,访问处理部204f使用生成部204e生成的与数据的加密及解密相关的信息,将cpu2014对向nand存储器202写入的数据进行加密的处理、或者cpu2014对从nand存储器202读出的数据进行解密的处理中的至少一个处理设为可能的状态(步骤s8)。

113.<优点>

114.以上,对第一实施方式的第一信息处理装置10进行了说明。在第一信息处理装置10中,生成部204e基于存储器系统20a所存在的位置来生成与数据的加密及解密相关的信息。访问处理部204f使用生成部204e生成的与数据的加密及解密相关的信息,将cpu2014对

向nand存储器202写入的数据进行加密的处理、或者cpu2014对从nand存储器202读出的数据进行解密的处理中的至少一个处理设为可能的状态。

115.通过这样构成存储器系统20a,由此限制能够访问nand存储器202所存储的数据的条件,在不满足该条件的情况下,不生成与数据的加密及解密相关的信息。其结果是,通过第一实施方式的第一信息处理装置10,能够降低存储器系统20a存储的数据向外部泄漏的可能性。即,通过第一实施方式的第一信息处理装置10,能够实现存储器系统20a中的数据的保密性的提高。

116.另外,生成部204e生成的与数据的加密及解密相关的信息也可以根据存储器系统20a的位置而不同。由此,在数据被写入时的存储器系统20a的位置与读出数据时的存储器系统20a的位置不同的情况下,无法正确地对数据进行解密。其结果,能够进一步提高存储器系统20a中的数据的保密性。

117.(第一实施方式的第一变形例)

118.在上述的第一实施方式中,说明了在存储器系统20a中,通信处理装置204作为取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、以及访问处理部204f发挥功能的情况。然而,在第一实施方式的第一变形例中,在存储器系统20a中,取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、以及访问处理部204f的一部分或者全部也可以设置于cpu2014或者nand控制器2016。例如,可以如图9所示,cpu2014具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e以及访问处理部204f全部。另外,例如也可以如图10所示,nand控制器2016具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、以及访问处理部204f全部。另外,例如还可以如图11所示,cpu2014具备取得部204a、确定部204b以及签名部204c,nand控制器2016具备第一判定部204d、生成部204e以及访问处理部204f。

119.(第一实施方式的第二变形例)

120.另外,在第一实施方式的第二变形例中,在存储器系统20a中,也可以将取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e以及访问处理部204f的一部分或者全部与通信处理装置204、cpu2014以及nand控制器2016分开地设置于存储器控制器201。例如可以如图12所示,存储器控制器201与通信处理装置204、cpu2014以及nand控制器2016分开地具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e以及访问处理部204f全部。此外,在图12中,省略了主机接口控制器2011、ram2012、rom2013以及ecc电路2015的记载。

121.(第二实施方式)

122.在第二实施方式的第一信息处理装置10中,在存储器系统20a启动时,基于存储器系统20a所存在的位置,判定是否执行固件fw1所包括的第一程序pg1。

123.<通信处理装置的结构>

124.图13是表示通信处理装置204的结构的一例的图。通信处理装置204作为取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、以及启动部204h发挥功能。

125.第二判定部204g基于存储器系统20a所存在的位置,判定是否执行第一程序pg1。

126.例如,第二判定部204g在第一判定部204d判定为存储器系统20a的位置处于第一

规定范围内的情况下,判定为执行第一程序pg1。另外,第二判定部204g在第一判定部204d判定为存储器系统20a的位置处于第一规定范围外的情况下,判定为不执行第一程序pg1。

127.启动部204h基于第二判定部204g的判定结果,使存储器控制器201的cpu2014执行第一程序pg1。

128.例如,在第二判定部204g判定为执行第一程序pg1的情况下,启动部204h使cpu2014执行第一程序pg1。另外,在第二判定部204g判定为不执行第一程序pg1的情况下,启动部204h不使cpu2014执行第一程序pg1。

129.<存储器系统进行的处理>

130.接着,对存储器系统20a进行的处理进行说明。图14是表示存储器系统20a的处理流程的一例的图。

131.存储器系统20a启动后,通信处理装置204的第二判定部204g基于存储器系统20a所存在的位置,判定是否执行第一程序pg1(步骤s11)。具体而言,第二判定部204g在第一判定部204d判定为存储器系统20a的位置处于第一规定范围内的情况下,判定为执行第一程序pg1。另外,第二判定部204g在第一判定部204d判定为存储器系统20a的位置处于第一规定范围外的情况下,判定为不执行第一程序pg1。

132.在第二判定部204g判定为执行第一程序pg1的情况下(步骤s11中为是),启动部204h使存储器控制器201的cpu2014从rom2013中读出固件(步骤s12)。然后,cpu2014执行固件所包括的第一程序pg1(步骤s13)。通过该步骤s13的处理,存储器系统20a成为从外部接受访问请求的状态。存储器系统20a能够执行图8所示的步骤s1以后的处理。

133.第二判定部204g在判定为不执行第一程序pg1的情况下(步骤s11中为否),结束处理。

134.<优点>

135.以上,对第二实施方式的第一信息处理装置10进行了说明。在第一信息处理装置10的存储器系统20a中,第二判定部204g基于存储器系统20a所存在的位置,判定是否执行第一程序pg1。启动部204h基于第二判定部204g的判定结果,使cpu2014执行第一程序pg1。

136.在第一实施方式的第一信息处理装置10中,无论存储器系统20a的位置如何,都能够从主机装置20b对存储器系统20a发行命令。例如,在存储器系统20a的位置不在第一规定范围内的情况下,无法进行加密后的数据的读出以及新数据的写入,但除此以外的来自主机装置20b的命令能够由存储器系统20a接受。另一方面,在第二实施方式的第一信息处理装置10中,能够实现根据存储器系统20a的位置,无法进行从主机装置20b向存储器系统20a的命令发行本身。例如,在存储器系统20a的位置不处于第一规定范围内的情况下,主机装置20b能够使存储器系统20a无法识别。其结果,第二实施方式的第一信息处理装置10与第一实施方式的第一信息处理装置10相比,能够进一步降低存储器系统20a所存储的数据向外部泄漏的可能性。即,第二实施方式的第一信息处理装置10与第一实施方式的第一信息处理装置10相比,能够进一步实现存储器系统20a中的数据的保密性的提高。

137.(第二实施方式的第一变形例)

138.在上述的第二实施方式中,说明了在存储器系统20a中,通信处理装置204作为取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、以及启动部204h发挥功能的情况。但是,在第二实施方式的第一变形例中,在

存储器系统20a中,取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、以及启动部204h的一部分或者全部也可以设置于cpu2014或者nand控制器2016。例如可以如图15所示,cpu2014具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g以及启动部204h。另外,例如也可以如图16所示,nand控制器2016具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、以及启动部204h。另外,例如还可以如图17所示,cpu2014具备取得部204a、确定部204b、签名部204c以及第一判定部204d,nand控制器2016具备生成部204e、访问处理部204f、第二判定部204g以及启动部204h。

139.(第二实施方式的第二变形例)

140.另外,在第二实施方式的第二变形例中,在存储器系统20a中,也可以将取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、以及启动部204h的一部分或者全部与通信处理装置204、cpu2014以及nand控制器2016分开地设置于存储器控制器201。例如可以如图18所示,存储器控制器201与通信处理装置204、cpu2014以及nand控制器2016分开地具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g以及启动部204h。此外,在图18中,省略了主机接口控制器2011、ram2012、rom2013以及ecc电路2015的记载。

141.(第三实施方式)

142.<信息处理系统的结构>

143.图19是表示根据第三实施方式的信息处理系统1的结构的一例的图。如图19所示,信息处理系统1具备第一信息处理装置10和第二信息处理装置20(外部装置的一例)。第一信息处理装置10能够经由网络nw与第二信息处理装置20连接。在第三实施方式的信息处理系统1中,在存储器系统20a从第二信息处理装置20收到访问请求的情况下,基于与该请求一起从第二信息处理装置20发送的第二信息处理装置20的位置数据,判定存储器系统20a是否生成与数据的加密及解密相关的信息。

144.<第二信息处理装置的结构>

145.图20是表示第三实施方式的第二信息处理装置20的结构的一例的图。第二信息处理装置20是用于访问由第一信息处理装置10存储的数据的装置。第二信息处理装置20例如是膝上式pc那样的移动式的信息处理终端。如图20所示,第二信息处理装置20具备通信部101、处理部102、第一取得部103、确定部104以及签名部105。通信部101、处理部102、第一取得部103、确定部104以及签名部105例如能够由1个或者多个cpu(central processing unit:中央处理单元)、fpga(field programmable gate array:现场可编程门阵列)、asic(application specific integrated circuit:专用集成电路)那样的集成电路构成。另外,第二信息处理装置20具备天线10a。

146.通信部101经由第一信息处理装置10所具备的主机装置20b而与存储器系统20a进行通信。

147.处理部102经由通信部101尝试向存储器系统20a写入数据的处理、或者从存储器系统20a读出数据的处理。

148.第一取得部103从人造卫星经由天线10a接收电波。

149.确定部104基于第一取得部103接收到的电波,确定第二信息处理装置20的位置。例如,确定部104与在第一实施方式中确定部204b使用gps确定了存储器系统20a的位置的方法同样地,确定第二信息处理装置20的位置。即,确定部104基于第一取得部103分别从4个不同的人造卫星接收到的电波,确定第二信息处理装置20的位置。另外,位置例如由纬度及经度表示。但是,位置可以是除了纬度及经度之外还由标高来表示的位置。

150.签名部105对与访问请求一起向第一信息处理装置10发送的第二信息处理装置20的位置数据赋予规定的签名数据。例如,签名部105基于rsa算法,使用私钥对位置数据赋予规定的签名数据。私钥保存在例如usb(universal serial bus:通用串行总线)加密狗等硬件安全模块设备中。并且,签名部105将赋予了签名数据的位置数据与访问请求一起发送至第一信息处理装置10。

151.<通信处理装置的结构>

152.图21是表示第一信息处理装置10所具备的通信处理装置204的结构的一例的图。通信处理装置204作为取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i以及第一验证部204j发挥功能。

153.第三判定部204i使用规定的公钥来判定签名数据是否是第二信息处理装置20的签名数据。规定的公钥与第二信息处理装置20在签名数据的赋予中所使用的私钥成对。即,规定的公钥是将签名数据解密为第三判定部204i能够读取的数据的公钥。

154.第一验证部204j在第三判定部204i判定为签名数据是第二信息处理装置20的签名数据的情况下,使存储器系统20a的处理继续。另外,在第三判定部204i判定为签名数据不是第二信息处理装置20的签名数据的情况下,第一验证部204j使存储器系统20a的处理结束。

155.在第三判定部204i判定为签名数据是第二信息处理装置20的签名数据的情况下,第一验证部204j验证第二信息处理装置20的位置是否处于第二规定范围内,该第二信息处理装置20的位置由从第二信息处理装置20收到的第二信息处理装置20的位置数据所表示。第二规定范围被设定为第二信息处理装置20能够访问存储器系统20a的第二信息处理装置20的位置。该第二规定范围例如在存储器系统20a的动作开始时从存储器芯片2021被加载到ram2012中。图22是表示第二规定范围的一例的图。在图22中,针对第二信息处理装置20能够访问存储器系统20a的纬度和经度,规定关于纬度的允许范围和关于经度的允许范围,由此示出第二规定范围。第一验证部204j读出与写入到ram2012的这样的第二规定范围有关的信息。第一验证部204j通过将读出的第二规定范围与从第二信息处理装置20收到的第二信息处理装置20的位置数据进行比较,由此能够验证第二信息处理装置20的位置是否处于第二规定范围内。

156.生成部204e在第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内的情况下,生成与数据的加密及解密相关的信息。

157.例如,主机装置20b在从第二信息处理装置20收到数据的写入请求时,向存储器系统20a输出该写入请求。在cpu2014经由主机i/f控制器2011收到写入请求,第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内的情况下,生成部204e基于存储器系统20a所存在的位置生成加密密钥。另外,在第一验证部204j验证为第二信息处理装置20

的位置不处于第二规定范围内的情况下,生成部204e不生成加密密钥。

158.另外,例如,主机装置20b在从第二信息处理装置20收到数据的读出请求时,向存储器系统20a输出该读出请求。在cpu2014经由主机i/f控制器2011收到读出请求,第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内的情况下,生成部204e基于存储器系统20a所存在的位置生成解密密钥。另外,在第一验证部204j验证为第二信息处理装置20的位置不处于第二规定范围内的情况下,生成部204e不生成解密密钥。

159.访问处理部204f在生成部204e生成了与数据的加密及解密相关的信息的情况下,使用生成部204e生成的与数据的加密及解密相关的信息,将cpu2014对向nand存储器202写入的数据进行加密的处理、或者cpu2014对从nand存储器202读出的数据进行解密的处理中的至少一个处理设为可能的状态。

160.例如,访问处理部204f在生成部204e生成了加密密钥的情况下,将生成部204e生成的加密密钥发送至存储器控制器201。存储器控制器201的cpu2014使用加密密钥对向nand存储器202写入的写入数据进行加密。然后,存储器控制器201的nand控制器2016将加密后的数据向nand存储器202写入。

161.另外,例如,访问处理部204f在生成部204e生成了解密密钥的情况下,将生成部204e生成的解密密钥发送至存储器控制器201。存储器控制器201的nand控制器2016从nand存储器202读出加密后的数据。然后,存储器控制器201的cpu2014使用生成部204e生成的解密密钥,对从nand存储器202读出的加密后的数据进行解密。

162.<存储器系统进行的处理>

163.接着,对存储器系统20a进行的处理进行说明。图23是表示存储器系统20a的处理流程的一例的图。

164.第二信息处理装置20将赋予了签名数据的位置数据与访问请求一起发送至主机装置20b。主机装置20b将赋予了签名数据的位置数据与访问请求一起发送至存储器系统20a。

165.通信处理装置204的第三判定部204i使用规定的公钥来判定签名数据是否是第二信息处理装置20的签名数据(步骤s21)。

166.第三判定部204i在判定为签名数据不是第二信息处理装置20的签名数据的情况下(在步骤s21中为否),结束处理。

167.另外,在第三判定部204i判定为签名数据是第二信息处理装置20的签名数据的情况下(在步骤s21为是),第一验证部204j验证由从第二信息处理装置20接收到的第二信息处理装置20的位置数据表示的第二信息处理装置20的位置是否处于第二规定范围内(步骤s22)。

168.具体而言,第一验证部204j读出与已写入到ram2012的第二规定范围有关的信息。然后,第一验证部204j将读出的第二规定范围与从第二信息处理装置20收到的第二信息处理装置20的位置数据进行比较。

169.第一验证部204j在验证了第二信息处理装置20的位置不处于第二规定范围内的情况下(在步骤s22中为否),结束处理。

170.在第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内的情况下(在步骤s22中为是),生成部204e生成与数据的加密及解密相关的信息(步骤s23)。

171.具体而言,在第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内的情况下,生成部204e基于存储器系统20a所存在的位置生成加密密钥。加密密钥是与数据的加密及解密相关的信息的一例。另外,在第一验证部204j验证为第一信息处理装置10的位置不处于第二规定范围内的情况下,生成部204e不生成加密密钥。

172.另外,具体而言,在第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内的情况下,生成部204e基于存储器系统20a所存在的位置生成解密密钥。解密密钥是与数据的加密及解密相关的信息的一例。另外,在第一验证部204j验证为第二信息处理装置20的位置不处于第二规定范围内的情况下,生成部204e不生成解密密钥。

173.访问处理部204f在生成部204e生成了与数据的加密及解密相关的信息的情况下,使用生成部204e所生成的与数据的加密及解密相关的信息,将cpu2014对向nand存储器202写入的数据进行加密的处理、或者cpu2014对从nand存储器202读出的数据进行解密的处理中的至少一个处理设为可能的状态(步骤s6)。

174.<优点>

175.以上,对第三实施方式的信息处理系统1进行了说明。在信息处理系统1的存储器系统20a中,在第三判定部204i判定为签名数据是第二信息处理装置20的签名数据的情况下,第一验证部204j验证从第二信息处理装置20接收到的第二信息处理装置20的位置数据所表示的第二信息处理装置20的位置是否处于第二规定范围内。

176.通过这样构成存储器系统20a,能够判定有无对从第二信息处理装置20向存储器系统20a发送的第二信息处理装置20的位置数据的篡改。因此,第三实施方式的信息处理系统1所具备的第一信息处理装置10与第一~第二实施方式的第一信息处理装置10相比,能够进一步限制能够向存储器系统20a所存储的数据进行访问的条件。在不满足该条件的情况下,不生成与数据的加密及解密相关的信息,无法访问存储器系统20a所存储的数据。其结果是,第三实施方式的第一信息处理装置10与第一~第二实施方式的第一信息处理装置10相比,能够进一步降低存储器系统20a存储的数据向外部泄漏的可能性。即,第三实施方式的第一信息处理装置10与第一~第二实施方式的第一信息处理装置10相比,能够进一步实现存储器系统20a中的数据的保密性的提高。

177.(第三实施方式的第一变形例)

178.在上述的第三实施方式中,说明了在存储器系统20a中,通信处理装置204作为取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i以及第一验证部204j发挥功能。然而,在第三实施方式的第一变形例中,在存储器系统20a中,取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i以及第一验证部204j的一部分或者全部也可以设置于cpu2014或者nand控制器2016。例如可以如图24所示,cpu2014具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i以及第一验证部204j的全部。另外,例如也可以如图25所示,nand控制器2016具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i以及第一验证部204j的全部。另外,例如还可以如图26所示,cpu2014具备取得部204a、确定部204b、签名部204c、第一判定部204d以及生成部204e,nand

控制器2016具备访问处理部204f、第二判定部204g、启动部204h、第三判定部204i以及第一验证部204j。

179.(第三实施方式的第二变形例)

180.另外,在第三实施方式的第二变形例中,在存储器系统20a中,也可以将取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i以及第一验证部204j的一部分或者全部与通信处理装置204、cpu2014以及nand控制器2016分开地设置于存储器控制器201。例如可以如图27所示,存储器控制器201与通信处理装置204、cpu2014以及nand控制器2016分开地具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i以及第一验证部204j的全部。另外,在图27中,省略了主机接口控制器2011、ram2012、rom2013和ecc电路2015的描述。

181.(第四实施方式)

182.在第四实施方式的信息处理系统1中,限制了从第二信息处理装置20能够向存储器系统20a访问的时间段,验证存储器系统20a是否为该时间段中的访问。

183.<信息处理系统的结构>

184.图28是表示根据第四实施方式的信息处理系统1的结构的一例的图。信息处理系统1具备第一信息处理装置10和第二信息处理装置20。如图28所示,信息处理系统1能够与服务器30连接。服务器30是发布时间戳的时间戳服务器。时间戳是指,在可信的时刻,对某数字信息赋予能够检测是否有变更、篡改的信息,在该时刻以后,能够证明该数字信息的内容是否有变更、篡改。

185.<第二信息处理装置的结构>

186.图29是表示第四实施方式的第二信息处理装置20的结构的一例的图。如图29所示,第二信息处理装置20具备通信部101、处理部102、第一取得部103、确定部104、签名部105以及第二取得部106。另外,第二信息处理装置20具备天线10a。

187.第二取得单元106从服务器30取得时间戳。

188.签名部105对与访问请求、第二信息处理装置20的位置数据一起向第一信息处理装置10发送的时间戳赋予规定的签名数据。然后,签名部105将赋予了签名数据的时间戳与访问请求、第二信息处理装置20的位置数据一起发送至第一信息处理装置10。

189.<通信处理装置的结构>

190.图30是表示通信处理装置204的结构的一例的图。通信处理装置204作为取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i、第一验证部204j及第二验证部204k发挥功能。

191.第二验证部204k验证由从第二信息处理装置20收到的时间戳表示的时刻是否在规定的时刻的范围内。时间戳是时间信息的一例。规定的时刻的范围被设定为第二信息处理装置20能够向存储器系统20a访问的时刻的范围。该规定的时刻的范围例如在存储器系统20a的动作开始时从存储器芯片2021被加载到ram2012。图31是表示规定的时刻的范围的一例的图。在图31中,根据第二信息处理装置20能够向存储器系统20a访问的开始时刻和结束时刻,示出了规定的时刻的范围。第二验证部204k读出被写入到ram2012的这样的规定的时刻的范围(即,能够访问的开始时刻和能够访问的结束时刻)。第二验证部204k通过将读

出的规定的时刻的范围与从第二信息处理装置20收到的时间戳表示的时刻进行比较,能够验证第二信息处理装置20的时间戳表示的时刻是否在规定的时刻的范围内。

192.生成部204e在第一验证部204j验证第二信息处理装置20的位置处于第二规定范围内,第二验证部204k验证为由时间戳表示的时刻在规定的时刻的范围内的情况下,生成与数据的加密及解密相关的信息。

193.例如,主机装置20b若从第二信息处理装置20收到数据的写入请求,则向存储器系统20a输出该写入请求。cpu2014经由主机i/f控制器2011接收写入请求。在cpu2014收到写入请求,第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内,第二验证部204k验证为时间戳在规定的时刻的范围内的情况下,生成部204e基于存储器系统20a所存在的位置来生成加密密钥。加密密钥是与数据的加密及解密相关的信息的一例。另外,在cpu2014收到写入请求,第一验证部204j验证为第二信息处理装置20的位置不处于第二规定范围内,或者第二验证部204k验证为时间戳不在规定的时刻的范围内的情况下,生成部204e不生成加密密钥。

194.另外,例如,主机装置20b若从第二信息处理装置20收到数据的读出请求,则向存储器系统20a输出该读出请求。cpu2014经由主机i/f控制器2011接收读出请求。在cpu2014收到读出请求,第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内,第二验证部204k验证为时间戳在规定的时刻的范围内的情况下,生成部204e基于存储器系统20a所存在的位置来生成解密密钥。解密密钥是与数据的加密及解密相关的信息的一例。另外,在cpu2014收到读出请求,第一验证部204j验证为第二信息处理装置20的位置不处于第二规定范围内,或者第二验证部204k验证为时间戳不在规定的时刻的范围内的情况下,生成部204e不生成解密密钥。

195.访问处理部204f在生成部204e生成了与数据的加密及解密相关的信息的情况下,使用生成部204e生成的与数据的加密及解密相关的信息,将cpu2014对向nand存储器202写入的数据进行加密的处理、或者cpu2014对从nand存储器202读出的数据进行解密的处理中的至少一个处理设为可能的状态。

196.例如,访问处理部204f在生成部204e生成了加密密钥的情况下,将生成部204e生成的加密密钥发送至存储器控制器201。存储器控制器201的cpu2014使用加密密钥对向nand存储器202写入的写入数据进行加密。然后,存储器控制器201的nand控制器2016将加密后的数据向nand存储器202写入。另外,访问处理部204f在生成部204e生成了解密密钥的情况下,将生成部204e生成的解密密钥发送至存储器控制器201。存储器控制器201的nand控制器2016从nand存储器202读出加密后的数据。然后,存储器控制器201的cpu2014使用生成部204e生成的解密密钥,对从nand存储器202读出的加密后的数据进行解密。

197.<存储器系统进行的处理>

198.接着,对存储器系统20a进行的处理进行说明。图32是表示存储器系统20a的处理流程的一例的图。

199.第二信息处理装置20将赋予了签名数据的时间戳与访问请求、位置数据一起发送至主机装置20b。主机装置20b将赋予了签名数据的时间戳与访问请求、位置数据一起发送至存储器系统20a。

200.通信处理装置204的第三判定部204i使用规定的公钥来判定签名数据是否是第二

信息处理装置20的签名数据(步骤s31)。

201.第三判定部204i判定为签名数据不是第二信息处理装置20的签名数据的情况下(在步骤s31中为否),结束处理。

202.另外,在第三判定部204i判定为签名数据是第二信息处理装置20的签名数据的情况下(在步骤s31为是),第一验证部204j验证由从第二信息处理装置20接收到的第二信息处理装置20的位置数据表示的第二信息处理装置20的位置是否处于第二规定范围内(步骤s32)。

203.具体而言,第一验证部204j读出与被写入到ram2012的第二规定范围有关的信息。然后,第一验证部204j将读出的第二规定范围与从第二信息处理装置20接收到的第二信息处理装置20的位置数据进行比较。

204.第一验证部204j在验证了第二信息处理装置20的位置不处于第二规定范围内的情况下(在步骤s32中为否),结束处理。

205.在第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内的情况下(在步骤s32为是),第二验证部204k验证从第二信息处理装置20收到的时间戳是否在规定的时刻的范围内(步骤s33)。

206.具体而言,第二验证部204k读出与被写入到ram2012的规定的时刻的范围有关的信息。第二验证部204k将读出的规定的时刻的范围与从第二信息处理装置20收到的时间戳表示的时刻进行比较。第二验证部204k验证时间戳表示的时刻是否在规定的时刻的范围内。

207.第二验证部204k验证为时间戳不在规定的时刻的范围内的情况下(在步骤s33中为否),结束处理。

208.在第二验证部204k验证为时间戳在规定的时刻的范围内的情况下(在步骤s33中为是),生成部204e生成与数据的加密及解密相关的信息(步骤s23)。

209.具体而言,主机装置20b若从第二信息处理装置20收到数据的写入请求,则向存储器系统20a输出该写入请求。cpu2014经由主机i/f控制器2011接收写入请求。在cpu2014收到写入请求,第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内,第二验证部204k验证为从第二信息处理装置20收到的时间戳在规定的时刻的范围内的情况下,生成部204e基于存储器系统20a所存在的位置来生成加密密钥。加密密钥是与数据的加密及解密有关的信息的一例。另外,在cpu2014收到写入请求、第一验证部204j验证为第二信息处理装置20的位置不处于第二规定范围内,或者第二验证部204k验证为从第二信息处理装置20收到的时间戳不在规定的时刻的范围内的情况下,生成部204e不生成加密密钥。

210.另外,具体而言,主机装置20b若从第二信息处理装置20收到数据的读出请求,则向存储器系统20a输出该读出请求。cpu2014经由主机i/f控制器2011接收读出请求。在cpu2014收到读出请求,第一验证部204j验证为第二信息处理装置20的位置处于第二规定范围内,第二验证部204k验证为从第二信息处理装置20收到的时间戳为规定的时刻的范围内的情况下,生成部204e根据存储器系统20a所存在的位置生成解密密钥。解密密钥是与数据的加密及解密有关的信息的一例。另外,在cpu2014收到读出请求、第一验证部204j验证为第二信息处理装置20的位置不处于第二规定范围内,或者第二验证部204k验证为从第二信息处理装置20收到的时间戳不在规定的时刻的范围内的情况下,生成部204e不生成解密

密钥。

211.访问处理部204f在生成部204e生成了与数据的加密及解密相关的信息的情况下,使用生成部204e生成的与数据的加密及解密相关的信息,将cpu2014对向nand存储器202写入的数据进行加密的处理、或者cpu2014对从nand存储器202读出的数据进行解密的处理中的至少一个处理设为可能的状态(步骤s6)。

212.<优点>

213.以上,对第四实施方式的信息处理系统1进行了说明。在信息处理系统1的存储器系统20a中,第二验证部204k验证从第二信息处理装置20收到的时间戳是否在规定的时刻的范围内。

214.通过这样构成存储器系统20a,在第二验证部204k验证为从第二信息处理装置20收到的时间戳不在规定的时刻的范围内的情况下,生成部204e不生成与数据的加密及解密相关的信息。因此,第四实施方式的第一信息处理装置10,与第一~第三实施方式的第一信息处理装置10相比,能够进一步限制能够向存储器系统20a所存储的数据进行访问的条件。其结果是,第四实施方式的第一信息处理装置10与第一~第三实施方式的第一信息处理装置10相比,能够进一步降低存储器系统20a存储的数据向外部泄漏的可能性。即,第四实施方式的第一信息处理装置10与第一~第三实施方式的第一信息处理装置10相比,能够进一步实现存储器系统20a中的数据的保密性的提高。

215.(第四实施方式的第一变形例)

216.在上述的第四实施方式中,说明了在存储器系统20a中,通信处理装置204作为取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i、第一验证部204j以及第二验证部204k发挥功能。然而,在第四实施方式的第一变形例中,在存储器系统20a中,取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i、第一验证部204j以及第二验证部204k的一部分或者全部也可以设置于cpu2014或者nand控制器2016。例如可以如图33所示,cpu2014具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i、第一验证部204j以及第二验证部204k的全部。另外,例如也可以如图34所示,nand控制器2016具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i、第一验证部204j以及第二验证部204k的全部。另外,例如还可以如图35所示,cpu2014具备取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e以及访问处理部204f,nand控制器2016具备第二判定部204g、启动部204h、第三判定部204i、第一验证部204j以及第二验证部204k。

217.(第四实施方式的第二变形例)

218.另外,在第四实施方式的第二变形例中,也可以将取得部204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i、第一验证部204j以及第二验证部204k的一部分或者全部与通信处理装置204、cpu2014以及nand控制器2016分开地设置于存储器控制器201。例如可以如图36所示,存储器控制器201与通信处理装置204、cpu2014以及nand控制器2016分开地具备取得部

204a、确定部204b、签名部204c、第一判定部204d、生成部204e、访问处理部204f、第二判定部204g、启动部204h、第三判定部204i、第一验证部204j以及第二验证部204k的全部。另外,在图36中,省略了主机接口控制器2011、ram2012、rom2013和ecc电路2015的描述。

219.在上述的实施方式以及变形例中,将加密密钥和解密密钥作为不同的密钥进行了说明,但在其他的实施方式中,加密密钥和解密密钥也可以是相同的密钥。

220.以上,对几个实施方式及变形例进行了说明,但实施方式并不限定于上述例子。上述的实施方式以及变形例也可以相互组合来实现。存储器控制器201的功能的一部分或全部也可以通过asic(application specific integrated circuit:专用集成电路)、pld(programmable logic device:可编程逻辑器件)或fpga(field programmable gate array:现场可编程门阵列)等硬件(包括电路部:circuitry)来实现。另外,本说明书中的“第一”、“第二”等序数是为了便于说明,也可以调换顺序而重新进行。

221.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子而提示的,并不意图限定发明的范围。这些实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包括在发明的范围或主旨中,同样包括在权利要求书所记载的发明及其等同的范围内。

222.附图标记说明

[0223]1…

信息处理系统,10

…

第一信息处理装置,10a

…

天线,20

…

第二信息处理装置,20a

…

存储器系统,20b

…

主机装置,30

…

服务器,101

…

通信部,102

…

处理部,103

…

第一取得部,104

…

确定部,105

…

签名部,106

…

第二取得部,201

…

存储器控制器,202

…

nand存储器,203

…

天线,204a

…

取得部,204b

…

确定部,204c

…

签名部,204d

…

第一判定部,204e

…

生成部,204f

…

访问处理部,204g

…

第二判定部,204h

…

启动部,204i

…

第三判定部,204j

…

第一验证部,204k

…

第二验证部,2011

…

主机i/f控制器,2012

…

ram,2012a

…

判定电压信息,2012b

…

基准电压信息,2013

…

rom,2014

…

cpu,2015

…

ecc电路,2016

…

nand控制器,2021

…

存储器芯片,2021a

…

i/o信号处理电路,2021b

…

控制信号处理电路,2021c

…

芯片控制电路,2021d

…

ry/by生成电路,2021e

…

命令寄存器,2021f

…

地址寄存器,2021g

…

行解码器,2021h

…

列解码器,2021i

…

数据寄存器,2020j

…

读出放大器,2021k

…

存储单元阵列,blk

…

物理区块,mt

…

存储单元,wl

…

字线。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。