1.本发明有关于一种具有存储器内运算(in-memory-computing(imc))的存储器装置及其操作方法。

背景技术:

2.人工智能(ai)已在许多领域中成为高度有效解决方案。ai的关键操作在于对大量的输入数据(如输入特征图(input feature maps))与权重值进行乘积累加运算(multiply-and-accumulation(mac))。

3.然而,以目然的ai架构而言,容易遇到输出入瓶颈(io bottleneck)与低效率的mac运算流程(inefficient mac operation fow)。

4.为达到高准确度,可执行具有多位输入及多位权重值的mac操作。然而,输出入瓶颈变得更加严重,且效率将更低。

5.存储器内运算in-memory-computing(imc))可用于加速mac运算,因为imc可减少在中央处理架构下所需要用的复杂算术逻辑单元(arithmetic logic unit,alu),且提供存储器内的mac操作的高并行性(parallelism)。

6.以非易失性存储器式imc(nvm-based imc)而言,其优点例如是,非易失性储存,数据迁移减少等。然而,非易失性存储器式imc的挑战在于,最高位(most significantbit,msb)的错误位效应(error-bit effect),不易分辨的电流加总结果(indistinguishable current summation results),需要大量adc/dac故而增加功率消耗及芯片面积。

7.公开内容

8.根据本发明一实例,提出一种存储器装置,包括:一存储器阵列,包括多个存储器单元,可用于储存多个权重值于该存储器阵列的这些存储器单元内;一乘法电路,耦接至该存储器阵列,该乘法电路对多个输入数据与这些权重值进行乘法,以得到多个乘法结果;以及一计数单元,耦接至该乘法电路,对这些乘法结果进行位计数以得到一乘积累加运算(mac)运算结果。

9.根据本发明另一实例,提出一种存储器装置的操作方法,包括:储存多个权重值于该存储器装置的一存储器阵列的多个存储器单元内;对多个输入数据与这些权重值进行位乘法,以得到多个乘法结果;以及对这些乘法结果进行位计数以得到一乘积累加运算(mac)运算结果。

10.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附图式详细说明如下:

附图说明

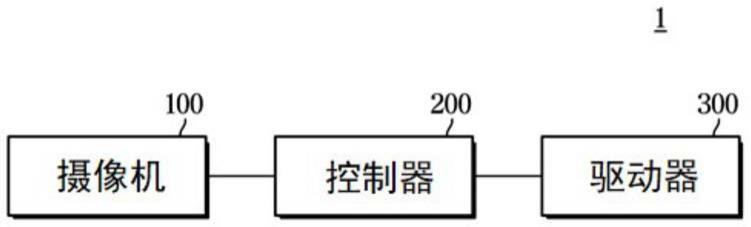

11.图1绘示根据本发明一实施例的具有存储器内运算功能的存储器装置的功能框图。

12.图2显示根据本发明一实施例的数据映射(data mapping)示意图。

13.图3a至图3c显示根据本发明一实施例的数据映射的数个例。

14.图4a与图4b显示本发明实施例的乘法运算的两种示范例示意图。

15.图5a与图5b显示根据本发明一实施例的分群操作(多数决操作)与计数示意图。

16.图6显示比较本发明一实施例与常规技术的mac运算流程。

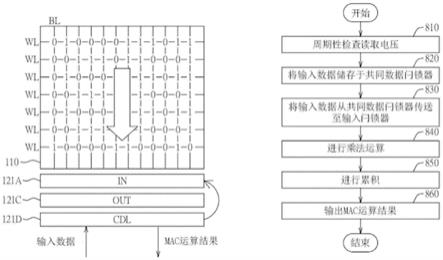

17.图7a显示本发明实施例中的编程固定存储器页面(memory page)的流程图,图7b显示本发明实施例中的调整读取电压的流程图。

18.图8显示根据本发明一实施例的mac操作流程。

19.附图标记说明

20.100:存储器装置

21.110:存储器阵列

22.120:乘法电路

23.130:输出入电路

24.140:分群电路

25.150:计数单元

26.111:存储器单元

27.121:单位元乘法单元

28.121a:输入闩锁器

29.121b:感应放大器

30.121c:输出闩锁器

31.121d:共同数据闩锁器

32.141:分群单元

33.301a、303a、301b、303b、311a、313a、311b、313b:位

34.302、312、314:权重值

35.405、415:闩锁器

36.410:位线开关

37.420:与门

38.710-750:步骤

39.810-860:步骤

具体实施方式

40.本说明书的技术用语参照本技术领域的习惯用语,如本说明书对部分用语有加以说明或定义,该部分用语的解释以本说明书的说明或定义为准。本发明的各个实施例分别具有一或多个技术特征。在可能实施的前提下,本领域技术人员可选择性地实施任一实施例中部分或全部的技术特征,或者选择性地将这些实施例中部分或全部的技术特征加以组合。

41.请参照图1,其绘示根据本发明一实施例的具有存储器内运算(in-memory-computing(imc))功能的存储器装置100的功能框图。具有存储器内运算功能的存储器装置100包括:存储器阵列110、乘法电路120、输出入电路130、分群电路140与计数单元150。其中,存储器阵列110与乘法电路120是模拟的,而分群电路140与计数单元150是数字的。

42.存储器阵列110包括多个存储器单元111。在本发明一实施例中,存储器单元111例如但不受限于,为非易失性存储器单元。当进行mac操作时,存储器单元111可用于储存权重值(weight)。

43.乘法电路120耦接至存储器阵列110。乘法电路120包括多个单位元乘法单元121。各单位元乘法单元121包括:输入闩锁器121a、感应放大器(sa)121b、输出闩锁器121c与共同数据闩锁器(common data latch(cdl))121d。输入闩锁器121a耦接至存储器阵列110。感应放大器121b耦接至输入闩锁器121a。输出闩锁器121c耦接至感应放大器121b。共同数据闩锁器121d耦接至输出闩锁器121c。

44.输出入电路130耦接至乘法电路120、分群电路140与计数单元150,用以接收输入数据,并将存储器装置100所得到的输出数据输出。

45.分群电路140耦接至乘法电路120。分群电路140包括多个分群单元141。这些分群单元141对于这些单位元乘法单元121的多个乘法结果进行分群操作,以得到多个分群结果。在本发明一可能实施例中,分群操作例如可由多数决技术(majority technique)所实施,例如多数决功能技术(majority function technique),分群电路140由根据多数决功能技术的多数决群体电路(majority grouping circuit)所实施,分群单元141由分布式多数决群体单元(majority grouping unit)所实施,但本发明并不受限于此。分群技术可由其他相似技术来实施。在本发明一实施例中,分群电路140可选择性地设置。

46.计数单元150耦接至分群电路140或乘法电路120。在本发明一实施例中,计数单元150用以对乘法电路120的乘法结果进行位计数(bitwise counting)或位累积(bitwise accumulation),以产生mac操作结果(当存储器装置100不包括分群电路140时)。或者是,计数单元150用以对分群电路140的分群结果(例如,多数决结果)进行位计数或位累积,以产生mac操作结果(当存储器装置100包括分群电路140时)。在本发明一实施例中,计数单元150可以用已知的计数电路,例如但不限于,波纹计数器(ripple counter)来实现。在本发明说明中,计数与累积基本上具有相同意思,而计数器与累积器基本上具有相同意思。

47.现请参照图2,其显示根据本发明一实施例的数据映射(data mapping)示意图。如图2所示,以各输入数据(或各权重值)具有n个维度(n是正整数)的8位为例(但当知本发明并不受限于此)。

48.下面以输入数据的数据映射为例做说明,但当知本发明并不受限于此。下面的说明同样适用于权重值的数据映射。

49.当将输入数据以二进制8位表示时,输入数据(或权重值)分为最高有效位(most signifcant bit,msb)向量(vector)与最低有效位(least signifcant bit,lsb)向量。8位输入数据(或权重值)的最高有效位向量包括4位b7~b4,而最低有效位向量包括4位b3~b0。

50.将输入数据的msb向量与lsb向量的各位以一元编码(unary coding)(亦即数值形式(value format))表示。例如,输入数据的最高有效位向量的位b7可以表示为b70~b77,输入数据的最高有效位向量的位b6可以表示为b60~b63,输入数据的最高有效位向量的位b5可以表示为b50~b51,输入数据的最高有效位向量的位b4一样表示为b4。

51.将以一元编码(数值形式)表示的输入数据的msb向量的各位与输入数据的lsb向量的各位重复多次以成为点积展开式(unfolding dot product,unfdp)。例如,输入数据的

msb的各位被重复(2

4-1)次,同样地,输入数据的lsb的各位被重复(2

4-1)次。如此可以将输入数据以点积展开式表示。

52.对输入数据(点积展开式)与权重值进行乘法操作,以得到乘法操作结果。

53.为方便了解,下面以一例做说明,但当知其并非用于限制本发明。

54.现请参照图3a,其显示根据本发明一实施例的一维数据映射的一例。如图3a所示,输入数据=(in1,in2)=(2,1),与权重值=(we1,we2)=(1,2)。将输入数据的msb与lsb以二进制形式表示,所以,in1=10,而in2=01,相似地,将权重值的msb与lsb的各位以二进制形式表示,所以,we1=01,而we2=10。

55.将输入数据的msb与lsb,以及,权重值的msb与lsb,编码为以一元编码(数值形式)表示。亦即,将输入数据的msb编码为110,将输入数据的lsb编码为001,相似地,将权重值的msb编码为001,将权重值的lsb编码为110。

56.之后,将以编码为一元编码的输入数据的msb(110)的各位与编码为一元编码的输入数据的lsb(001)的各位重复多次以成为点积展开式(unfolding dot product,unfdp)。例如,输入数据的msb(110)的各位被重复3次,所以得到输入数据的msb的点积展开式为111111000。输入数据的lsb(001)的各位被重复3次,所以得到输入数据的lsb的点积展开式为000000111。

57.对输入数据(点积展开式)与权重值进行mac操作,以得到mac操作结果。mac操作结果为:1*0=0、1*0=0、1*1=1、1*0=0、1*0=0、1*1=1、0*0=0、0*0=0、0*1=0、0*1=0、0*1=0、0*0=0、0*1=0、0*1=0、0*0=0、1*1=1、1*1=1、1*0=0。将这些数值相加,则可以得到:0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 1 1 0=4。

58.由上述可知,如果输入数据是i位而权重值是j位(i与j皆为正整数),则所用的存储器单元数量为:(2

i-1)*(2

j-1)。

59.现请参照图3b,其显示根据本发明一实施例的数据映射的另一可能例。在图3b中,输入数据是(in1)=(2),而权重值是(we1)=(1)。输入数据与权重值是4位。

60.输入数据表示为二进制格式时,in1=0010。相似地,权重值表示为二进制格式时,we1=0001。

61.将输入数据与权重值编码成一元编码(数值形式)。例如,输入数据的最高位“0”编码成“00000000”,而输入数据的最低位“0”编码成“0”,以此类推。相似地,权重值的最高位“0”编码成“00000000”,而权重值的最低位“1”编码成“1”。

62.编码成一元编码的输入数据的各位被复制多次以成为点积展开式。例如,编码成一元编码的输入数据的最高位301a被复制15次以成为位303a;以及,编码成一元编码的输入数据的最低位301b被复制15次以成为位303b。

63.编码成一元编码的权重值302也被复制15次,以表示为点积展开式。

64.对表示为乘积展开式的输入数据与表示为点积展开式的权重值进行乘法操作以产生mac操作结果。详细而言,输入数据的位303a乘上权重值302;输入数据的元303b乘上权重值302,依此类推。将乘法值加总可以产生mac操作结果(“2”)。

65.现请参照图3c,其显示根据本发明一实施例的数据映射的另一可能例。在图3c中,输入数据是(in1)=(1),而权重值是(we1)=(5)。输入数据与权重值是4位。

66.输入数据表示为二进制格式时,in1=0001。相似地,权重值表示为二进制格式时,

we1=0101。

67.将输入数据与权重值编码成一元编码(数值形式)。

68.编码成一元编码的输入数据的各位被复制多次以成为点积展开式。在图3c中,当复制输入数据的各位与权重值的各位时,加入位“0”。例如,编码成一元编码的输入数据的最高位311a被复制15次并加入位“0”以成为位313a;以及,编码成一元编码的输入数据的最低位311b被复制15次并加入位“0”以成为位313b。藉此将输入数据表示为点积展开式。

69.相似地,编码成一元编码的权重值312也被复制15次,并额外加入位“0”至各权重值314。藉此将权重值表示为点积展开式。

70.对表示为点积展开式的输入数据与表示为点积展开式的权重值进行乘法操作以产生mac操作结果。详细而言,输入数据的位313a乘上权重值314;输入数据的位313b乘上权重值314,依此类推。将乘法值加总可以产生mac操作结果(“5”)。

71.在常规技术中,对8位输入数据与8位权重值进行mac操作,如果采用直接mac运算法,则所用的存储器单元数量为255*255*512=33,292,822。

72.相反地,如上述般,在本发明实施例中,对8位输入数据与8位权重值进行mac操作,则所用的存储器单元数量为15*15*512*2=115,200*2=230,400。故而,本发明实施例在进行mac操作中所用的存储器单元数量约为常规技术的0.7%。

73.在本发明实施例中,利用unfdp式的数据映射,可以减少运算时所用的存储器单元数量,故而可以减少运算成本,且减少错误校正码(ecc,error correction code)成本。另外,也可以容忍错误位效应(fail-bit effect)。

74.请再参考图1。在本发明实施例中,当进行乘法运算时,权重值(转导值)乃是储存于存储器阵列110的这些存储器单元111内,而输入数据(电压)则是由输出入电路130读取并传送给共同数据闩锁器121d。共同数据闩锁器121d传送输入数据给输入闩锁器121a。

75.为更了解本发明实施例的乘法运算,现请参考图4a与图4b,其显示本发明实施例的乘法运算的两种示范例示意图。图4a应用于存储器装置支持受选位线读取(the selected bit-line read function),图4b应用于存储器装置不支持受选位线读取。图4a中,输入闩锁器121a包括闩锁器(第一闩锁器)405与位线开关410;以及,图4b中,输入闩锁器121a包括闩锁器(第二闩锁器)415与与门420。

76.如图4a所示,将权重值以一元编码(数值形式)表示(如图2)。故而,权重值的最高位存于8个存储器单元111内,权重值的次高位存于4个存储器单元111内,权重值的第三高位存于2个存储器单元111内,权重值的最低位存于1个存储器单元111内。

77.同样地,将输入数据以一元编码(数值形式)表示(如图2),故而,输入数据的最高位存于8个共同数据闩锁器121d内,输入数据的次高位存于4个共同数据闩锁器121d内,输入数据的第三高位存于2个共同数据闩锁器121d内,输入数据的最低位存于1个共同数据闩锁器121d内。输入数据从共同数据闩锁器121d送至闩锁器405。

78.在图4a中,这些多个位线开关410耦接于存储器单元111与感应放大器121b之间。位线开关410受控于闩锁器405。例如,当闩锁器405输出位1时,位线开关410为导通,而当闩锁器405输出位0时,位线开关410为关闭。

79.此外,当存储器单元111内的权重值为位1且位线开关410为导通(输入数据为位1)时,感应放大器121b将感应到存储器单元电流以产生乘法结果“1”。当存储器单元111内的

权重值为位0且位线开关410为导通(输入数据为位1)时,感应放大器121b感应不到存储器单元电流。当存储器单元111内的权重值为位1且位线开关410为关闭(输入数据为位0)时,感应放大器121b感应不到存储器单元电流以产生乘法结果“0”。当存储器单元111内的权重值为位0且位线开关410为关闭(输入数据为位0)时,感应放大器121b感应不到存储器单元电流。

80.亦即,经由图4a的布局方式,当输入数据为位1且权重值为位1时,感应放大器121b感应到存储器单元电流以产生乘法结果“1”。至于其他情况,感应放大器121b感应不到存储器单元电流,以产生乘法结果“0”。

81.在图4b,输入数据从共同数据闩锁器121d送至闩锁器415。与门420的一端接受感应放大器121b的感应结果(即权重值),而另一端则接收闩锁器415的输出位(亦即输入数据)。当存储器单元111所储存的权重值为位1时,感应放大器121b的感应结果为逻辑高(感应到存储器单元电流);当存储器单元111所储存的权重值为位0时,感应放大器121b的感应结果为逻辑低(感应不到存储器单元电流)。

82.当闩锁器415输出位1(亦即输入数据为位1)且感应放大器121b的感应结果为逻辑高(亦即权重值为位1)时,与门420输出位1以产生乘法结果“1”,并送至分群电路140或计数单元150。至于其他情况下,与门420输出位0以产生乘法结果“0”,并送至分群电路140或计数单元150。

83.图4b的实施例不只可应用于非易失性存储器,也可应用于易失性存储器。

84.在本发明实施例中,当进行乘法运算时,可以重复使用受选位线读取(selected bit line read,sbl-read)指令。故而,本发明实施例可以减少以单位元表示(single-bit representation)所来的变动影响(variation infuence)。

85.现请参考图5a,其显示根据本发明一实施例的分群操作(多数决操作)与位计数(bitwise counting)示意图。如图5a所示,参考符号gm1代表对输入数据的第一msb向量与权重值进行位乘法(bitwise multiplication)后所得到的第一乘法运算结果;参考符号gm2代表对输入数据的第二msb向量与权重值进行位乘法后所得到的第二乘法运算结果;参考符号gm3代表对输入数据的第三msb向量与权重值进行位乘法后所得到的第三乘法运算结果;参考符号gl代表对输入数据的lsb与权重值进行位乘法后所得到的第四乘法运算结果。在分群操作(多数决操作)后,对第一乘法运算结果gm1进行分群结果是第一分群结果cb1(其累积权重是22);对第二乘法运算结果gm2进行分群结果是第二分群结果cb2(其累积权重是22);对第三乘法运算结果gm3进行分群结果是第三分群结果cb3(其累积权重是22);以及,对第四乘法运算结果gl进行分群结果是第四分群结果cb4(其累积权重是20)。

86.图5b显示图3c的累积例。请参照图3c与图5b。如图5b所示,输入数据(图3c)的位313b乘上权重值314。从输入数据(图3c)的位313b乘上权重值314所产生的乘法结果的前四个位(“0000”)被分群为第一乘法结果“gm1”。相似地,从输入数据(图3c)的位313b乘上权重值314所产生的乘法结果的第五至第八位(“0000”)被分群为第二乘法结果“gm2”。从输入数据(图3c)的位313b乘上权重值314所产生的乘法结果的第九至第十二位(“1111”)被分群为第三乘法结果“gm3”。从输入数据(图3c)的位313b乘上权重值314所产生的乘法结果的第十三至第十六位(“0010”)则被直接计数。

87.在分群操作(多数决操作)后,第一分群结果cb1是“0”(其累积权重是22);第二分

群结果cb2是“0”(其累积权重是22);第三分群结果cb3是“1”(其累积权重是22)。在计数时,将这些分群结果cb1~cb4乘上个别累积权重并加以累积而产生mac操作结果。例如,如图5b所示,mac操作结果是cb1*22 cb2*22 cb3*22 cb4*20=0*22 0*22 1*22 1*20=00000000000000000000000000000101=5。

88.在本发明一实施例中,分群原则(多数决原则)可如下所示:

89.群组位分群结果(多数决结果)1111(状况a)11110(状况b)11100(状况c)1或01000(状况d)00000(状况e)0

90.在上表中,以状况a而言,由于群组皆为正确的(“1111”没有错误位),故而,其多数决结果为1。以状况e而言,由于群组皆为正确的(“0000”没有错误位),故而,其多数决结果为0。

91.以状况b而言,由于群组中有1个位是错误(“1110”中的“0”是错误的),通过多数决,可以将“1110”决定为“1”。以状况d而言,由于群组中有1个位是错误(“0001”中的“1”是错误的),通过多数决,可以将“0001”决定为“0”。

92.以状况c而言,群组中有2个位是错误的(“1100”中的“00”是错误的,或者,“1100”中的“11”是错误的),通过多数决,可以将“1100”决定为“1”或“0”。

93.故而,在本发明实施例中,通过分群(多数决)功能,可以减少错误位。

94.分群电路140的分群结果系输入至计数单元150进行位计数。

95.在进行计数时,将msb向量的乘法运算结果的计数结果与lsb向量的乘法运算结果的计数结果进行累积。以图5a的情况而言,使用两种累积器。第一种累积器要被分配较高的累积权重值(例如是22)。第一种累积器要累积:(1)“对乘法运算结果gm1进行分群(多数决)的所得到分群(多数决)结果:1位”加上“对乘法运算结果gm2进行分群(多数决)的分群(多数决)结果:1位”再加上“对乘法运算结果gm3进行分群(多数决)的分群(多数决)结果:1位”。第一种累积器所得到的计数结果再乘以较高的累积权重值(例如是22)。第二种累积器要被分配较低的累积权重值(例如是20)。第二种累积器则是对乘法运算结果gl(多位)进行直接计数。将经累积权重加权过的两种累积结果相加,即可得到mac结果。例如,对乘法运算结果gm1进行分群的所得到分群结果为1(1位),对乘法运算结果gm2进行分群的分群结果为0(1位),对乘法运算结果gm3进行分群的分群结果为1(1位)。第一种累积器所得到的计数结果(1 0 1)再乘以22,等于2*22=8。对乘法运算结果gl为4(3位),可直接计数。将经累积权重加权过的两种累积结果相加,即可得到mac结果为8 4=12。

96.由上述可知,在本发明实施例中,当进行计数或累积(accumulation)时,由于输入数据已展开为unfdp形式,可以对储存在共同数据闩锁器内的数据进行分群(亦即,分为msb向量与lsb向量),通过分群机制(多数决机制)可以减少在msb向量/lsb向量内的错误位。

97.此外,在本发明实施例中,即便使用传统的累积器(计数器),仍可以减少计数/累积时间,这是因为本发明实施例乃是使用数字计数指令(错误位计数),以及对于不同向量(msb向量与lsb向量)的累积结果给予不同累积权重。以一例而言,可以将累积运算时间减

少至约40%。

98.图6显示比较本发明一实施例与常规技术的mc运算流程。以本发明实施例与常规技术的mac运算流程而言,输入数据传输至存储器装置。同时进行位线设定与字线设定。当位线设定完成后,进行感应。进行累积操作。并将累积操作结果回传。重复上述操作,直到所有输入数据都运算完成。

99.由图6可知,本发明实施例的mac操作可以分为两种子操作类型。第一种子操作类型是乘法操作,将输入数据乘上权重值,乃是根据受选位线读取指令而进行。第二种子操作类型则是累积(数据计数),特别是错误位计数(fail bit counting)。在本发明其他可能实施例中,可以加入更多计数单元,以加速计数/累积操作。

100.相较于常规技术,在本发明实施例中,进行累积操作的速度较快,故而可以加快mac操作。

101.此外,在本发明实施例中,亦可调整读取电压。图7a显示本发明实施例中的编程固定存储器页面(memory page)的流程图,图7b显示本发明实施例中的调整读取电压的流程图。

102.在图7a中,在步骤710中,将一笔已知输入数据编程至一固定存储器页面内,其中,该笔已知输入数据的位比率是:50%是位0,50%是位1。

103.在图7b中,步骤720中,读取该固定存储器页面,并计数位1的比率。步骤730中,判断位1的比率是否接近50%。如果步骤730为否,则流程接至步骤740。如果步骤730为是,则流程接至步骤750。

104.步骤740中,如果位1的比率小于50%,则增加读取电压;以及,如果位1的比率大于50%,则减少读取电压。步骤740结束后,流程回至步骤720。

105.步骤750中,记录目前的读取电压,以作为后续读取操作所用。

106.如所知般,读取电压将会影响到位1的读取。故而,在本发明实施例中,可以根据操作条件(例如但不受限于,编程周期,温度或读取干扰等),周期性地校正读取电压,以保持高正确性与可靠度。

107.图8显示根据本发明一实施例的mac操作流程。如图8所示,在步骤810中,周期性检查读取电压。如果读取电压需要调整的话,则可如图7b的流程来调整。

108.在步骤820中,将输入数据储存于共同数据闩锁器121d。

109.在步骤830中,将输入数据从共同数据闩锁器121d传送至输入闩锁器121a。

110.在步骤840中,在支持受选位线读取指令或不支持受选位线读取指令下,进行乘法运算。

111.在步骤850中,进行累积。

112.在步骤860中,将mac运算结果输出(例如通过输出入电路30输出)。

113.本发明实施例可应用于nand型闪存,或者敏感于保持与热变化的存储器装置,例如但不受限于,nor型闪存,相变(pcm)型闪存,磁式随机存取存储器(magnetic ram)或电阻式ram。

114.本发明实施例可应用于3d型存储器与2d型存储器,例如但不受限于,2d/3d nand型闪存,2d/3d nor型闪存,2d/3d相变(pcm)型闪存,2d/3d磁式随机存取存储器(magnetic ram)或2d/3d电阻式ra。

115.虽然上述实施例中,将输入数据及/或权重值分为msb向量与lsb向量(2个向量),但本发明并不受限于此。在本发明其他可能实施例中,输入数据及/或权重值亦可分为更多个向量,此亦在本发明保护范围内。

116.本发明实施例不仅可应用多数决分群技术,也可应用其他分群技术,以加速累积。

117.本发明实施例可应用于,例如但不受限于,人脸识别等ai技术之中。

118.综上所述,虽然本发明已以实施例公开如上,然其并非用以限定本发明。本发明所属技术领域中技术人员,在不脱离本发明的精神和范围内,可作各种更动与润饰。因此,本发明的保护范围应以随附的权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。