1.本发明属于集成电路设计和数据传输技术领域,具体涉及一种多芯片模块中芯片间的超短距离数据传输方法及装置。

背景技术:

2.高速的数据传输是高性能计算机、数据中心、5g和智能驾驶等应用的关键技术之一,其带宽、功耗和延迟指标是cpu、gpu、dps、ai和交换等高端芯片发展的瓶颈。

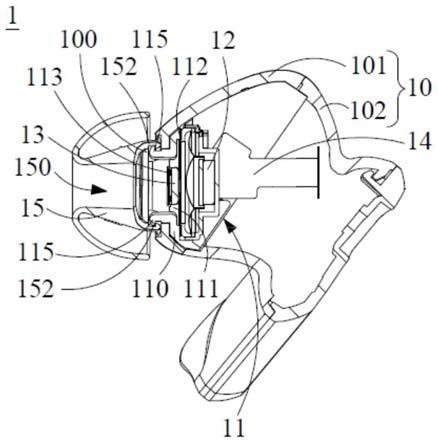

3.图1给出了一种典型的多模块(mcm)芯片互连方式,它将不同功能的芯粒集成到同一基板上,避免了大尺寸芯片设计时光照尺寸受限、良率低、设计周期长和成本高的问题,进而提升高端芯片的整体性能。

4.当前典型的数据传输有串行、并行两大分类,图2给出两大分类中不同类型的发展趋势。单端二进制脉冲幅度调制(pam2-ses)具有非常好的引脚效率(pepam2,ses=1,每条线传输一位数据:1bit/1wire),但是这种信号传输方法对共模噪声(cmn)和信号串扰(xtalk)表现出了高灵敏度,并同时产生开关噪声(ssn)。采用差分传输方式(1bit/2wire)可以很好的解决共模噪声的问题,但其较低的引脚效率会降低链路的吞吐量。为了进一步提高吞吐率,业界已经转向使用更高阶的pam,例如pam4和pam8。pam4已成功用于56gb/s和112gb/s链路的设计。但pam4和pam8对码间干扰的敏感度更高,尤其是在反射形式下,对信号串扰具有更高的灵敏度,因为小的过渡会受到大过渡的干扰(对于反射也是如此)。

技术实现要素:

5.本发明要解决的技术问题:针对现有技术的上述问题,提供一种多芯片模块中芯片间的超短距离数据传输方法及装置。本发明提供了一种基于相关不归零(cnrz)信令传输方案(称为弦信令)的usr(超短距离)链路,该链路通过n 1根导线传输n位(nb/n 1w),从而为mcm应用启用了非常高速且非常节能的芯片到芯片链路。弦信令与pam2-ds具有相同的灵敏度,并提供了较高的引脚效率。与pam4和pam8相比,弦信令对均衡复杂度要求更低,传输时的功耗更低。在不损失信道串扰,共模噪声,同步开关噪声和码间干扰等指标的同时,无需使用模数转换器(adc),最终实现较高的引脚效率。

6.为了解决上述技术问题,本发明采用的技术方案为:

7.一种多芯片模块中芯片间的超短距离数据传输方法,包括在发送端和接收端之间通过多路差分信号传输cnrz-n编码的弦信令,其中cnrz-n编码中的n是指cnrz-n编码中数据位宽,且发送端对弦信令的编码为将cnrz-n编码矩阵、发送端和接收端之间的共模电压vcm以及n位数据d0~dn构成的矩阵相乘得到编码后得到的n 1位的弦信令;接收端对弦信令的解码为将n 1位的弦信令、cnrz-n编码矩阵的倒置矩阵相乘还原出发送端发送的n位数据d0~dn。

8.可选地,所述发送端和接收端之间的共模电压vcm的大小满足:

[0009][0010]

上式中,wi为编码后得到的第i位数据。

[0011]

可选地,所述cnrz-n编码是指cnrz-7编码,发送端对弦信令编码的函数表达式为:

[0012][0013]

上式中,cnrz7为cnrz-7编码矩阵,vcm为发送端输出端的共模电压,d0~d6为待编码的7位数据,w0~w7为编码后得到的8位数据。

[0014]

可选地,接收端对弦信令解码的函数表达式为:

[0015][0016]

上式中,vcm为发送端和接收端之间的共模电压,d0~d6为解码后得到的7位数据,cnrz

7t

为cnrz-7编码矩阵的倒置矩阵。

[0017]

可选地,cnrz-7编码矩阵cnrz7的函数表达式为:

[0018][0019]

可选地,所述发送端侧编码为将cnrz-n编码矩阵、发送端输出端的共模电压vcm以及n位数据d0~dn构成的矩阵相乘得到编码后得到的n 1位的弦信令时,发送端为cnrz-n编码矩阵的每一列使用一个编码器,每一行作为一个子信道对应接收端的一个解码器。

[0020]

可选地,所述发送端侧编码为将cnrz-n编码矩阵、发送端输出端的共模电压vcm以及n位数据d0~dn构成的矩阵相乘得到编码后得到的n 1位的弦信令时,发送端在每个预设的单位间隔ui中采用电压模式的驱动方式,在驱动编码器的同时也对n位数据d0~dn进行了编码并发送出去。

[0021]

可选地,所述接收端侧将n 1位的弦信令、cnrz-n编码矩阵的倒置矩阵相乘还原出发送端发送的n位数据d0~dn时,n 1根导线连接到n个多输入比较器电路,每个比较器电路的输入级都执行逆线性变换以实现线性组合,产生n个等眼的二进制数据。

[0022]

此外,本实施例还提供一种多芯片模块中芯片间的超短距离数据传输装置,包括发射机、接收机以及位于发射机、接收机的编解码传输模块,所述编解码传输模块由编码器、解码器以及位于编码器、解码器之间的多条传输线路构成,所述编解码传输模块被编程或配置以执行所述的多芯片模块中芯片间的超短距离数据传输方法的步骤。

[0023]

此外,本实施例还提供一种多核计算设备,包括相互连接多核处理器和存储器,其特征在于,所述多核处理器被编程或配置以执行所述的多芯片模块中芯片间的超短距离数据传输方法的步骤。

[0024]

和现有技术相比,本发明具有下述优点:本发明提供了一种基于相关不归零(cnrz)信令传输方案(称为弦信令)的usr(超短距离)链路,该链路通过n 1根导线传输n位(nb/n 1w),从而为mcm应用启用了非常高速且非常节能的芯片到芯片链路。弦信令与pam2-ds具有相同的灵敏度,并提供了较高的引脚效率。与pam4和pam8相比,弦信令对均衡复杂度要求更低,传输时的功耗更低,无需使用模数转换器(adc),最终实现较高的引脚效率。

附图说明

[0025]

图1为现有典型的多模块(mcm)芯片互连方式。

[0026]

图2为现有串行、并行两大分类的数据传输方式的发展趋势图。

[0027]

图3为本发明实施例方法的基本流程示意图。

[0028]

图4为本发明实施例中n=1(cnrz-1)的最简单的编码传输原理图。

[0029]

图5为本发明实施例中n=7(cnrz-7)的编码传输原理图。

[0030]

图6为本发明实施例中sst编码逻辑示例。

[0031]

图7为本发明实施例中多输入比较器示例。

[0032]

图8为本发明实施例中7位数据的d0~d6输出眼图仿真结果图。

具体实施方式

[0033]

如图3所示,本实施例提供一种多芯片模块中芯片间的超短距离数据传输方法,包括在发送端和接收端之间通过多路差分信号传输cnrz-n编码的弦信令,其中cnrz-n编码中的n是指cnrz-n编码中数据位宽,且发送端对弦信令的编码为将cnrz-n编码矩阵、发送端和接收端之间的共模电压vcm以及n位数据d0~dn构成的矩阵相乘得到编码后得到的n 1位的弦信令;接收端对弦信令的解码为将n 1位的弦信令、cnrz-n编码矩阵的倒置矩阵相乘还原出发送端发送的n位数据d0~dn。为了解决由于差分传输(ds)引起的引脚效率低的问题,本实施例采用了具有编码特点的cnrz-n信令传输方法,达到了在保持差分传输中信道串扰,共模噪声,同步开关噪声和码间干扰等指标的情况下,提高了链路的引脚效率。

[0034]

cnrz-n本质上是差分信号(ds)的一种推广,是弦信令的一种传输方式之一。本实施例中,采用cnrz-n编码的弦信令的主要属性如下:

[0035]

1)nb/(n 1)w,即:n 1个信道传输n位数据。

[0036]

2)发送端和接收端之间的共模电压vcm的大小满足:

[0037][0038]

上式中,wi为编码后得到的第i位数据。通过引入发送端和接收端之间的共模电压vcm,保持差分传输的优点。

[0039]

3)基于弦信令的链路的输入和输出总是二进制。尽管每条线上的信号电平数目可以超过2,甚至更多。在接收端解码后产生的二进制信号,节省了高分辨率adc的需求,利用简单的slicer电路后便可通信。

[0040]

其中,cnrz-n编码中的n可根据需要选择取值。

[0041]

图4所示为n=1(cnrz-1)的最简单的链路拓扑和相应的数学模型,为弦信令的最简单的编码形式,用于将1位数据进行编码,实现1b/2w传输。以其最简单的形式,考虑一个pam2-ds链接。为了将单端位转换为差分值,在编码时执行以下转换:

[0042][0043]

上式中,d为n=1(cnrz-1)的待传输的1位二进制数据。此外,编码器和解码器的总增益使用因子进行归一化。单端到差分的变换是基于walsh

–

hadamard(沃尔什-阿达玛)矩阵h进行的,其中h-1

=h

t

=h。此属性意味着可以在接收器端使用编码矩阵的转换矩阵来解码,恢复出原始二进制数据,即:

[0044][0045]

对于常用的差分信令传输,常采用电压模式或电流模式驱动器用于发射机发送数据,而接收器前端可采用差分放大器提取二进制数据。

[0046]

为了实现更有效的弦信令方案,使用了更高阶的编码与解码矩阵。图5为本实施例中n=7(cnrz-7)的链路拓扑和相应的数学模型,采用了同样的正交多线信令,最终完成7b/8w传输,引脚效率提高了175%。对应的cnrz-7链路在8条线上并行传输7位数据。此时,cnrz-n编码是指cnrz-7编码,发送端对弦信令编码的函数表达式为:

[0047][0048]

上式中,cnrz7为cnrz-7编码矩阵,vcm为发送端输出端的共模电压,d0~d6为待编码的7位数据,w0~w7为编码后得到的8位数据。对应地,接收端对弦信令解码的函数表达式为:

[0049][0050]

上式中,vcm为发送端和接收端之间的共模电压,d0~d6为解码后得到的7位数据,cnrz

7t

为cnrz-7编码矩阵的倒置矩阵。n=7(cnrz-7)的链路拓扑和相应的数学模型中,cnrz-7编码矩阵cnrz7的函数表达式为:

[0051][0052]

本实施例中,所述发送端侧编码为将cnrz-n编码矩阵、发送端输出端的共模电压vcm以及n位数据d0~dn构成的矩阵相乘得到编码后得到的n 1位的弦信令时,发送端为cnrz-n编码矩阵的每一列使用一个编码器(电压模驱动:w0~w7),每一行作为一个子信道对应接收端的一个解码器。

[0053]

如图6所示,本实施例中发送端侧编码为将cnrz-n编码矩阵、发送端输出端的共模电压vcm以及n位数据d0~dn构成的矩阵相乘得到编码后得到的n 1位的弦信令时,发送端在每个预设的单位间隔ui中采用电压模式的驱动方式,在驱动编码器的同时也对n位数据d0~dn进行了编码并发送出去,图6为将7bit数据(d0~d6)编码到8线(w0~w7)上。对应于每根导线(cnrz-7矩阵的每一列),将选择正确的输入位,加权后用于输出驱动器。组合后的信号将以目标输出阻抗放置在相应的导线上。本实施例中,接收端侧将n 1位的弦信令、cnrz-n编码矩阵的倒置矩阵相乘还原出发送端发送的n位数据d0~dn时,n 1根导线连接到n个多输入比较器电路,每个比较器电路的输入级都执行逆线性变换以实现线性组合,产生n个等眼的二进制数据。图7所示为八根导线连接到七个多输入比较器电路,每个比较器的输入级都执行逆线性变换以实现线性组合,产生七个等眼二进制数据。图7所示的示例实现了cnrz-7矩阵的第一行(子通道号0),其函数表达式为:

[0054]vout,0

=[w0 w1 w2 w

3-w

4-w

5-w

6-w7]

×gm

rd,

ꢀꢀ

(7)

[0055]

上式中,v

out,0

为输出数据d0的差分信号,wi代表信道i上的信号,rd是负载电阻,gm是图7中差分对的每个晶体管的跨导。尽管导线上有多个电平,但是每个多输入比较器电路的输出都是二进制的。因此,通过切片电路便可进行通信。尽管cnrz-7将引脚效率从双端差分的1/2提高到cnrz-7的7/8,但它不显现出对码间干扰过高的灵敏度,而且保持了对共模噪声和信号串扰的良好抗扰性能。本实施例中,该信令所基于的线性和正交变换在发射机中编码并驱动(见图6),在接收机的多输入比较器(mic)中进行解码(见图7),能够降低对串

扰和其他噪声源的敏感度,用时又要保持较高的数据速率和引脚效率。

[0056]

通常认为,具有更多级别的信令方法对isi表现出更高的敏感性。isi灵敏度与限幅器或决策电路输入端的信号电平数量直接相关,与传输线上的电平数量相反。考虑具有由h(t)表示的脉冲响应的信道。如果ci是从具有nc符号集中选择的数据符号:

[0057]ci

∈c={cj:j=0,

…

,n

c-1},

ꢀꢀ

(8)

[0058]

上式中,nc为nc符号集的数据符号总数量。

[0059]

那么,通过理想的多输入比较器电路后,所发送的信号可以描述为:

[0060][0061]

上式中,s(t)为发送的信号,ci是从具有nc符号集中选择的数据符号,pu(t)表示宽度为t的矩形脉冲,t为施加,t为符号持续时间(对应于一个单位间隔ui)。

[0062]

因此,接收到的信号将是发送信号与传输函数离散卷积的结果:

[0063][0064]ht,i(t)

的定义为:

[0065][0066]

上式中,r(t)为接收的信号,h(t)为传输函数,h

t,i(t)

为衰落项。

[0067]

假设接收到的信号t∈[0,t),则有:

[0068][0069]

上式中,c0是从具有nc符号集中选择的第一个数据符号,h

t,0(t)

为主衰落项,而第二个因素是与码间干扰相关的衰落系数,即:

[0070][0071]

其中,h

t,i(t)

/h

t,0(t)

是由于信道isi引起的衰落因子,而ci/c0是由于弦信令方法引起的码间干扰灵敏度。而编码方式的码间干扰比率定义为:

[0072][0073]

上式中,ir为编码方式的码间干扰比率(简称:干扰率),c',c为任意数据。则在码间干扰最差的情况下,ci/c0等于干扰率ir,因此有:

[0074][0075]

重要的是要注意,除了信道损耗,即h

t,i(t)

/h

t,0(t)

以外,还有第二个因素加剧了对码间干扰的敏感性:如前文定义的编码方式的干扰率ir。如果所有数据符号到接收端的距离相等,则ir=1,并且对码间干扰不会有额外的灵敏度。单端和差分pam2信令方法均满足ir=1。但是,在pam4信令中,ir=3(请参阅表1),这说明了为什么该信令方法对码间干扰表现出更高的灵敏度,因此需要更复杂的均衡。

[0076]

表1:不同信令方法的主要特性。

[0077][0078][0079]

此处的分析表明,信令方法的选择直接影响链路预算,精心设计的信令方案有助于避免不必要的睁眼损失。与和弦信令一样,传递给限幅器的信号是二进制的,ir=1,类似于pam2信令。因此,它不会表现出任何过高的isi灵敏度。本实施例中,可使用(15)计算眼睛的宽度。在时间间隔[0,t]中有两个时间点,其中r(t)=0。如果我们将这两个时间点称为t

l

(眼睛的左侧)和tr(眼睛的右侧),则眼睛宽度为:

[0080]

t

eye,width

=t

r-t

l

,

ꢀꢀ

(16)

[0081]

上式中,t

eye,width

表示眼睛宽度(眼宽)。

[0082]

从(15)和(16)可以明显看出,当ir》1时,眼宽减小得更快。可以进行相同的分析,以表明眼高也与ir成正比降低,表1比较了几种主要信令方法的isi灵敏度和引脚效率。本实施例中对前述方法进行电路仿真,输入为prbs7伪随机码,加入信道提取的参数(信道衰减约为7.5db),经过均衡后,7位高速数据的d0~d6输出眼图仿真结果分别如图8所示,图8中(a)为d0,(b)为d1,(c)为d2,(d)为d3,(e)为d4,(f)为d5,(g)为d6。由图8可知,解码后的信号完全是二进制的nrz信号。

[0083]

此外,本实施例还提供一种多芯片模块中芯片间的超短距离数据传输装置,包括发射机、接收机以及位于发射机、接收机的编解码传输模块,所述编解码传输模块由编码器、解码器以及位于编码器、解码器之间的多条传输线路构成,所述编解码传输模块被编程或配置以执行前述的多芯片模块中芯片间的超短距离数据传输方法的步骤。

[0084]

此外,本实施例还提供一种多核计算设备,包括相互连接多核处理器和存储器,所述多核处理器被编程或配置以执行前述的多芯片模块中芯片间的超短距离数据传输方法的步骤。

[0085]

本领域内的技术人员应明白,本技术的实施例可提供为方法、系统、或计算机程序产品。因此,本技术可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本技术可采用在一个或多个其中包含有计算机可用程序代码的计算机可读存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。本技术是参照根据本技术实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0086]

以上所述仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。