一种基于arm和fpga的调制解调板卡

技术领域

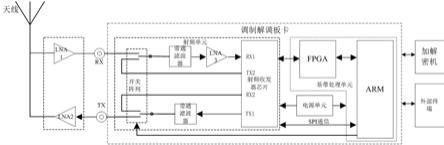

1.本实用新型涉及飞控通信技术领域,具体涉及一种基于arm和fpga的调制解调板卡。

背景技术:

2.在飞控技术领域中,为了获取飞行器运行数据并存储分析,给飞行器下发工况指令,一般通过便携式地面站与飞行器端设备之间进行数据交互及控制来完成。数据交互及控制过程中,便携式地面站内安装的基于arm和fpga的调制解调板卡则用于对下行信号进行射频接收、射频解调和基带解调;同时产生上行信号,并进行射频调制与发送。

3.现有的基于arm和fpga的调制解调板卡,常采用dsp fpga芯片组合作为处理器来完成射频信号的解调与调制,但是在与飞行器通信过程中,其实时控制能力较低,并不能通过外部终端对处理器进行实时监测和实时控制,例如参数的调整、事件回放、数据发送和停止等。

技术实现要素:

4.为了克服现有技术的不足,本实用新型提供了一种基于arm和fpga的调制解调板卡,不仅能够对射频信号进行解调和调制,还能通过外部终端对处理器进行实时监测和实时控制,实现射频信号收发、信号解调与调制等过程中的实时控制以及参数调整。

5.本实用新型的技术方案如下:

6.一种基于arm和fpga的调制解调板卡,包括有射频单元、通过ldvs接口与射频单元通信连接的基带处理单元以及电源单元,板卡侧边还设置有与基带处理单元通信连接的信号接收端口rx以及信号发送端口tx。

7.射频单元包括有依次连接的开关阵列、带通滤波器、第三信号放大器以及射频收发器芯片,射频收发器芯片,用于对经过带通滤波以及信号放大的射频信号进行模数转换以及收发的内部逻辑处理。

8.基带处理单元包括有fpga处理芯片以及arm处理芯片,fpga处理芯片,与射频收发器芯片通过ldvs总线数据连接,用于信号编码、复用、调制和解调的内部逻辑处理;arm处理芯片,通过数据总线与fpga处理芯片连接,用于对信号的内部逻辑处理进行控制,还通过spi总线与射频收发器芯片通信连接,用于对信号的接收与发送进行控制;其中,fpga处理芯片是整个基带处理的核心,主要负责获取射频单元采集到的射频信号并进行信号解调,并将解调后的数据发送给arm处理芯片,同时接收arm处理芯片的控制信号和需要发送的数据,将需要发送的数据进行信号调制并发送至射频收发芯片。

9.对接收到的信号进行跟踪,调制解调等处理;arm处理芯片作为协从处理单元通过与fpga处理芯片的数据交换完成部分信号处理功能,处理过的数据通过pcie总线上传到便携式终端设备,同时实现对其它外围器件进行控制。

10.进一步地,基于arm和fpga的调制解调板卡外还设置有第一信号放大器、第二信号

放大器和天线,开关阵列依次通过信号接收端口rx、第一信号放大器与天线连接,还通过信号发送端口tx、第二信号放大器与天线连接;其中,天线主要将接收到的无线射频信号放大,并转化为有线射频电信号;同时将发送的有线射频电信号放大,并转化为无线射频信号。

11.进一步地,开关阵列中设置有信号接收开关和信号发送开关,信号接收开关的开关端依次通过带通滤波器、第三信号放大器后与射频收发器芯片的第一接收端连接,天线、第一信号放大器、信号接收开关、带通滤波器、第三信号放大器以及射频收发器芯片组成信号接收链路。

12.射频收发器芯片的第一发送端通过带通滤波器与信号发送开关的开关端连接,天线、第二信号放大器、信号发送开关、带通滤波器、射频收发器芯片组成信号发送链路;

13.射频收发器芯片的第二发送端以及第二接收端均与开关阵列通信连接。

14.进一步地,基于arm和fpga的调制解调板卡还通过pcie总线连接有终端设备和加解密机;该终端设备,用于通过arm处理芯片和射频收发器芯片进行射频信号参数配置以及射频信号收发控制;还用于通过arm处理芯片和fpga处理芯片进行基带信号的参数配置以及控制基带信号的收发、调制与解调;同时,通过终端设备,还能实时监测、显示、存储、转发及事后回放与查阅,以及手动触发发送和停止上行数据发送;加解密机,用于对上行射频信号或下行射频信号进行加密或解密。

15.本实用新型通过射频单元对下行信号进行模数转换等内部逻辑处理之后,通过ldvs接口发送给基带处理单元进行信号的的编码、复用、解调等内部逻辑的处理,经处理过的数据通过pcie总线上传到终端设备;同时,基带处理单元将需要发送的数据进行信号调制后发送至射频单元,由射频单元进行数模转换等内部逻辑处理为上行信号并通过天线向外发送。因此,通过arm与fpga芯片的处理器组合,本实用新型不仅能够对射频信号进行解调和调制,还能通过外部终端对处理器进行实时监测和实时控制,实现射频信号收发、信号解调与调制等过程中的实时控制以及参数调整。

16.本实用新型所述的基于arm和fpga的调制解调板卡,具有兼容多种频段的信号解调、体积小、结构简单、易于设计实现等优点,以及数据传输速度快、抗干扰性等高可靠性性能。

附图说明

17.构成本技术的一部分的附图用来提供对本实用新型的进一步理解,本实用新型的示意性实施例及其说明用于解释本实用新型,并不构成对本实用新型的不当限定。在附图中:

18.图1是本实用新型实施例所述的基于arm和fpga的调制解调板卡的结构示意图。

具体实施方式

19.以下结合附图对本实用新型的实施例进行详细说明,但是本实用新型可以由权利要求限定和覆盖的多种不同方式实施。

20.如附图1所示,一种基于arm和fpga的调制解调板卡,包括有射频单元、通过ldvs接口与射频单元通信连接的基带处理单元以及电源单元,板卡侧边还设置有与基带处理单元

通信连接的信号接收端口rx以及信号发送端口tx,射频单元包括有依次连接的开关阵列、带通滤波器、第三信号放大器lna3以及射频收发器芯片,射频收发器芯片,用于对经过带通滤波以及信号放大的射频信号进行模数转换以及收发的内部逻辑处理。

21.开关阵列中设置有信号接收开关和信号发送开关,信号接收开关的开关端依次通过带通滤波器、第三信号放大器lna3后与射频收发器芯片的第一接收端连接,天线、第一信号放大器lna1、信号接收开关、带通滤波器、第三信号放大器lna3以及射频收发器芯片组成信号接收链路。

22.射频收发器芯片的第一发送端通过带通滤波器与信号发送开关的开关端连接,天线、第二信号放大器lna2、信号发送开关、带通滤波器、射频收发器芯片组成信号发送链路;射频收发器芯片的第二发送端以及第二接收端均与开关阵列通信连接。

23.基带处理单元包括有fpga处理芯片以及arm处理芯片,fpga处理芯片与射频收发器芯片通过ldvs总线数据连接,用于信号编码、复用、调制和解调的内部逻辑处理;arm处理芯片,通过数据总线与fpga处理芯片连接,用于与fpga处理芯片进行数据交换,还通过spi总线与射频收发器芯片通信连接,用于对信号的接收与发送进行控制。

24.基于arm和fpga的调制解调板卡外还设置有第一信号放大器lna1、第二信号放大器lna2和天线,开关阵列依次通过信号接收端口rx、第一信号放大器lna1与天线连接,还通过信号发送端口tx、第二信号放大器lna2与天线连接。

25.基于arm和fpga的调制解调板卡还通过pcie总线连接有终端设备和加解密机;该终端设备,用于通过arm处理芯片和射频收发器芯片进行射频信号参数配置以及射频信号收发控制;还用于通过arm处理芯片和fpga处理芯片进行基带信号的参数配置以及控制基带信号的收发、调制与解调;加解密机,用于对上行射频信号或下行射频信号进行加密或解密。

26.本实施例通过射频单元对s波段下行射频信号进行模数转换等内部逻辑处理之后,通过ldvs接口发送给基带处理单元进行信号的的编码、复用、解调等内部逻辑的处理,经处理过的数据通过pcie总线上传到终端设备;同时,基带处理单元将需要发送的数据进行信号调制后发送至射频单元,由射频单元进行数模转换等内部逻辑处理为l波段上行射频信号并通过天线向外发送。

27.本实施例通过arm处理芯片与外部终端通信连接,实现了处理器参数配置,射频信号和基带信号的收发控制、调制与解调的控制以及进行实时数据监测。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。