一种可支持8k输入输出的视频处理器

技术领域

1.本实用新型涉及音视频处理技术领域,具体涉及一种可支持8k输入输出的视频处理器。

背景技术:

2.视频处理器是led全彩显示屏诞生、成长以及成熟的全程见证者和标志性设备,led专用的视频处理设备在此过程中也逐渐走向成熟,led视频处理器的优劣直接影响了led显示屏的显示效果。

3.经过4k信号的发展,8k信号和显示设备已经开始出现,但是市面上除了少量的电脑显卡及高端电视机等,在led和投影等行业,还没有一款能够同时支持2k、4k及8k输入和输出的视频处理器。

4.有鉴于此,本实用新型的设计人设计出了本实用新型。

技术实现要素:

5.本实用新型的目的在于提供一种可支持8k输入输出的视频处理器,具有可同时支持2k、4k及8k输入和输出的特点。

6.为实现上述目的,本实用新型的技术解决方案是:

7.一种可支持2k、4k及8k输入输出的视频处理器,包括:至少一可供2k、4k和/或8k输入信号输入并可对2k、4k和/或8k输入信号进行区分处理的输入模块、一可将输入信号从至少一输入模块切换到至少一输出模块输出的总矩阵模块及至少一可供2k、4k和/或8k输入信号输出并可对2k、4k和/或8k输入信号进行区分处理的输出模块,所述总矩阵模块与输入模块及输出模块电性连接。

8.所述输入模块包括至少一可供2k、4k和/或8k输入信号输入的接口芯片、一输入fpga模块、一输入同步时钟模块及至少一差分输出模块,所述输入同步时钟模块与输入fpga模块电性连接,所述输入fpga模块包括一可分别对8k输入信号及2k和/或4k输入信号进行处理的输入接口解码模块,所述接口芯片电性连接输入fpga模块的输入接口解码模块,所述差分输出模块与总矩阵模块电性连接,所述输入接口解码模块电性连接至差分输出模块。

9.所述输入fpga模块还包括一音频视频处理模块,所述音频视频处理模块电性连接于所述输入接口解码模块与差分输出模块之间。

10.所述输入接口解码模块包括一可判断并分出8k输入信号及2k和/或4k输入信号的输入矩阵模块、一8k输入信号输入处理模块、一2k和/或4k输入信号输入处理模块、一输入逻辑模块、一输入hdcp解码模块,所述输入矩阵模块电性连接接口芯片,所述输入逻辑模块电性连接输入hdcp解码模块;所述8k输入信号输入处理模块包括依次串联电性连接的一16b/18b解码模块、一frl扰频器、一frl映射器、一rs fec解码模块及一frl打包模块;所述2k和/或4k输入信号输入处理模块包括依次串联电性连接的一tmds解码模块及一tmds扰频

器;所述输入矩阵模块的2k和/或4k输入信号输出口电性连接tmds解码模块,所述输入矩阵模块的8k输入信号输出口电性连接16b/18b解码模块,所述tmds扰频器及frl打包模块电性连接输入逻辑模块,所述输入逻辑模块的视频接口电性连接至音频视频处理模块。

11.所述8k输入信号输入处理模块还包括一偏差校验器,所述偏差校验器电性连接16b/18b解码模块。

12.所述输出模块包括一输出fpga模块、一输出同步时钟模块及至少一输出接口,所述输出同步时钟模块与输出fpga模块电性连接,所述输出fpga模块包括一可分别对8k输入信号及2k和/或4k输入信号进行处理的输出接口编码模块,所述输出接口编码模块电性连接总矩阵模块。

13.所述输出接口编码模块包括一可判断并分出8k输入信号及2k和/或4k输入信号的输出逻辑模块、一8k输入信号输出处理模块、一2k和/或4k输入信号输出处理模块及一可将并行信号转为串行信号的输出矩阵模块,所述输出矩阵模块电性连接至一驱动芯片,所述输出逻辑模块电性连接输出音频视频处理模块;所述8k输入信号输出处理模块包括依次串联电性连接的一frl打包模块、一frl超级块映射模块、一rs fec编码器、一frl扰频器及一16b/18b编码模块,所述8k输入信号输出处理模块的frl打包模块电性连接输出逻辑模块的8k输入信号输出口,所述8k输入信号输出处理模块的16b/18b编码模块电性连接输出矩阵模块;所述2k和/或4k输入信号输出处理模块包括依次串联电性连接的一tmds扰频器及一tmds编码模块,所述2k和/或4k输入信号输出处理模块的tmds扰频器电性连接输出逻辑模块的2k和/或4k输入信号输出口,所述2k和/或4k输入信号输出处理模块的tmds编码模块电性连接输出矩阵模块。

14.所述输出接口编码模块还包括一视频时钟控制模块及一hdcp模块,所述hdcp模块电性连接输出逻辑模块,所述总矩阵模块的音频接口电性连接输出逻辑模块,所述总矩阵模块的视频接口电性连接输出逻辑模块,所述视频时钟控制模块电性连接总矩阵模块的视频接口。

15.一种可支持2k、4k及8k输入输出的视频处理器,还包括一控制板及一扩展cxp模块,所述控制板电性连接总矩阵模块,所述扩展cxp模块电性连接总矩阵模块。

16.所述扩展cxp模块包括一fpga模块及一同步时钟模块,所述扩展cxp模块的同步时钟模块电性连接扩展cxp模块的fpga模块,所述扩展cxp模块的fpga模块电性连接总矩阵模块。

17.采用上述技术方案后,本实用新型通过输入模块及输出模块的结构设计,由于所述输入模块可以接受2k、4k和/或8k输入信号输入,且能够区分出2k、4k和/或8k输入信号,并对2k、4k和/或8k输入信号进行区分处理,所述输出模块也可以区分出2k、4k和/或8k输入信号,并对2k、4k和/或8k输入信号进行区分处理,输出2k、4k和/或8k输入信号,从而实现本实用新型可以同时支持2k、4k及8k输入和输出。

附图说明

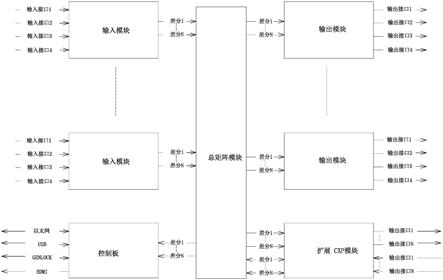

18.图1为本实用新型的原理示意图;

19.图2为本实用新型的输入模块的原理示意图;

20.图3为本实用新型的输入模块的输入接口解码模块的原理示意图;

21.图4为本实用新型的输出模块的原理示意图;

22.图5为本实用新型的输出模块的输出接口编码模块的原理示意图;

23.图6为本实用新型的cxp扩展板的原理示意图。

具体实施方式

24.为达成上述目的及功效,本实用新型所采用的技术手段及构造,兹绘图就本实用新型较佳实施例详加说明其特征与功能如下,以利完全了解。

25.请参阅图1所示,本实用新型揭示了一种可支持8k输入输出的视频处理器,包括:至少一可供2k、4k和/或8k输入信号输入并可对2k、4k和/或8k输入信号进行区分处理的输入模块、一可将输入信号从至少一输入模块切换到至少一输出模块输出的总矩阵模块及至少一可供2k、4k和/或8k输入信号输出并可对2k、4k和/或8k输入信号进行区分处理的输出模块,所述总矩阵模块与输入模块及输出模块电性连接;其中,所述输入模块及输出模块可以更换和热插拔。

26.再者,请参阅图2所示,所述输入模块可以包括至少一可供2k、4k和/或8k输入信号输入的接口芯片、一输入fpga模块、一输入同步时钟模块及至少一差分输出模块,所述输入同步时钟模块与输入fpga模块电性连接,所述输入fpga模块包括一可分别对8k输入信号及2k和/或4k输入信号进行处理的输入接口解码模块,所述接口芯片电性连接输入fpga模块的输入接口解码模块,所述差分输出模块与总矩阵模块电性连接,所述输入接口解码模块电性连接至差分输出模块。

27.进一步,所述输入fpga模块还可以包括一音频视频处理模块,所述音频视频处理模块电性连接于所述输入接口解码模块与差分输出模块之间,所述音频视频处理模块可以进行像素点重组、图像切割、拼接、图层叠加、淡入淡出、特效切换、羽化、字幕叠加、抠图、旋转、叠背景、叠logo、叠still台标、分辨率转换、音频矩阵、音频延迟及webserver控制处理。

28.接着,请参阅图3所示,所述输入接口解码模块可以包括一可判断并分出8k输入信号及2k和/或4k输入信号的输入矩阵模块、一8k输入信号输入处理模块、一2k和/或4k输入信号输入处理模块、一可将并行信号转为串行信号的输入逻辑模块、一输入hdcp解码模块,所述输入矩阵模块电性连接接口芯片,所述输入逻辑模块电性连接输入hdcp解码模块;所述8k输入信号输入处理模块包括依次串联电性连接的一16b/18b解码模块、一frl扰频器、一frl映射器、一rs fec解码模块及一frl打包模块;所述2k和/或4k输入信号输入处理模块包括依次串联电性连接的一tmds解码模块及一tmds扰频器;所述输入矩阵模块的2k和/或4k输入信号输出口电性连接tmds解码模块,所述输入矩阵模块的8k输入信号输出口电性连接16b/18b解码模块,所述tmds扰频器及frl打包模块电性连接输入逻辑模块,所述输入逻辑模块的视频接口电性连接至音频视频处理模块。

29.其中,所述2k和/或4k输入信号输入处理模块的tmds解码模块可以把tmds信号解成rgb数据;所述2k和/或4k输入信号输入处理模块的tmds扰频器可以把tmds的扰频数据去除,还原出源数据;所述8k输入信号输入处理模块的16b/18b解码模块可以对frl的16b/18b编码进行解码;所述8k输入信号输入处理模块的frl扰频器可以把frl的扰频数据去除,还原出源数据;所述8k输入信号输入处理模块的frl映射器可以将原来的tmds clock映射出frl的一个lane进行还原出clock;所述8k输入信号输入处理模块的rs fec解码模块可以对

rs fec编码的数据还原成源数据;所述8k输入信号输入处理模块的frl打包模块可以将所接收到的视频音频数据解包呈frl数据流;所述输入接口解码模块的输入逻辑模块可以将tmds或frl数据统一转成对应格式的数据送到后方;所述输入接口解码模块的输入hdcp解码模块可以保护蓝光,对输入的视频数据、音频数据进行加密保护的解密。

30.进一步,所述8k输入信号输入处理模块还可以包括一偏差校验器,所述偏差校验器电性连接16b/18b解码模块,所述偏差校验器可以检测16b/18b解码模块在解码后极性偏差值,以实现直流平衡调整。

31.另外,请参阅图4所示,所述输出模块可以包括一输出fpga模块、一输出同步时钟模块及至少一输出接口,所述输出同步时钟模块与输出fpga模块电性连接,所述输出fpga模块包括一可分别对8k输入信号及2k和/或4k输入信号进行处理的输出接口编码模块,所述输出接口编码模块电性连接总矩阵模块。

32.进一步,请参阅图5所示,所述输出接口编码模块可以包括一可判断并分出8k输入信号及2k和/或4k输入信号的输出逻辑模块、一8k输入信号输出处理模块、一2k和/或4k输入信号输出处理模块及一可将并行信号转为串行信号的输出矩阵模块,所述输出矩阵模块电性连接至一驱动芯片,所述输出逻辑模块电性连接输出音频视频处理模块;所述8k输入信号输出处理模块包括依次串联电性连接的一frl打包模块、一frl超级块映射模块、一rs fec编码器、一frl扰频器及一16b/18b编码模块,所述8k输入信号输出处理模块的frl打包模块电性连接输出逻辑模块的8k输入信号输出口,所述8k输入信号输出处理模块的16b/18b编码模块电性连接输出矩阵模块;所述2k和/或4k输入信号输出处理模块包括依次串联电性连接的一tmds扰频器及一tmds编码模块,所述2k和/或4k输入信号输出处理模块的tmds扰频器电性连接输出逻辑模块的2k和/或4k输入信号输出口,所述2k和/或4k输入信号输出处理模块的tmds编码模块电性连接输出矩阵模块。

33.其中,所述输出接口编码模块的输出逻辑模块可以根据协议来处理视频接口以及音频接口所接收到的数据,并分别交予两条独立的数据路径进行处理;所述输出接口编码模块的tmds扰频器可以改变数字信号序列,使传输性能更优;所述输出接口编码模块的tmds编码模块可以按照tmds信号格式进行编码;所述输出接口编码模块的frl打包模块可以按照对应格式规定的frl传输模式进行打包;所述输出接口编码模块的frl超级块映射模块可以将原来的tmds clock映射呈frl的一个lane;所述输出接口编码模块的rs fec编码器可以对数据流进行相应的处理;所述输出接口编码模块的frl扰频器可以改变数字信号序列,使传输性能更优;所述输出接口编码模块的16b/18b编码模块可以对frl所传输的数据流进行编码。

34.进一步,所述输出接口编码模块还可以包括一视频时钟控制模块及一hdcp模块,所述hdcp模块电性连接输出逻辑模块,所述总矩阵模块的音频接口电性连接输出逻辑模块,所述总矩阵模块的视频接口电性连接输出逻辑模块,所述视频时钟控制模块电性连接总矩阵模块的视频接口;所述输出接口编码模块可以对输出的视频数据、音频数据进行加密保护。

35.此外,为了便于监控所有输入源信号,本实用新型还可以包括一具备网络通讯、usb通讯、web控制、输入和场景预监功能的控制板及一扩展cxp模块,所述控制板电性连接总矩阵模块,所述扩展cxp模块电性连接总矩阵模块。

36.进一步,请参阅图6所示,所述扩展cxp模块可以包括一fpga模块及一同步时钟模块,所述扩展cxp模块的同步时钟模块电性连接扩展cxp模块的fpga模块,所述扩展cxp模块的fpga模块电性连接总矩阵模块;所述扩展cxp模块可以同时支持输入和输出,具备光纤输入接口和光纤输出接口,每个光纤输入接口或者光纤输出接口可以支持4路的rgb444 4k2k@60hz信号,所述扩展cxp模块可以把扩展输入的信号送进总矩阵模块供预监和输出,并可以接收从总矩阵模块送出来的信号送出给下一台设备。

37.综上所述,本实用新型通过输入模块及输出模块的结构设计,由于所述输入模块可以接受2k、4k和/或8k输入信号输入,且能够区分出2k、4k和/或8k输入信号,并对2k、4k和/或8k输入信号进行区分处理,所述输出模块也可以区分出2k、4k和/或8k输入信号,并对2k、4k和/或8k输入信号进行区分处理,输出2k、4k和/或8k输入信号,从而实现本实用新型可以同时支持2k、4k及8k输入和输出;其中,图1中以所述输入模块及输出模块为多个进行显示说明,但并不以此为限,每一输入模块中可以具有多个接口芯片,形成多个输入接口,于图1中,以每一输入模块形成4个输入接口为例,每一输出模块形成有4个输出接口为例进行举例说明,本实用新型的输入模块可以支持所有的视频音频接口(如:hdmi/dp/sdi/dvi/type-c/h.264/h.265/hdbaset/ndi等);经由输入模块处理后形成差分信号传给总矩阵模块,接着由总矩阵模块选择性将经由输入模块处理后形成一个或者多个差分信号对接输出模块,让本实用新型所输入的输入信号经由输入模块处理后经由总矩阵模块选择性输出至输出模块;所述总矩阵模块可以形成差分信号传递至控制板,所述控制板可以连接以太网或者通过usb接口连接外部设备,所述控制板也可以通过同步锁定接口(genlock)连接至外部设备或者通过全数字化视频和声音发送的接口(hdmi)连接外部设备;所述扩展cxp模块可以接收总矩阵模块输出的差分信号,也可以发出差分信号给总矩阵模块,所述扩展cxp模块具有输出接口和输入接口。

38.本实用新型的技术内容及技术特点已揭示如上,本实用新型的组成并不以上述为限,本领域的技术人员仍可能基于本实用新型的揭示而作各种不背离本实用新型创作精神的替换及修饰。因此,本实用新型的保护范围应不限于实施例所揭示,而应包括各种不背离本实用新型的替换及修饰,并为权利要求书所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。