1.本公开涉及一种数据处理方法及一种数据处理装置。

背景技术:

2.当前,为满足计算机网络技术以及相关业务的快速发展,大量数据例如多媒体数据(例如语音、图片、视频等媒体数据)需要传输和处理,这些多媒体数据的处理需要大量的计算资源,特别是并行计算资源。并行计算主要依靠并行处理器来完成,并行处理器是指同时可以处理多个运算的处理器。目前,主流的并行处理器有gpu(graphics processing unit,图形处理单元)、gpgpu(general-purpose computing on graphics processing units,通用图形处理器)等。

技术实现要素:

3.本公开至少一实施例提供一种数据处理方法,应用于并行处理器,所述并行处理器最大能支持m个工作项集合并行运行,且包括与所述m个工作项集合分别对应的m个指令缓存区,所述方法包括:获取对应于当前计算任务的需要并行运行的工作项集合数目p;根据所述工作项集合数目p,对所述m个指令缓存区进行配置以得到多个缓存分区,其中,响应于所述工作项集合数目p小于m,每个缓存分区的大小大于所述一个指令缓存区的大小;设置所述每个缓存分区的指针的跳转范围。

4.例如,在本公开一些实施例提供的一种数据处理方法中,根据所述工作项集合数目p,对所述m个指令缓存区进行配置,以得到多个缓存分区,该方法包括:将所述m个指令缓存区平均分配为n个缓存分区,其中,n为正整数且大于等于p,小于m。

5.例如,在本公开一些实施例提供的一种数据处理方法中,所述每个指令缓存区包括多个存储片,将所述m个指令缓存区平均分配为n个缓存分区,包括:确定所述m个指令缓存区包括的存储片总数;根据所述存储片总数和所述工作项集合数目p确定缓存分区总数n;将所述m个指令缓存区平均分配为n个缓存分区,其中,每个缓存分区包括n个存储片,n为正整数且为所述存储片总数与n的比值。

6.例如,在本公开一些实施例提供的一种数据处理方法中,根据所述存储片总数和所述工作项集合数目p确定缓存分区总数n,包括:响应于所述存储片总数能被p整除,将所述工作项集合数目p作为所述缓存分区总数n;响应于所述存储片总数不能被p整除,从能整除所述存储片总数的多个被选择数中选择大于且最靠近p的被选择数作为所述缓存分区总数n。

7.例如,在本公开一些实施例提供的一种数据处理方法中,设置所述每个缓存分区的指针的跳转范围,包括:确定所述指针的跳转步长,并使得所述指针按照所述跳转步长在所述缓存分区中循环跳转,其中,所述指针包括写指针和读指针。

8.例如,在本公开一些实施例提供的一种数据处理方法中,所述每个缓存分区按预设存储长度被划分为多个子存储区,所述多个子存储区与多个地址编号一一对应,所述每

个缓存分区包括第一端和第二端,所述多个地址编号沿所述第一端至所述第二端的方向依次递增,使得所述指针按照所述跳转步长在所述缓存分区中循环跳转,包括:确定第一目标地址编号,其中,所述第一目标地址编号为所述指针当前所在子存储区的地址编号与所述跳转步长之和;响应于所述第一目标地址编号小于等于所述多个地址编号中的最大值,所述指针在下一次跳转时跳转至所述第一目标地址编号对应的子存储区,响应于所述第一目标地址编号大于所述多个地址编号中的最大值,所述指针在下一次跳转时跳转至第二目标地址编号对应的子存储区,其中,所述第二目标地址编号为所述第一目标地址编号和所述多个地址编号的总数的余数。

9.例如,在本公开一些实施例提供的一种数据处理方法中,所述读指针包括第一读指针和第二读指针,所述写指针用于指示下一条指令的写入位置,所述第一读指针用于指示当前待读取的指令的位置,所述第二读指针用于指示所述当前待读取的指令所在的存储片,针对所述第二读指针和所述写指针,所述缓存分区按照相同的预设存储长度被划分为多个子存储区,所述第二读指针和所述写指针对应相同的地址编号范围。

10.例如,在本公开一些实施例提供的一种数据处理方法中,获取对应于当前计算任务的需要并行运行的工作项集合数目p,包括:预测所述并行处理器在执行所述当前计算任务时,需要并行运行的工作项集合的最大数目,将所述最大数目作为所述工作项集合数目p。

11.例如,本公开一些实施例提供的一种数据处理方法还包括:根据每个缓存分区的大小,调整指令预取策略。

12.例如,在本公开一些实施例提供的一种数据处理方法中,根据每个缓存分区的大小,调整指令预取策略,包括:根据所述每个缓存分区的大小,增加单次预取的指令条数,或者连续执行多次指令预取。

13.例如,本公开一些实施例提供的一种数据处理方法还包括:根据每个缓存分区的大小,调整缓存分区剩余存储容量的判断条件。

14.本公开至少一实施例还提供一种数据处理装置,应用于并行处理器,所述并行处理器最大能支持m个工作项集合并行运行,且包括与所述m个工作项集合分别对应的m个指令缓存区,所述数据处理装置包括:获取单元,配置为获取对应于当前计算任务的需要并行运行的工作项集合数目p;配置单元,配置为根据所述工作项集合数目p,对所述m个指令缓存区进行配置以得到多个缓存分区,设置所述每个缓存分区的指针的跳转范围,其中,响应于所述工作项集合数目p小于m,每个缓存分区的大小大于所述一个指令缓存区的大小。

15.例如,在本公开一些实施例提供的一种数据处理方法中,所述获取单元为寄存器,所述寄存器预存所述工作项集合数目p。

16.例如,在本公开一些实施例提供的一种数据处理方法中,所述配置单元包括多个子配置单元,所述多个子配置单元的每个对应于不同的可用工作项集合数目,且所述多个子配置单元的每个用于,根据对应的可用工作项集合数目,对所述m个指令缓存区进行配置以得到多个缓存分区,设置所述每个缓存分区的指针的跳转范围。

17.例如,在本公开一些实施例提供的一种数据处理方法中,所述多路选择器被配置根据所述工作项集合数目p,选择所述多个子配置单元之一。

附图说明

18.为了更清楚地说明本公开实施例的技术方案,下面将对实施例的附图作简单地介绍,显而易见地,下面描述中的附图仅仅涉及本公开的一些实施例,而非对本公开的限制。

19.图1a为一种gpgpu的示意性结构图;

20.图1b为一种并行处理器的示意性结构图;

21.图2a为指令缓存区的的示意性结构图;

22.图2b示出了写指针跳转示意图;

23.图2c示出了读指针跳转示意图;

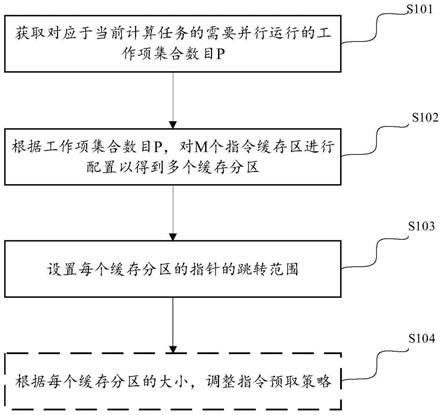

24.图3为本公开至少一实施例提供的一种数据处理方法的流程图;

25.图4示出了图3所示的数据处理方法中步骤s102的示意性流程图;

26.图5a为本公开至少一实施例提供的一种指令缓存区的结构的示意图;

27.图5b为本公开至少一实施例提供的写指针的跳转示意图;

28.图5c为本公开至少一实施例提供的读指针的跳转示意图;

29.图6为本公开至少一实施例提供的指令数据的读写流程的示意图;

30.图7为本公开至少一实施例提供的一种数据处理装置的示意图;

31.图8为本公开至少一实施例提供的配置单元的示意图。

具体实施方式

32.为使本公开实施例的目的、技术方案和优点更加清楚,下面将结合本公开实施例的附图,对本公开实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本公开的一部分实施例,而不是全部的实施例。基于所描述的本公开的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本公开保护的范围。

33.除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。同样,“一个”、“一”或者“该”等类似词语也不表示数量限制,而是表示存在至少一个。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。

34.下面通过几个具体的实施例对本公开进行说明。为了保持本公开实施例的以下说明清楚且简明,可省略已知功能和已知部(元)件的详细说明。当本公开实施例的任一部(元)件在一个以上的附图中出现时,该部(元)件在每个附图中由相同或类似的参考标号表示。

35.图1a为一种通用图形处理器的一种结构示意图。

36.在并行计算中,被执行的任务一般包括多个线程(workitem)。如图1a所示,这些线程在通用图形处理器(或称为并行计算处理器)中执行前,会在命令处理器中被划分成多个线程组(workgroup),然后经由线程组分发单元,将多个线程组分发到各个计算单元,一个

线程组中的所有线程必须要分配到同一个计算单元上执行。同时,线程组会被拆分成最小执行线程组(后简称执行组),每个执行组包含了固定数量(或小于这个固定数量)的线程,例如,32个线程。多个线程组可以在同一个计算单元中执行。在计算单元中,根据计算单元中的算数逻辑单元以及其他模块的个数,一个线程组中的多个执行组可以同时执行或分时执行。每个执行组中的多个线程会执行相同的指令,指令的读取、译码、发射都在调度模块完成,计算指令的执行在算数逻辑单元完成,而且内存执行指令会被发射到缓存中以进行读写操作。

37.在一个执行组执行计算指令时,需要的源数据(来自于通用寄存器)可能来自于之前某一条内存读取指令,这时需要一条等待指令(wait)来确保之前的内存读取指令读回的数据已经准备好。而在同一个线程组中,多个执行组之间也存在这样的同步关系。例如,一个线程组包括2个执行组,分别为执行组0和执行组1,这2个执行组的计算都需要读取内存区域a中的数据。为了节省读取的时间和带宽,一般的优化方法是执行组0读取内存区域a的一半数据,执行组1读取内存区域a的另一半数据。但对于任一个执行组,在该任一执行组执行计算指令时都需要内存区域a的所有数据,因此在执行组执行计算指令之前,需要等待执行组0和执行组1的内存读取指令都读回了数据,这时需要一条屏障指令(barrier)来阻止执行组继续执行指令,直到执行组0和执行组1的内存读取指令结束,以得到内存区域a的所有数据。

38.图1b为并行处理器的示意性结构图。

39.如图1b所示,并行处理器可以包括指令缓存器、指令调度器、指令缓存区和指令执行单元。例如,指令缓存器可以包括一片位于指令调度器外部的缓存(cache),用于缓存指令调度器从外部存储空间取回的指令数据;指令调度器用于获取指令数据以及进行指令译码和指令派发,例如,指令调度器执行取指操作,以从指令缓存器得到指令数据,并且,指令调度器对获取的指令数据进行一系列的指令仲裁、指令译码,最后将选出的指令派发至相应的指令执行单元执行;指令缓存区位于指令调度器中,用于缓存指令调度器从指令缓存器中取回的小批量指令数据。需要说明的是,在本公开中,指令数据指指令本身,而非指令操作数。

40.例如,并行处理器可以包括多个单指令多数据(single instruction multiple data,简称simd)处理器,例如,simd处理器可以为矢量处理单元(vector process unit,简称vpu),一个simd处理器可以并行处理多个线程数据。

41.例如,在一个simd处理器中,全局执行空间被划分为大量大小相等的工作项(work_item)集合,各个工作项集合并行运行,各自执行对应的指令操作。例如,一个simd处理器最大能支持m个工作项集合并行运行,并且包括与m个工作项集合分别对应的m个指令缓存区,每个指令缓存区临时存储指令调度器从指令缓存器取回的、由与该指令缓存区对应的工作项集合执行的指令数据,这里,m为正整数。

42.例如,指令调度器可以为每一个工作项集合进行独立的取指操作,指令调度器为一个工作项集合从指令缓存器取回指令数据后,需要将该笔指令数据写入与该工作项集合相对应的指令缓存区。例如,指令调度器单次取指操作所能取回的指令数据的大小可以是8个双字(double word),根据实际需要,不同处理器单次取回的指令数据的大小可以不同。

43.例如,并行处理器可以包括a个simd处理器,并行处理器中的指令调度器可以为该

a个simd处理器派发指令。如前所述,一个simd处理器同时能够容纳最多m个工作项集合在其上面运行,每一个工作项集合都对应一个独立的指令缓存区,所以并行处理器需要为a*m个工作项集合提供a*m个指令缓存区以缓存指令,这里,a为正整数。

44.图2a为指令缓存区的的示意性结构图。如图2a所示,并行处理器包括4个simd处理器,分别为单指令多数据处理器0、单指令多数据处理器1、单指令多数据处理器2和单指令多数据处理器3,每个simd处理器最多同时支持10个工作项集合并行运行,例如,单指令多数据处理器0最多同时支持工作项集合0_0、工作项集合1_0、...工作项集合9_0并行运行,单指令多数据处理器1最多同时支持工作项集合0_1、工作项集合1_1、...工作项集合9_1并行运行,以此类推。

45.例如,40个工作项集合对应的40个指令缓存区由40个位宽为128比特(也即4个双字,每个双字为32比特,每个双字由图2a中的dw表示),深度例如可以为4的独立存储器组成。例如,40个存储器分别为图2a中的mem0至mem39。例如,每个存储器包括4个存储片,一个存储片包括该存储器中同一级深度的4个双字,例如,如图2a中的存储片0为存储器mem0中同一级深度的4个双字,也即虚线框标记的dw0至dw3。

46.每个存储器的4级深度分别对应4个单指令多数据处理器,也即每个存储器组成4个单指令多数据处理器所对应的指令缓存区的一部分。例如,如图2a中的指令缓存区1所示,该指令缓存区为单指令多数据处理器0中的工作项集合0_0对应的指令缓存区,指令缓存区1由存储器mem0、存储器mem1、存储器mem2和存储器mem3的同一级深度构成,也即由存储片0、存储片1、存储片2和存储片3组成,4个存储器的同一级深度可以容纳16个双字的指令数据。

47.例如,每个指令缓存区具有写指针wptr,写指针wptr用于指示下一笔取回的指令数据写入指令缓存区的位置,指令数据一旦写入,写指针就立马跳转到下一笔指令数据应该要被写入的地址。指令调度器从指令缓存器取回指令数据后,将这笔指令数据写入到指令缓存区中写指针wptr指定的位置。

48.图2b示出了写指针跳转示意图。

49.如图2b所示,单指令多数据处理器n1所处理的工作项集合m1_n1是图2a中任一处理器所处理的某个工作项集合。如图2b所示,以单指令多数据处理器n1所处理的工作项集合m1_n1为例,写指针wptr可以有4个值,例如可以是0,1,2和3,这四个值分别指示该工作项集合对应的指令缓存区中4个存储片的起始位置。例如,每个指令缓存区的长度为16个双字,单次写入(取回)的指令数据长度为8个双字,因而,图2b中的写指针wptr的值只会在0和2之间跳转,也即写指针wptr的跳转范围为:0-》2-》0。待指令数据一次性被写入到指令缓存区的地址为0之后的8个双字位置(例如dw0到dw7的8个双字所对应的区域)后,写指针wptr的值将自动地跳转为2,此时该指令缓存区的另一半(例如dw8到dw15的8个双字所对应的区域)为空,以便容纳后续一笔取回的指令数据。

50.由于指令调度器单次取回的指令数据为8个双字,且为指令缓存区大小的一半,所以在将指令数据写入指令缓存区时需要打开连续两个存储器的写使能,具体如表1所示。

51.表1

[0052][0053]

例如,mem0_wen,mem1_wen,mem2_wen和mem3_wen分别表示4个存储片的写使能,数字1代表可用态(enable),数字0代表不可用态(disable),写指针wptr的值0,1,2,3分别表示四个存储片的起始位置。例如,如图2a所示,4个存储片分别位于4个不同的存储器,例如,当写指针wptr的值为0时,需要同时打开存储器mem0和存储器mem1的写使能,当写指针wptr的值为1时,需要同时打开存储器mem1和存储器mem2的写使能,当写指针wptr的值为2时,需要同时打开存储器mem2和存储器mem3的写使能,当写指针wptr的值为3时,需要同时打开存储器mem3和存储器mem0的写使能。

[0054]

例如,每个指令缓存区还具有读指针,例如,读指针包括第一读指针dw_rptr和第二读指针rptr,第一读指针dw_rptr用于指示当前待读取的指令数据的具体位置,第二读指针rptr用于指示当前待读取的指令数据所在的存储片。

[0055]

图2c示出了读指针跳转示意图。

[0056]

例如,如图2c所示,以图2a中的单指令多数据处理器n1所处理的工作项集合m1_n1为例,第二读指针rptr可以有4个值,例如可以是0,1,2和3,这四个值分别指示该工作项集合对应的指令缓存区中每个存储片的起始位置。由于第二读指针rptr指示待读取的指令数据所在的存储片,因此第二读指针rptr的跳转范围为:0-》1-》2-》3-》4-》0。

[0057]

例如,由于读取的指令数据的长度最小可以是1个双字,例如,当指令数据为双字指令时,第一读指针dw_rptr的跳转步长为1(1个双字),当指令数据为四字指令时,第一读指针dw_rptr的跳转步长为2(2个双字),例如,如图2c所示,第一读指针dw_rptr的跳转范围可以是0~15,dw_rptr=0表示dw0所在的位置。

[0058]

例如,如图2c中标记为1

st

的跳转范围表示第一读指针dw_rptr的跳转步长为1时的跳转范围,此时第一读指针dw_rptr的跳转范围是:0-》1-》2-》...14-》15-》0,标记为2

nd

的跳转范围表示第一读指针dw_rptr的跳转步长为2时的跳转范围,此时第一读指针dw_rptr的跳转范围是:0-》2-》4-》...12-》14-》0。

[0059]

需要说明的是,图2c所示的读指针跳转示意图仅为示意性的,第一读指针dw_rptr的跳转步长不限制为固定的1或2,第一读指针dw_rptr的跳转步长取决于待读取的指令是双字指令还是四字指令,本公开对此不作限制。

[0060]

由于待读取数据可能是1个双字也可能是两个双字,因而当第一读指针dw_rptr位于存储片的最后一个双字时,需要同时打开两个存储器的读使能,具体如表2所示。

[0061]

表2

[0062][0063]

例如,mem0_ren,mem1_ren,mem2_ren和mem3_ren分别表示4个存储器的读使能,数字1代表可用态(enable),数字0代表不可用态(disable)。例如,如图2a所示,4个存储片分别位于4个不同的存储器,第一读指针dw_rptr的值0,1,2,

…

,14,15分别对应一个指令缓存区中的双字dw的地址。例如,当第一读指针dw_rptr的值为3时,第一读指针dw_rptr位于第一个存储片的最后一个双字,需要同时打开存储器mem0和存储器mem1的读使能;当第一读指针dw_rptr的值为7时,第一读指针dw_rptr位于第二个存储片的最后一个双字,需要同时打开存储器mem1和存储器mem2的读使能;当第一读指针dw_rptr的值为11时,第一读指针dw_rptr位于第三个存储片的最后一个双字,需要同时打开存储器mem2和存储器mem3的读使能;当第一读指针dw_rptr的值为15时,第一读指针dw_rptr位于第四个存储片的最后一个双字,需要同时打开存储器mem0和存储器mem3的读使能。

[0064]

如上所示,当前并行处理器中的指令调度器和指令缓存区为并行处理器最大能运行的m个工作项集合分别单独设计了专有的硬件资源供其取指和缓存指令,也即将指令缓存区固定地划分给对应的工作项集合,每个工作项集合对应的指令缓存区大小无法随着实际需求调整。然而,有时候用户的计算任务没有那么庞大密集,在同一段时间内无法保证m个工作项集合同时并行运行,所以未运行的工作项集合的指令缓存区就会一直空闲,这些硬件资源在这一段时间无法得到有效的利用,导致这些工作项集合对应的指令缓存区的硬件资源会被浪费。

[0065]

本公开提供了一种数据处理方法以及数据处理装置。该数据处理方法包括:获取对应于当前计算任务的需要并行运行的工作项集合数目p;根据该工作项集合数目p,对该m个指令缓存区进行配置以得到多个缓存分区,其中,响应于该工作项集合数目p小于m,每个缓存分区的大小大于该一个指令缓存区的大小;设置该每个缓存分区的指针的跳转范围。

[0066]

该数据处理方法通过获取当前计算任务需要并行运行的工作项集合数目对指令缓存区进行重新配置划分,充分利用未执行计算任务的工作项集合对应的指令缓存区的硬件资源,减少硬件资源浪费。

[0067]

图3是本公开至少一实施例提供的一种数据处理方法的流程图,如图3所示,例如,该数据处理方法可以至少包括步骤s101-s103。

[0068]

例如,该数据处理方法应用于并行处理器,该并行处理器最大能支持m个工作项集合并行运行,且包括与m个工作项集合分别对应的m个指令缓存区。关于并行处理器的相关介绍可以参考图1a至图2c的相关内容,这里不再赘述,例如,由于同一时刻仅有一个simd处理器处于运行状态,因而这里的并行处理器可以指一个simd处理器。

[0069]

在步骤s101,获取对应于当前计算任务的需要并行运行的工作项集合数目p。

[0070]

例如,可以通过算法、应用程序等由并行处理器自动预测该并行处理器在执行当前计算任务时,需要并行运行的工作项集合的最大数目,并将该最大数目作为工作项集合数目p,也就是动态配置各个指令缓存区的大小。

[0071]

例如,可以由用户在使用并行处理器执行计算任务时,预测计算任务最大需要并行运行的工作项集合的数目,并将该最大数目作为工作项集合数p,也就是静态配置各个指令缓存区的大小。通过预测该并行处理器在执行当前计算任务时需要并行运行的工作项集合的最大数目,并将该最大数目作为工作项集合数目p,可以保证所有的工作项集合都能分配上对应的缓存分区。

[0072]

在步骤s102,根据工作项集合数目p,对m个指令缓存区进行配置以得到多个缓存分区。

[0073]

例如,响应于工作项集合数目p小于m,每个缓存分区的大小大于一个指令缓存区的大小。也就是说,若不需要m个工作项集合同时并行运行,则重新对m个指令缓存区进行空间配置,使得当前运行的p个工作项集合分配这m个指令缓存区,每个需要运行的工作项集合对应的缓存分区的大小会大于其原本可支配的一个指令缓存区的大小。

[0074]

例如,步骤s102可以包括:将m个指令缓存区平均分配为n个缓存分区,这里,n为正整数且大于等于p,小于m。

[0075]

图4为图3所示的数据处理方法中步骤s102的示意性流程图。如图4所示,步骤s102至少包括步骤s1021-s1023。

[0076]

在步骤s1021,确定m个指令缓存区包括的存储片总数。

[0077]

例如,每个指令缓存区包括c个存储片,因而m个指令缓存区一共包括c*m个存储片。例如,如图2a所示,每个指令缓存区包括4个存储片,因而m个指令缓存区一共包括40个存储片。

[0078]

在步骤s1022,根据存储片总数和工作项集合数目p确定缓存分区总数n。

[0079]

例如,响应于存储片总数能被p整除,将工作项集合数目p作为缓存分区总数n;响应于存储片总数不能被p整除,从能整除存储片总数的多个被选择数中选择大于且最靠近p的被选择数作为缓存分区总数n。

[0080]

例如,存储片总数为40,p为4时,存储片总数能被p整除,此时选择p作为缓存分区总数n,即缓存分区总数n为4,之后根据缓存分区总数n对40个存储片进行平均分配。

[0081]

例如,存储片总数为40,p为6时,存储片总数不能被p整除,此时从能整除40的多个被选数(也即2、4、5、8、10、20)中选择大于且最靠近p的被选择数作为缓存分区总数n,也即缓存分区总数n可以为8。

[0082]

在存储片总数不能被p整除的情况下,m个指令缓存区未实现100%的空间利用,此时仍存在小部分的空闲空间,但这种分配方式得到的缓存分区的大小仍然大于原有的一个指令缓存区的大小。

[0083]

例如,在一些实施例中,可以限制p的选择范围,也即限制p需要能整除存储片总数,此时可以实现m个指令缓存区的100%利用,不存在任何被浪费的空闲空间,硬件资源利用率得到显著提高。

[0084]

在步骤s1023,将m个指令缓存区平均分配为n个缓存分区。

[0085]

例如,每个缓存分区包括n个存储片,n为正整数且为存储片总数与n的比值。

[0086]

例如,存储片总数可以为40,n可以为4,因而每个缓存分区所包括的存储片数目n为40/n个,也即为10个。

[0087]

在步骤s103,设置每个缓存分区的指针的跳转范围。

[0088]

例如,由于在步骤s102对指令缓存区的重新配置而得到的多个缓存分区,此时的缓存分区可能包括多个指令缓存区,因而需要相应地调整指针在各个缓存分区内的跳转范围。

[0089]

例如,步骤s103可以包括:确定指针的跳转步长,并使得指针按照跳转步长在缓存分区中循环跳转。

[0090]

例如,指针包括写指针和读指针,写指针可以为如上所述的写指针wptr,读指针可以是如上所述的第一读指针dw_rptr和第二读指针rptr。

[0091]

例如,每个缓存分区可以按预设存储长度被划分为多个子存储区,多个子存储区与多个地址编号一一对应,每个缓存分区包括第一端和第二端,多个地址编号沿第一端至第二端的方向依次递增。

[0092]

例如,预设存储长度可以根据指针的跳转步长确定,例如,对于写指针wptr和第二读指针rptr,预设存储长度可以为1个存储片的长度,例如如图2a所示的存储片结构,预设存储长度可以为4个双字。例如,对于第一读指针dw_rptr,预设存储长度可以为第一读指针的最小跳转步长,例如为1个双字。

[0093]

缓存分区按照预设存储长度被划分为多个子存储区,每个子存储区都对应一个地址编号,缓存分区中指针起始跳转的一端为第一端,另一端为第二端,例如,缓存分区中位于第一端的第一个子存储区的地址编号为0,之后沿第一端向第二端的方向,子存储区的地址编号依次为1、2、3

…

。例如,地址编号可以标记在子存储区的第一个双字所在的位置。

[0094]

例如,使得该指针按照跳转步长在缓存分区中循环跳转,可以包括:确定第一目标地址编号,例如,该第一目标地址编号可以为上述指针当前所在子存储区的地址编号与该跳转步长之和;响应于第一目标地址编号小于等于多个地址编号中的最大值,指针在下一次跳转时跳转至第一目标地址编号对应的子存储区,响应于第一目标地址编号大于该多个地址编号中的最大值,该指针在下一次跳转时跳转至第二目标地址编号对应的子存储区,例如,该第二目标地址编号可以为该第一目标地址编号和该多个地址编号的总数的余数。

[0095]

例如,读指针包括第一读指针dw_rptr和第二读指针rptr,写指针用wptr于指示下一条指令的写入位置,第一读指针dw_rptr用于指示当前待读取的指令的位置,第二读指针rptr用于指示当前待读取的指令所在的存储片,针对第二读指针rptr和写指针wptr,缓存分区按照相同的预设存储长度被划分为多个子存储区,第二读指针和写指针对应相同的地址编号范围。

[0096]

例如,第一读指针dw_rptr当前指向地址编号n,根据跳转的双字数量和预设存储长度的关系,确定跳转步长,例如,当指令数据为双字指令,预设存储长度为1个双字时,第一读指针dw_rptr的跳转步长为1,当指令数据为四字指令,预设存储长度为1个双字时,第一读指针dw_rptr的跳转步长为2。

[0097]

在获得缓存分区后,对每个缓存分区进行如上所述的指针跳转范围调整,使得指令数据按照一定的规则通过读指针与写指针进行有序读写。通过上述数据处理方法,合理

配置未被使用的指令缓存区给正在运行的工作项集合使用,增大每个运行的工作项集合的指令缓存区的大小,合理利用硬件资源,减少存储空间浪费。

[0098]

例如,如图3所示,在步骤s103之后,根据本公开至少一实施例提供的一种数据处理方法,还可以包括步骤s104。

[0099]

在步骤s104,根据每个缓存分区的大小,增加单次预取的指令条数,或者连续执行多次指令预取。

[0100]

例如,在单个工作项集合对应的缓存分区变大的情况下,指令调度器可以预取更多的指令数据进行预先缓存,例如可以单次预取更多的指令数据或者连续执行多次指令预取,从而保证有足够多的指令数据满足后面执行单元的需求。

[0101]

此外,因为指令缓存器是一片cache,如果指令调度器在取指的时候没有发生命中,那么将要从下一级存储系统中取得指令数据,这个过程耗费的时间比较长,而且不可预估。本公开至少一实施例提供的处理处理方法可以通过为更少的工作项集合灵活配置更大的指令缓存区,从而减少执行单元因执行速率快于取指速率时,需要等待指令调度器从指令缓存器取回指令数据的时间,有效解决在一些场景下指令执行速率和指令调度器取指速率不匹配的问题。

[0102]

需要说明的是,本公开对具体的指令预取策略不进行限制,可以采用任意适配缓存分区大小的预取策略。

[0103]

例如,本公开至少以实施例提供的数据处理方法还可以包括:根据每个缓存分区的大小,调整缓存分区剩余存储容量的判断条件。

[0104]

由于缓存分区的大小进行了调整,因而指针跳转范围也随之进行了调整,基于第二读指针rptr和写指针wptr的数值关系可以得到指令缓存区中有效且未被执行的指令数据的数量以及缓存分区的剩余存储容量,从而控制指令调度器执行相应的取指等操作。

[0105]

例如,当第二读指针rptr和写指针wptr满足rptr 2==wptr或者rptr==wptr时,表示缓存分区剩余存储容量足够执行取指操作,例如,当rptr 2==wptr时表示指令缓存区中的有效指令数据不多,且已经被执行的指令数据的大小超过或者等于单次取回指令数据大小,此时指令缓存区即将为空,rptr==wptr表示指令缓存区已为空,也就是说,当第二读指针rptr和写指针wptr的rptr==wptr是由rptr 2==wptr得到时,表示缓存分区有空间容纳更多的指令数据。

[0106]

当然,根据缓存分区大小不同,可以适应性修改剩余存储容量的判断条件,本公开对此不做限制。

[0107]

通过调整缓存分区剩余存储容量的判断条件,使得本公开至少一实施例提供的一种数据处理方法能够在不同数量的工作项集合下正确判断指令缓存区的占用情况,从而更高效地进行指令数据的读写操作以提高并行处理器的资源利用率。

[0108]

例如,下面以图2a所示的指令缓存区结构为例,具体说明本公开至少一实施例提供的数据处理方法的流程。

[0109]

如图2a所示,并行处理器可以为任意一个simd处理器,例如,可以为单指令多数据处理器0。

[0110]

根据本公开至少一实施例提供的数据处理方法,首先,在步骤s101,获取对应于当前计算任务的需要并行运行的工作项集合数目p。

[0111]

例如,可以采用如步骤s101所述的任意方式确定执行一项计算任务最大需要并行运行的工作项集合的数目p,例如p=4。

[0112]

之后,在步骤s102,根据工作项集合数目p,对m个指令缓存区进行配置以得到多个缓存分区。

[0113]

例如,可以将m个指令缓存区平均分配为n个缓存分区。例如,单指令多数据处理器0包括10个指令缓存区,每个指令缓存区包括4个存储片,存储片总数为40,由于存储片总数40可以被4整除,那么可以将工作项集合数目p作为缓存分区总数n,也即是n=4,也即将10个指令缓存区平均分配为4个缓存分区,其中每个缓存分区包含40/4=10个存储片。

[0114]

之后,在步骤s103,设置每个缓存分区的指针的跳转范围。关于跳转范围的具体设置可以参考后续内容,这里不再赘述。

[0115]

需要说明的是,对单指令多数据处理器1、单指令多数据处理器2和单指令多数据处理器3也可以执行上述步骤,从而对单指令多数据处理器1、单指令多数据处理器2和单指令多数据处理器3中的10个指令缓存区根据缓存分区总数n进行平均分配。

[0116]

例如,缓存分区数目n可以为2、4、5、8、10,从而实现硬件资源的100%利用。当n=10时缓存分区的大小与指令缓存区的大小相同,当n=2、4、5、8时,缓存分区的大小分别是指令缓存区大小的5倍、2.5倍、2倍和1.25倍,均扩大了每个运行的工作项集合用于缓存指令的空间大小,极大地保证有效未执行指令数据在指令缓存区中的数量。

[0117]

例如,各个simd处理器可以采用相同的缓存分区总数n进行划分,例如,各个simd处理器中的10个缓存分区均按照n=4进行划分,由此得到图5a所示的缓存分区的结构示意图。

[0118]

图5a为本公开至少一实施例提供的一种指令缓存区的结构的示意图。如图5a所示,每个单指令多数据处理器对应的指令缓存区可以根据4个工作项集合被重新配置为4个缓存分区。例如,单指令多数据处理器0对应的10个指令缓存区根据4个工作项集合(工作项集合0_0、工作项集合1_0、工作项集合2_0和工作项集合3_0)被重新配置为4个缓存分区。4个单指令多数据处理器则总共对应4*4=16个缓存分区。

[0119]

例如,缓存分区1为单指令多数据处理器0中的工作项集合0_0对应的缓存分区。如图5a所示,缓存分区1可以由存储器mem0、存储器mem1、

…

、存储器mem9的10个存储器的同一级深度构成,也即由存储片0、存储片1、

…

、存储片9的10个存储片组成,每个存储片包括4个双字的存储空间,因此缓存分区1包括dw0~dw39的40个双字的存储空间,图5a中其他缓存分区以此类推。每个存储片的内部结构以及每个存储片对应的存储器与图2a所示的情况相同,此处不再赘述。

[0120]

图5b为本公开至少一实施例提供的写指针的跳转示意图,图5c为本公开至少一实施例提供的读指针的跳转示意图。

[0121]

下面以n=4为例,结合图5a、图5b和图5c,具体说明步骤s103的执行过程。

[0122]

如图5b所示,以图5a中的单指令多数据处理器0所处理的工作项集合0_0对应的缓存分区1为例,具体说明该缓存分区1的写指针wptr,第二读指针rptr和第一读指针dw_rptr的跳转方式、跳转范围、存储器使能开启情况等。

[0123]

例如,写指针wptr的跳转步长为4个双字,因此预设存储长度可以为4个双字,工作项集合0_0对应的缓存分区1总共有40个双字,例如可以是如图5a虚线框中的dw0到dw39,从

而缓存分区1可以划分为10(40/4)个子存储区。10个子存储区与10个地址编号0,1,2,

…

,9一一对应,同时,缓存分区1的第一端可以是编号为0的子存储区,第二端可以是编号为9的子存储区,地址编号0,1,2,

…

,9沿着第一端(地址编号0)至第二端(地址编号9)的方向上依次递增。

[0124]

例如,写指针wptr的值可以代表下一条指令数据在缓存分区1中所要写入的子存储区的位置,例如写指针wptr可以有10个值,例如可以是0,1,

…

,9,同时这10个值分别对应缓存分区1中每个存储片(存储片0至存储片9)的起始位置。例如,单次写入缓存分区1的指令数据的大小可以是固定的8个双字,当然不同的并行处理器可以有不同的设置,例如单次写入缓存分区1的指令数据的大小可以是4个双字、16个双字等,本公开对此不作限制。

[0125]

例如,由于单次写入缓存分区1的指令数据的大小为8个双字,每个子存储区的大小为4个双字,因而每次写入指令数据需要同时写入两个子存储区,依据地址编号的变化情况,写指针wptr的跳转步长可以设置为2。因此,如图5b所示,写指针wptr可以在地址编号0,2,4,

…

,6,8之间或地址编号1,3,

…

,7,9之间循环跳转。

[0126]

例如,指令调度器从指令缓存器取回指令数据后,将这笔指令数据写入到缓存分区中写指针wptr指定的位置。当前写指针wptr的值例如可以为0,也即对应缓存分区dw0的位置并指向第一个存储片的起始位置,取完第一笔指令数据并将指令数据写入写指针wptr指向的位置后,也即dw0到dw7的8个双字所对应的区域,确定第一目标地址编号为2(0 2),由于第一目标地址编号小于地址编号最大值9,写指针wptr的值从0跳转为2;在取完第二笔指令数据并将指令数据写入地址编号2所在的子存储区后,确定第一目标地址编号为4(2 2),由于第一目标地址编号小于地址编号最大值9,写指针wptr的值从2跳转为4,依次类推。

[0127]

按照上述的写入方式继续向缓存分区写入指令数据,并同时完成写指针wptr的值的跳转,例如写指针wptr的值跳转为8时,完成指令数据写入后,此时的第一目标地址编号为10(8 2),由于第一目标地址编号大于地址编号最大值9,写指针wptr跳转至第二目标地址编号0,第二目标地址编号0为第一目标地址编号10和多个地址编号的总数10的余数,从而,写指针wptr在缓存分区1中指向下一个位置,例如第一个存储片的起始位置dw0,之后继续上述循环。

[0128]

如前所述,在将指令数据写入缓存分区时需要打开连续两个存储片对应的两个存储器的写使能,写使能变化如表3所示。例如,mem0_wen,mem1_wen,

…

,mem9_wen分别表示10个存储器的写使能,数字1代表可用态(enable),数字0代表不可用态(disable),写指针wptr的值0,1,2,

…

,9分别对应图5a中缓存分区1的10个存储片(存储片0-存储片9)的起始位置。

[0129]

表3

[0130][0131]

当写指针wptr的值为0时,指向存储片0的起始位置,因此需要将与存储片0对应的存储器mem0的写使能mem0_wen设置为1,同时打开与存储器mem0连续的存储器mem1的写使能,将存储器mem1的写使能mem1_wen设置为1;当写指针wptr的值为1时,指向存储片1的起始位置,将与存储片1对应的存储器mem1的写使能mem1_wen设置为1,同时打开与存储器mem1连续的存储器mem2的写使能,将存储器mem2的写使能mem2_wen设置为1,并且关闭存储器mem0的写使能,也即将mem0_wen设置为0;当写指针wptr的值为2时,指向存储片2的起始位置,因此需要将与存储片2对应的存储器mem2的写使能mem2_wen设置为1,同时打开与存储器mem2连续的存储器mem3的写使能,将存储器mem3的写使能mem3_wen设置为1,并且关闭存储器mem1的写使能,也即将mem1_wen设置为0;当写指针wptr的值为3时,指向存储片3的起始位置,将与存储片3对应的存储器mem3的写使能mem3_wen设置为1,同时打开与存储器mem3连续的存储器mem4的写使能,将存储器mem4的写使能mem4_wen设置为1,并且关闭存储器mem2的写使能,也即将mem2_wen设置为0。

[0132]

当写指针wptr的值为5~9时,类似写指针wptr的值为0-4时的情况,此处不再赘述。

[0133]

例如,如图5c所示,针对第一读指针dw_rptr,预设存储长度可以为1个双字,缓存分区1总共有40个双字,例如可以是dw0到dw39,从而该缓存分区可以划分为40个子存储区。例如,针对第一读指针dw_rptr,40个子存储区与40个地址编号0,1,2,

…

,39一一对应,同时,缓存分区1的第一端可以是地址编号为0的子存储区,缓存分区1的第二端可以是地址编号为39的子存储区,地址编号0,1,2,

…

,39沿着第一端(地址编号0)至第二端(地址编号39)的方向上依次递增。

[0134]

如图5c所示,第一读指针dw_rptr实际可以指向下一条要被执行的指令,第一读指针dw_rptr的跳转范围例如可以是0~39,即为缓存分区1中可以容纳双字的总数量40。例如,第一读指针dw_rptr的跳转步长可以设置为1或者2,当跳转步长为1时,表示待读取的指令数据为双字指令,当跳转步长为2时,表示待读取的指令数据为四字指令。

[0135]

例如,第一读指针dw_rptr可以在0~39之间依据跳转步长循环跳转。

[0136]

例如,第一读指针dw_rptr当前指向地址编号0,也即第一读指针dw_rptr指向存储

片0的起始位置,例如可以是图5c中的dw0,若第一读指针dw_rptr的跳转步长为1时,第一目标地址编号可以为1(0 1),因为第一目标地址编号1小于与第一读指针dw_rptr相对应的多个地址编号的最大值39,从而第一读指针dw_rptr在下一次跳转时跳转至第一目标地址编号1对应的子存储区dw1。所以,第一读指针dw_rptr从地址编号0跳转至地址编号1,第一读指针dw_rptr跳转后(如图5c中dw0至dw1处的1

st next)指向dw1;例如,若第一读指针dw_rptr的跳转步长为2时,第一目标地址编号可以为2(0 2),因而第一读指针dw_rptr在下一次跳转时跳转至第一目标地址编号2对应的子存储区dw2。所以,第一读指针dw_rptr从地址编号0跳转至地址编号2,第一读指针dw_rptr跳转后(如图5c中dw0至dw2处的2

nd next)指向dw2。

[0137]

例如,第一读指针dw_rptr当前指向地址编号38时,也即第一读指针dw_rptr指向子存储区dw38,若第一读指针dw_rptr的跳转步长为1时,第一目标地址编号可以为39(38 1),因而,第一读指针dw_rptr在下一次跳转时跳转至第一目标地址编号39对应的子存储区dw39。所以,第一读指针dw_rptr从地址编号38跳转至地址编号39,第一读指针dw_rptr跳转后(如图5c中dw38至dw39处的1

st next)指向dw39;例如,若第一读指针dw_rptr的跳转步长为2时,第一目标地址编号可以为40(38 2),因为第一目标地址编号40大于与第一读指针dw_rptr相对应的多个地址编号的最大值39,从而第一读指针dw_rptr在下一次跳转时跳转至第二目标地址编号对应的子存储区,第二目标地址编号可以为第一目标地址编号40和多个地址编号的总数40的余数,也即第二目标地址编号为0,从而第一读指针dw_rptr从地址编号38跳转至地址编号0,第一读指针dw_rptr跳转后(如图5c中dw38至dw0处的2

nd next)指向dw0。

[0138]

例如,第一读指针dw_rptr当前指向地址编号为39时,也即第一读指针dw_rptr指向子存储区dw39,若第一读指针dw_rptr的跳转步长为1时,第一目标地址编号可以为40(39 1),参考如前所述的内容,第一读指针dw_rptr从地址编号39跳转至地址编号0,第一读指针dw_rptr跳转后(如图5c中的dw39至dw0处的1

st next)指向dw0;例如,若第一读指针dw_rptr的跳转步长为2时,第一目标地址编号可以为41(39 2),第二目标地址编号为1,因而,第一读指针dw_rptr从地址编号39跳转至第二地址编号11,第一读指针dw_rptr跳转后(如图5c中的dw39至dw1处的2

nd next)指向的存储地址为dw1。

[0139]

需要说明的是,上述实施例仅为示意性描述,不同指令可以对应不同的位宽,例如,指令数据可以为32比特或64比特等,根据每次待读取的指令数据的长度不同,第一读指针dw_rptr的跳转步长可以为1也可以为2,当然,第一读指针dw_rptr的跳转步长也可以是其他值,例如,在指令数据为128比特时,跳转步长还可以为4,本公开对此不作限制。

[0140]

例如,针对第二读指针rptr,预设存储长度可以为4个双字,缓存分区1总共有40个双字,从而缓存分区1可以划分为40/4个,即为10个子存储区,例如10个子存储区可以分别为图5a中的存储片0至存储片9。例如,针对第二读指针rptr,该10个子存储区与10个地址编号(0,1,2,

…

,9)一一对应,同时,缓存分区1的第一端可以是地址编号为0的子存储区,缓存分区1的第二端可以是地址编号为9的子存储区,地址编号0,1,2,

…

,9沿着缓存分区1的第一端(地址编号0)至第二端(地址编号9)的方向上依次递增。

[0141]

如图5c所示,例如第二读指针rptr可以有10个值,例如可以是0,1,2,

…

,9,分别指向地址编号0-地址编号9。例如,第二读指针rptr单次跳转4个双字,针对第二读指针rptr的

每个子存储区的大小也为4个双字,因而第二读指针rptr的跳转步长可以为1。例如,第二读指针rptr可以在0~9之间依次循环跳转:

[0142]

例如,第二读指针rptr当前指向地址编号0(例如对应缓存分区1中dw0的位置),也即指向第一个子存储区/存储片0的起始位置,当待读取指令数据位于第二个子存储区时,第二读指针rptr进行跳转,此时第一目标地址编号可以为1(0 1),第二读指针rptr从地址编号0跳转至地址编号1,第二读指针rptr跳转后(如图5c中dw0至dw4处的next)指向dw4,也即第二个子存储区/存储片1的起始位置;当待读取指令数据位于第三个子存储区时,第二读指针rptr进行跳转,此时第一目标地址编号可以为2(1 1),第二读指针rptr从地址编号1跳转至地址编号2,第二读指针rptr跳转后(如图5c中dw4至dw8处的next)指向dw8,也即第三个子存储区/存储片2的起始位置,类似的,第二读指针rptr按照如上方式进行依次跳转,直到跳转至最后一个子存储区,也即存储片9的起始位置后,在下一次跳转(如图5c中dw36至dw0处的next)时跳转至地址编号0并指向dw0,完成一轮循环。

[0143]

之后,第二读指针rptr继续执行上述循环跳转,重复之处不再赘述。

[0144]

如前所述,从缓存分区读取指令数据时需要打开连续两个存储片对应的两个存储器的读使能,读使能变化如表4所示。

[0145]

表4

[0146]

[0147][0148]

例如,mem0_ren、mem1_ren、mem2_ren...、mem9_ren分别表示10个存储器(也即图5a中的存储器mem0至存储器mem9)的读使能,数字1代表可用态(enable),数字0代表不可用态(disable)。例如,如图5a所示,10个存储片分别位于10个不同的存储器,第一读指针dw_rptr的值0,1,2,

…

,38,39分别对应缓存分区中的双字dw0至dw39。

[0149]

例如,当第一读指针dw_rptr的值为0~3时,指向双字dw0至dw3且均属于存储片0,因此需要将与存储片0对应的存储器mem0的读使能mem0_ren设置为1,并且在第一读指针dw_rptr的值为3时打开与存储器mem0连续的存储器mem1的读使能,将存储器mem1的读使能mem1_ren设置为1;当第一读指针dw_rptr的值为4~7时,指向双字dw4至dw7且均属于存储片1,因此需要将与存储片1对应的存储器mem1的读使能mem1_ren设置为1,关闭存储器mem0的读使能,也即设置存储器mem0的读使能mem0_ren为0,并且在第一读指针dw_rptr的值为7时打开与存储器mem1连续的存储器mem2的读使能,将存储器mem2的读使能mem2_ren设置为1;例如,当第一读指针dw_rptr的值为8~11时,指向双字dw8至dw11且均属于存储片3,因此需要将与存储片3对应的存储器mem3的读使能mem3_ren设置为1,关闭存储器mem1的读使能,也即设置存储器mem1的读使能mem1_ren为0,并且在第一读指针dw_rptr的值为11时打开与存储器mem3连续的存储器mem3的读使能,将存储器mem3的读使能mem3_ren设置为1。

[0150]

当第一读指针dw_rptr的值为12~39时,类似第一读指针dw_rptr的值为0~3、4~7或8~11时的情况,此处不再赘述。

[0151]

从而,可以根据上述的方式实现在缓存分区根据工作项集合数目重新配置和划分为多个缓存分区的情况下,对每个缓存分区进行重新配置,调整指令数据的读指针的跳转

范围与跳转步长,以及对指令数据按照一定的指令数据长度通过读指针有序从指令缓存区读取指令数据,例如按照一定的指针跳转步长循环从缓存分区读取指令数据。

[0152]

类似的,在n=2、5、8时,按照如上所述的方式调整每个缓存分区的指针跳转范围。

[0153]

例如,在n=2时,每个缓存分区包括20个存储片,每个存储片包括4个双字,对于写指针wptr和第二读指针rptr,预设存储长度为4个双字,缓存分区被划分为20个子存储区,20个子存储区分别对应的地址编号为0~19,如前所述,写指针wptr的跳转步长为2(8个双字),第二读指针rptr的跳转步长为1(4个双字),因此,写指针wptr的跳转范围是:0-》2-》4-》6-》8-》10-》12-》14-》16-》18-》0,第二读指针rptr的跳转范围是:0-》1-》2-》3-》4-》5-》6-》7-》8-》9-》10-》11-》12-》13-》14-》15-》16-》17-》18-》19-》0;对于第一读指针dw_rptr,预设存储长度为1个双字,缓存分区被划分为80个子存储区,80个子存储区分别对应的地址编号为0~79,如前所述,第一读指针dw_rptr的跳转步长为1(1个双字)或2(2个双字),因此,第一读指针dw_rptr的跳转范围为0~79,根据指令数据的不同类型选择跳转步长为1或2,例如,当第一读指针dw_rptr跳转至79时,在下一条指令数据的长度为1个双字时,第一读指针dw_rptr跳转至0。

[0154]

需要说明的是,在上述实施例中,以每个存储片包括4个双字、写指针每次跳转8个双字、第二读指针每次跳转4个双字、第一读指针每次跳转1个或2个双字为例进行描述,但本公开不限于此,本领域技术人员可以根据需要适应性改变存储片的长度及跳转步长。

[0155]

例如,在n=5时,每个缓存分区包括8个存储片,每个存储片包括4个双字,对于写指针wptr和第二读指针rptr,预设存储长度为4个双字,缓存分区被划分为8个子存储区,8个子存储区分别对应的地址编号为0~7,如前所述,写指针wptr的跳转步长为2(8个双字),第二读指针rptr的跳转步长为1(4个双字),因此,写指针wptr的跳转范围是:0-》2-》4-》6-》0,第二读指针rptr的跳转范围是:0-》1-》2-》3-》4-》5-》6-》7-》0;对于第一读指针dw_rptr,预设存储长度为1个双字,缓存分区被划分为32个子存储区,32个子存储区分别对应的地址编号为0~31,如前所述,第一读指针dw_rptr的跳转步长为1(1个双字)或2(2个双字),因此,第一读指针dw_rptr的跳转范围为0~31,根据指令数据的不同类型选择跳转步长为1或2,例如,当第一读指针dw_rptr跳转至31时,在下一条指令数据的长度为1个双字时,第一读指针dw_rptr跳转至0。

[0156]

例如,在n=8时,每个缓存分区包括5个存储片,每个存储片包括4个双字,对于写指针wptr和第二读指针rptr,预设存储长度为4个双字,缓存分区被划分为5个子存储区,5个子存储区分别对应的地址编号为0~4,如前所述,写指针wptr的跳转步长为2(8个双字),第二读指针rptr的跳转步长为1(4个双字),因此,写指针wptr的跳转范围是:0-》2-》4-》1-》3-》0,第二读指针rptr的跳转范围是:0-》1-》2-》3-》4-》0;对于第一读指针dw_rptr,预设存储长度为1个双字,缓存分区被划分为20个子存储区,20个子存储区分别对应的地址编号为0~19,如前所述,第一读指针dw_rptr的跳转步长为1(1个双字)或2(2个双字),因此,第一读指针dw_rptr的跳转范围为0~19,根据指令数据的不同类型选择跳转步长为1或2,例如,当第一读指针dw_rptr跳转至19时,在下一条指令数据的长度为1个双字时,第一读指针dw_rptr跳转至0。

[0157]

根据本公开至少一实施例提供的一种数据处理方法,上述不同的工作项集合数使得该数据处理方法可以兼容多种不同数量的工作项集合,并根据实际的工作项集合数目相

应地重新配置指令缓存区以得到不同配置的多个缓存分区,同时,根据不同的缓存分区配置与之相应的指令数据读写方式,进而可以在不同个数的工作项集合下提高并行处理器的资源利用率。

[0158]

例如,可以根据写指针wptr,第二指针rptr和第一读指针dw_rptr,得到指令缓存区中有效且未被执行的指令数据的数量以及指令缓存区中空闲的空间大小,从而控制指令调度器执行相应的取指等操作。整个过程的流程如图6所示。

[0159]

图6为本公开至少一实施例提供的指令数据的读写流程的示意图。下面结合图6和图5a,具体说明指令数据的读写流程。

[0160]

如图6所示,若缓存分区为空或即将为空,指令调度器从指令缓存器读取指令数据,例如可以读取长度为8个双字的指令数据,指令调度器将指令数据写入缓存分区,例如可以将读取的指令数据写入缓存分区中的连续两个存储片上。

[0161]

之后,写指针wptr跳转至下一个写入位置,例如,写指针wptr当前指向为地址编号0,则跳转至地址编号2。

[0162]

之后,指令调度器执行读取指令的相关操作,并且在执行完读取指令操作后,根据指令数据的大小将第一读指针dw_rptr跳转对应的长度。例如可以将第一读指针dw_rptr在地址编号0到地址编号a(例如,对于如图5a所示的缓存分区,a为39)之间按跳转步长为1或2循环跳转。例如,若跳转步长为1,当第一读指针dw_rptr大于等于最大地址编号a时,下一次跳转至地址编号0,也即第一读指针dw_rptr=0。

[0163]

同时,判断第一读指针dw_rptr是否指向下一个存储片,若第一读指针dw_rptr指向下一个存储片,则第二读指针rptr的值增加1,并使得第二读指针rptr的值增加到第二读指针rptr对应的最大地址编号b(例如,对于如图5a所示的缓存分区,b为9),下一次跳转至地址编号0,也即第二读指针rptr=0。

[0164]

例如,如图6所示,可以根据写指针wptr和第二读指针rptr,确定指令缓存区是否为空或即将为空,例如,针对图5a所示的缓存分区,当满足rptr!=wptr或rptr-1!=wptr时,也即rptr不等于wptr或者rptr-1不等于wptr时,判断缓存分区为空或有空间接收下一笔指令数据,可以由指令调度器执行取指操作。

[0165]

本公开至少一实施例还提供了一种数据处理装置。图7是本公开至少一实施例提供的一种数据处理装置的示意图。

[0166]

如图7所示,例如,该数据处理装置100可以包括获取单元101和配置单元102。

[0167]

例如,获取单元101可以配置为获取对应于当前计算任务的需要并行运行的工作项集合数目p。

[0168]

配置单元102可以配置为根据工作项集合数目p,对m个指令缓存区进行配置以得到多个缓存分区,设置每个缓存分区的指针的跳转范围,这里,响应于工作项集合数目p小于m,每个缓存分区的大小大于一个指令缓存区的大小。

[0169]

例如,获取单元101可以是寄存器,该寄存器可以预存工作项集合数p,例如,用户预先判断当前计算任务对应的最大需要运行的工作项集合数目p,将工作项集合数目p通过寄存器写入数据处理装置。

[0170]

例如,获取单元101配置为执行获取对应于当前计算任务的需要并行运行的工作项集合数目p时,包括执行以下步骤:预测并行处理器在执行当前计算任务时,需要并行运

行的工作项集合的最大数目,将最大数目作为工作项集合数目p。

[0171]

例如,配置单元102包括分配子单元和设置子单元。

[0172]

例如,分配子单元配置为执行根据工作项集合数目p,对m个指令缓存区进行配置,以得到多个缓存分区时,包括执行以下操作:将m个指令缓存区平均分配为n个缓存分区,这里,n为正整数且大于等于p,小于m。

[0173]

例如,每个指令缓存区包括多个存储片,分配子单元执行将m个指令缓存区平均分配为n个缓存分区时,包括执行以下操作:确定m个指令缓存区包括的存储片总数;根据存储片总数和工作项集合数目p确定缓存分区总数n;将m个指令缓存区平均分配为n个缓存分区,例如,每个缓存分区包括n个存储片,n为正整数且为存储片总数与n的比值。

[0174]

例如,分配子单元执行根据存储片总数和工作项集合数目p确定缓存分区总数n时,包括执行以下操作:响应于存储片总数能被p整除,将工作项集合数目p作为缓存分区总数n;响应于存储片总数不能被p整除,从能整除存储片总数的多个被选择数中选择大于且最靠近p的被选择数作为缓存分区总数n。

[0175]

例如,设置子单元配置为设置每个缓存分区的指针的跳转范围时,包括执行以下操作:确定指针的跳转步长,并使得指针按照跳转步长在缓存分区中循环跳转,例如,指针包括写指针和读指针。

[0176]

例如,每个缓存分区按预设存储长度被划分为多个子存储区,多个子存储区与多个地址编号一一对应,每个缓存分区包括第一端和第二端,多个地址编号沿第一端至第二端的方向依次递增。设置子单元执行使得指针按照跳转步长在缓存分区中循环跳转时,包括执行以下操作:确定第一目标地址编号,其中,第一目标地址编号为指针当前所在子存储区的地址编号与跳转步长之和;响应于第一目标地址编号小于等于多个地址编号中的最大值,指针在下一次跳转时跳转至第一目标地址编号对应的子存储区,响应于第一目标地址编号大于多个地址编号中的最大值,指针在下一次跳转时跳转至第二目标地址编号对应的子存储区,这里,第二目标地址编号为第一目标地址编号和多个地址编号的总数的余数。

[0177]

例如,读指针包括第一读指针dw_rptr和第二读指针rptr,写指针wptr用于指示下一条指令的写入位置,第一读指针dw_rptr用于指示当前待读取的指令的位置,第二读指针rptr用于指示当前待读取的指令所在的存储片,针对第二读指针rptr和写指针wptr,缓存分区按照相同的预设存储长度被划分为多个子存储区,第二读指针rptr和写指针wptr对应相同的地址编号范围。

[0178]

配置单元102可以包括多个子配置单元,多个子配置单元的每个对应于不同的工作项集合数目p,且多个子配置单元的每个用于,根据对应的工作项集合数目,对m个指令缓存区进行配置以得到多个缓存分区,设置每个缓存分区的指针的跳转范围。

[0179]

图8为本公开至少一实施例提供的数据处理装置的示意性结构图。

[0180]

如图8所示,配置单元102可以根据不同的工作项集合数p对缓存分区进行相应不同的配置,从而得到多个配置子单元。例如可以根据k个不同的工作项集合数目p1、p2、

…

、pk将指令缓存区配置为指令缓存区配置1、指令缓存区配置2、

…

、指令缓存区配置k,该k个指令缓存区配置分别对应k个配置子单元1021、配置子单元1022、

…

、配置子单元102k。例如,每个配置子单元可以将将多个指令缓存区按照工作项集合数目进行配置得到与之对应的多个缓存分区。例如,配置子单元1022对应的工作项集合数目p2=4,从而可以利用本公开

至少一实施例提供的数据处理装置将多个指令缓存区进行配置得到指令缓存区配置2,例如指令缓存区配置2可以是:多个指令缓存区被分为4个缓存分区,每个缓存分区的指针的跳转范围根据缓存分区大小进行相应设置,例如可以将写指针wptr配置为在范围0~10之间跳转,将第一读指针dw_rptr配置为在范围0~39之间跳转,将第二读指针rptr配置为在范围0~19之间跳转。例如,针对图2a所示的指令缓存区结构,配置子单元的个数可以为5,例如,配置子单元1021所得到的指令缓存区配置1包括在n=2时的指令缓存区配置,也即此时10个指令缓存区被划分成2个缓存分区,每个缓存分区的指针跳转范围随之调整,类似的,配置子单元1022所得到的指令缓存区配置2包括在n=4时的指令缓存区配置,配置子单元1023所得到的指令缓存区配置3包括在n=5时的指令缓存区配置,配置子单元1024所得到的指令缓存区配置4包括在n=8时的指令缓存区配置,配置子单元1025所得到的指令缓存区配置5包括在n=10时的指令缓存区配置。

[0181]

例如,数据处理装置100还包括多路选择器,例如,多路选择器被配置根据工作项集合数目p,选择多个子配置单元之一,在带有数据处理装置100的硬件电路工作时,按照选择的子配置单元得到的指令缓存区配置执行取指等操作。

[0182]

例如,配置单元102包括存储在存储器中的代码和程序;处理器可以执行该代码和程序以实现如上所述的配置单元102的一些功能或全部功能。例如,配置单元102可以是专用硬件器件,用来实现如上所述的配置单元102的一些或全部功能。例如,配置单元102可以是一个电路板或多个电路板的组合,用于实现如上所述的功能。在本技术实施例中,该一个电路板或多个电路板的组合可以包括:(1)一个或多个处理器;(2)与处理器相连接的一个或多个非暂时的存储器;以及(3)处理器可执行的存储在存储器中的固件。

[0183]

需要说明的是,获取单元101用于实现图3所示的步骤s101,配置单元102用于实现图3所示的步骤s102和步骤s103,其中配置子单元用于实现图3所示的步骤s102,设置子单元用于实现图3所示的步骤s103。从而关于获取单元101的具体说明可以参考上述数据处理方法的实施例中图3所示的步骤s101的相关描述,关于配置子单元的具体说明可以参考上述数据处理方法的实施例中图3所示的步骤s102的相关描述,关于设置子单元的具体说明可以参考上述数据处理方法的实施例中图3所示的步骤s103的相关描述。

[0184]

数据处理装置100可以实现与前述数据处理方法相似的技术效果,该数据处理装置100通过获取当前计算任务需要并行运行的工作项集合数目对指令缓存区进行重新配置划分,充分利用未执行计算任务的工作项集合对应的指令缓存区的硬件资源,减少硬件资源浪费。

[0185]

对于本公开,还有以下几点需要说明:

[0186]

(1)本公开实施例附图只涉及到与本公开实施例涉及到的结构,其他结构可参考通常设计。

[0187]

(2)为了清晰起见,在用于描述本发明的实施例的附图中,层或结构的厚度和尺寸被放大。可以理解,当诸如层、膜、区域或基板之类的元件被称作位于另一元件“上”或“下”时,该元件可以“直接”位于另一元件“上”或“下”,或者可以存在中间元件。

[0188]

(3)在不冲突的情况下,本公开的实施例及实施例中的特征可以相互组合以得到新的实施例。

[0189]

以上仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,本公开的

保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。