1.本公开大体上涉及半导体装置,例如半导体存储器装置。

背景技术:

2.半导体存储器装置可包含用于存储信息的多个存储器单元。所存储的信息可被编码为二进制数据,且每一存储器单元可存储信息的单个位。存储器可使用随机数以用于各种应用。举例来说,以对其时序的随机性程度执行某些操作可为有益的,且随机数可用于注入随机性。然而,半导体存储器装置可通常为确定性装置,且其可能难以产生随机数。

技术实现要素:

3.根据本公开的实施例,提供了一种设备,其包括:存储器阵列,其包括多个字线,其中所述存储器阵列被配置成存取所述多个字线中的选定者作为存取操作的部分;电压,其耦合到所述存储器阵列,其中所述电压作为所述存取操作的部分改变;以及随机数发生器,其被配置成基于所述电压产生随机数。

4.根据本公开的实施例,提供了一种设备,其包括:多个存储器组;多个电压,其各自与所述多个存储器组中的一个相关联;以及多个随机数发生器,其各自被配置成基于所述多个电压中的相应一个产生随机数。

5.根据本公开的实施例,提供了一种方法,其包括:将电压提供到存储器阵列;对所述存储器阵列执行存取操作,其中所述存取操作改变所述电压;以及基于所述电压产生随机数。

附图说明

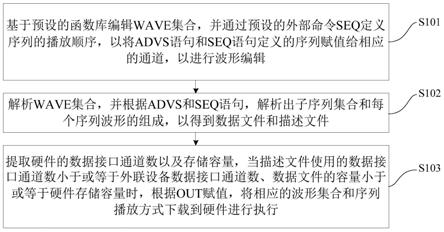

6.图1为根据本公开的实施例的半导体装置的框图。

7.图2为根据本公开的一些实施例的到存储器的不同组的电压分布的框图。

8.图3为根据本公开的实施例的随机数发生器的框图。

9.图4为根据本公开的一些实施例的随机数发生器的不同组织的框图。

10.图5为根据本公开的实施例的刷新控制电路的框图。

11.图6为根据本公开的一些实施例的基于存储器的电压产生随机数的方法的框图。

具体实施方式

12.某些实施例的以下描述在本质上仅是示例性的,且绝非意在限制本公开的范围或其应用或用途。在对本发明的系统和方法的实施例的以下详细描述中,参考形成本文的一部分的附图,且借助于图示展示可在其中实践所描述的系统和方法的特定实施例。足够详细地描述这些实施例,以使所属领域的技术人员能够实践当前公开的系统和方法,且应理解,可利用其它实施例,且在不脱离本公开的精神和范围的情况下可进行结构和逻辑改变。此外,为清晰起见,某些特征的详细描述在其对于所属领域的技术人员来说将显而易见时

将不予以论述,以免使本公开的实施例的描述混淆不清。因此,以下详细描述不应以限制性的意义来理解,且本公开的范围仅由所附权利要求书来限定。

13.例如存储器装置的半导体装置可产生可在存储器的各种操作中使用的一或多个随机数。举例来说,存储器可沿着地址总线定期对地址进行取样以便确定对不同地址的存取的数目(和/或速率),例如以确定一或多个行是否正在被锤击。可能有益的是以随机性的程度进行取样。随机数可用于将随机性注入到取样的时序中。各种方法可用于产生随机数,然而存储器(和一般来说的半导体装置)通常可为确定性的。举例来说,可产生可接着用于产生随机数的种子值。此确定性行为可减少随机数的

‘

随机性’,因为所述确定性行为有可能基于对确定性过程产生随机数的方式的了解而确定将产生哪一随机数。确定性行为还可减少装置间随机性,因为所述确定性行为有可能基于对产生相同类型的不同装置的随机数的过程的了解而猜测装置的随机行为。以与装置的物理质量相关联的方式产生随机数可为有用的,甚至相同类型的不同装置之间的物理质量也可能不同。

14.本公开涉及用于基于电压的随机数产生的设备、系统和方法。存储器装置可使用各种电压(例如,以表示不同逻辑电平的信号、驱动各种操作、对各种组件供电等)。当存储器执行操作时,在操作开始时,由电流牵引所引起的电压中的一或多个可发生变化(例如,

‘

下降’)。此下降的准确值可部分地基于裸片的物理结构,装置的物理结构可由于生产工艺的差异而不同。下降还可基于正执行哪种操作。举例来说,如果正执行对存储器的存取操作,那么正存取哪些存储器单元可改变下降的值。

15.存储器可包含耦合到存储器的一或多个电压的随机数发生器。随机数发生器可包含可耦合到电压的模/数转换器(adc)。响应于各种触发事件(例如,存取操作),adc可将电压转换成数字值。数字值可直接用作随机数,或可用作用于产生基于种子值产生随机数的序列发生器(例如,散列电路、线性反馈移位寄存器)的种子值。在一些实施例中,可存在用于存储器的每一组的不同随机数发生器。在一些实施例中,可组合组级随机数以产生总存储器随机数。在一些实施例中,基于电压的随机数可与随机性的另一来源(例如,熔断信息、不同随机数)组合以进一步增加随机数的随机性。基于电压的随机数的使用可能是有利的,因为可能难以控制或预测随机数,且与其它类型的随机数发生器相比,产生随机数的电路系统(例如,adc)可能是相对较小且简单的电路。

16.图1为根据本公开的实施例的半导体装置的框图。半导体装置100可为半导体存储器装置,例如集成在单个半导体芯片上的动态随机存取存储器(dynamic random access memory,dram)装置。

17.半导体装置100包含存储器阵列118。存储器阵列118示出为包含多个存储器组。在图1的实施例中,存储器阵列118示出为包含八个存储器组bank0到bank7。其它实施例的存储器阵列118中可包含更多或更少的组。每一存储器组包含多个字线wl、多个位线bl以及布置在多个字线wl与多个位线bl的相交处的多个存储器单元mc。字线wl的选择由行解码器108执行,且位线bl的选择由列解码器110执行。在图1的实施例中,行解码器108包含用于每一存储器组的相应行解码器,且列解码器110包含用于每一存储器组的相应列解码器。位线bl耦合到相应感测放大器(samp)。来自位线bl的读取数据由感测放大器samp放大,且通过互补本地数据线(liot/b)、传输门(tg)和互补主数据线(miot/b)传送到读取/写入放大器,以传送到局部锁存器120。接着可将数据提供到串行器(未图示),且接着可通过i/o电路122

将串行化数据提供到数据端子dq。相反地,写入数据通过并行器121从dq焊盘传送到局部锁存器120。写入数据从局部锁存器120通过互补主数据线miot/b、传输门tg和互补本地数据线liot/b传送到感测放大器samp,且写入耦合到位线bl的存储器单元mc中。

18.半导体装置100可采用多个外部端子,所述外部端子包含:耦合到命令和地址总线以接收命令和地址的命令和地址(c/a)端子;和用以接收时钟ck和/ck的cs信号时钟端子;用以提供数据的数据端子dq;以及用以接收电源电势vdd、vss、vddq和vssq的电源端子。

19.时钟端子供应有外部时钟ck和/ck,所述外部时钟被提供到输入电路112。外部时钟可互补。输入电路112基于ck和/ck时钟产生内部时钟iclk。iclk时钟被提供到命令解码器106且提供到内部时钟发生器114。内部时钟发生器114基于iclk时钟提供各种内部时钟lclk。lclk时钟可用于各种内部电路的时序操作。内部数据时钟lclk被提供到输入/输出电路122,以对包含在输入/输出电路122中的电路的操作进行计时,例如被提供到数据接收器以对写入数据的接收进行计时。存储器装置100还可包含数据选通端子dqs。数据选通信号可用于管理对存储器装置100的写入操作的计时,而一或多个系统时钟信号clk和/clk可管理其它操作的计时,例如读取操作、刷新操作和其它操作。

20.c/a端子可供应有存储器地址。经由命令/地址输入电路102将供应到c/a端子的存储器地址传送到地址解码器104。地址解码器104接收地址,且将已解码的行地址xadd供应到行解码器108并将已解码的列地址yadd供应到列解码器110。地址解码器104还可供应已解码的组地址badd,所述已解码的组地址可指示含有已解码的行地址xadd和列地址yadd的存储器阵列118的组。c/a端子可供应有命令。命令的实例包含用于控制各种操作的时序的时序命令、用于存取存储器的存取命令(例如,用于执行读取操作的读取命令和用于执行写入操作的写入命令)以及其它命令和操作。存取命令可与用以指示待存取的一或多个存储器单元的一或多个行地址xadd、列地址yadd和组地址badd相关联。

21.命令可经由命令/地址输入电路102作为内部命令信号提供到命令解码器106。命令解码器106包含对内部命令信号进行解码以产生各种内部信号的电路和用于执行操作的命令。举例来说,命令解码器106可提供行命令信号以选择字线和列命令信号以选择位线。

22.装置100可接收为读取命令的访问命令。当接收到读取命令并及时向组地址、行地址及列地址供应读取命令时,从存储器阵列118中对应于行地址和列地址的存储器单元读取读取数据。通过命令解码器106接收读取命令,所述命令解码器提供内部命令,使得数据从存储器单元读出(例如,沿着lio和mio)到局部锁存器120。举例来说,可激活由行和列地址指定的一或多个字线和一或多个数字线,且可沿着数字线将数据从存储器单元读出到感测放大器。数据可传送到读取/写入放大器(rwamp)120,所述读取/写入放大器可将读取数据提供到io电路122,所述io电路继而可将读取数据提供到数据端子dq。

23.装置100可接收为写入命令的存取命令。当接收到写入命令并及时向组地址、行地址和列地址供应写入命令时,通过dq端子将写入数据供应到读写放大器(rwamp)120。将提供到rwamp 120的写入数据写入到存储器阵列118中对应于行地址和列地址的存储器单元。举例来说,可通过耦合到系统电压来激活与行地址xadd相关联的一或多个字线。可激活与列地址相关联的位线,且可沿着局部i/o线liot/b将写入数据提供到感测放大器,且接着沿着已激活的位线将写入数据提供到已激活的位线和字线的相交处的存储器单元。接着将写入数据写入到那些存储器单元。

24.作为自刷新模式的部分,装置100还可接收使其实行一或多个刷新操作的命令。在一些实施例中,自刷新模式命令可在外部发布到存储器装置100。在一些实施例中,自刷新模式命令可由装置的组件定期产生。在一些实施例中,当外部信号指示自刷新进入命令时,还可激活刷新信号aref。刷新信号aref可为当命令解码器106接收指示进入自刷新模式的信号时被激活的脉冲信号。刷新信号aref可紧接在命令输入之后被激活,且此后可以所要内部时序循环地激活。刷新信号aref可用于在自刷新模式期间控制刷新操作的时序。因此,刷新操作可自动继续。自刷新退出命令可使刷新信号aref的自动激活停止且返回到空闲(idle)状态。刷新信号aref被供应到刷新控制电路116。刷新控制电路116将刷新行地址rxadd供应到行解码器108,所述行解码器可刷新由刷新行地址rxadd指示的一或多个字线wl。

25.电源端子供应有电源电势vdd和vss。电源电势vdd和vss被供应到内部电压发生器电路124。内部电压发生器电路124基于供应到电源端子的电源电势vdd和vss产生各种内部电势vpp、vod、vary、vperi等。内部电势vpp主要用于行解码器108中,内部电势vod和vary主要用于包含于存储器阵列118中的感测放大器samp中,且内部电势vperi用于多数外围电路块中。

26.电源端子还供应有电源电势vddq和vssq。电源电势vddq和vssq被供应到输入/输出电路122。在本公开的实施例中,供应到电源端子的电源电势vddq和vssq可为与供应到所述电源端子的电源电势vdd和vss相同的电势。在本公开的另一实施例中,供应到电源端子的电源电势vddq和vssq可为与供应到所述电源端子的电源电势vdd和vss不同的电势。供应到电源端子的电源电势vddq和vssq用于输入/输出电路122,使得由输入/输出电路122产生的电源噪声不会传播到其它电路块。

27.存储器装置100的电压中的一或多个可作为输入耦合到随机数发生器126。随机数发生器126可使用一或多个电压来产生随机数rand。随机数rand可由存储器的各种其它电路使用。随机数发生器126可耦合到一或多个电压。在一些实施例中,随机数发生器126可从电压发生器124接收电压。在一些实施例中,随机数发生器126可耦合到从外部源提供到存储器的电压端子的电压(例如,vdd)。为了一致性和简洁,术语vdd将用于指代耦合到随机数发生器126的电压,然而,应理解,存储器的任何电压都可用作输入。

28.随机数发生器126可产生随时间改变的随机数rand。举例来说,随机数rand的值可基于可随着存储器执行各种操作改变的电压vdd的值。在一些实施例中,随机数发生器126可不断地(例如,尽可能快)更新随机数rand的值。在一些实施例中,随机数发生器126可定期更新随机数rand的值。在一些实施例中,随机数发生器126可由存储器的一或多个内部信号(例如,存取信号)触发以更新随机数rand的值。

29.在一些实施例中,可存在产生用于存储器的总随机数rand的单个随机数发生器126。在一些实施例中,可存在各自耦合到存储器的不同电压的多个随机数发生器。举例来说,随机数发生器126可在逐组基础上重复。每一随机数发生器126可耦合到与所述组相关联的电压,且可基于所述电压提供随机数。举例来说,每一随机数发生器可耦合到将电压(例如,vdd)分布到所述组的总线。

30.图2为根据本公开的一些实施例的到存储器的不同组的电压分布的框图。图2展示存储器组(例如,图1的存储器阵列118的那些存储器组)可耦合到系统电压(例如,vdd)的方

式的实例。应理解,图2出于解释的目的展示简化的示意性布局,且可以不同方式布置存储器的物理总线和存储器裸片。类似地,虽然图2中仅展示四个存储器组,但其它实例实施例中可使用其它数目个存储器组(例如,8个、16个、32个)。系统电压vdd可表示提供到存储器和/或由所述存储器产生的任何数目个不同电压。

31.沿着电压总线202将电压vdd提供到存储器组210、220、230和240。电压总线220可为存储器内的携载电压vdd的导电元件。本地总线212、222、232和242可将电压vdd从电压总线202分别耦合到组210、220、230和240中。由本地总线212、222、232和242携载的电压可用于分别为组210、220、230和240内的各种操作供电。由于组和本地总线可大体类似,因此为简洁起见,将仅详细描述第一组210和第一本地总线212。

32.本地总线212可为将电压vdd从电压总线202耦合到存储器组210中的导电元件。组210可包含沿着若干多个字线布置的多个存储器单元,此处编号为wl0到wln。作为存取操作的部分,字线可通过耦合到本地总线212而被激活。多个开关(未图示)可控制字线是否耦合到本地总线212,且开关可由响应于行地址的行控制器(例如,图1的108)控制。

33.当激活行时,其可表示相对大的电流汲取,因为字线可需要充电到电压vdd。因此,当字线被激活时,沿着本地总线212以及电压总线202的电压中可存在改变或

‘

下降’。举例来说,在字线被激活之后的时刻中,从激活字线牵引的电流可使电压在本地总线212和电压总线202上下降。当各种驱动器将总线恢复到vdd时,电压接着可返回到vdd。此外,电压的下降量以及下降的持续时间可以取决于哪个字线被激活。举例来说,如图2中所布置,字线wl0可比字线wln更接近电压总线202。因此,沿着本地总线212在电压总线202与字线wl0之间以及在电压总线202与字线wln之间可存在不同电阻。以类似方式,不同组中的相同字线(例如,组210中的wl1和组230中的wl1)可导致电压总线202的电压中下降的量和持续时间不同。

34.由于随时间推移存取不同组中的不同字线,因此电压总线202上的电压可变化。由于变化的量和持续时间可取决于所存取的字线,因此电压总线202的电压可以难以确定的方式变化。此外,制造公差可意味着即使两个不同的存储器芯片具有对其执行的相同存取模式,其相应电压总线中的电压下降也可不同。因此,沿着电压总线的电压可包含随机性和不可预测性的元件,所述元件可用于产生随机数。

35.图3为根据本公开的实施例的随机数发生器的框图。在一些实施例中,随机数发生器300可包含于一些实施例中的图1的随机数发生器126中。随机数发生器300接收电压vdd,且基于电压vdd提供随机数rand。在一些实施例中,例如组合逻辑304、序列发生器306和/或时序逻辑308的任选组件进一步增加随机数rand的随机性和/或增加电压vdd与随机数rand之间的关系的复杂性。值rng_vdd可存储于锁存器307中,且可用作随机数rand,直到随机数发生器300可产生随机数的新值(例如,rng_vdd_new)且将其存储在锁存器307中为止。

36.随机数发生器300的各种任选组件以虚线示出。这些任选组件的任何组合可用于随机数发生器300中。

37.随机数发生器300包含模/数转换器(adc)302。adc 302可将电压vdd的模拟值转换成数字编号rng_vdd_new。值rng_vdd_new可保存于锁存器307中作为值rng_vdd。如本文中更详细地论述,各种方法可用于确定何时激活时序信号newrand,其可使锁存器307捕获rng_vdd_new的当前值作为rng_vdd的新值。由于电压vdd的波动,数字值rng_vdd可为随机

数。在一些实施例中,adc 302可基于vdd的值的预期波动而集中于电压vdd的值的特定范围。举例来说,rng_vdd的最大值可以其完整指定值与值vdd相关联,且rng_vdd的最小值在下降期间与vdd的预期最低值相关联。数字值rng_vdd可为n位二进制数。举例来说,在一些实施例中,数字值rng_vdd可为6位二进制数。其它数目的位(例如,4位、8位、10位等)可用于其它实例实施例中。

38.在一些实施例中,可选择adc 302,使得其在将模拟电压vdd转换成数字值rng_vdd时具有相对较低的精确度。举例来说,adc 302可具有较大公差,使得vdd的给定值可在第一时间产生第一值rng_vdd且在第二时间产生第二值rng_vdd。这可减少随机数发生器300的可预测性,其可增加数字值rng_vdd的随机性。

39.在一些实施例中,数字值rng_vdd可直接用作随机数rand(例如,可省略组合逻辑304和序列发生器306)。在一些实施例中,可修改数字值rng_vdd以产生随机数rand,这可进一步增加随机数rand的随机性和/或不可预测性。

40.在一些实施例中,组合逻辑304可用于将数字值rng_vdd与另一数字组合。举例来说,可使用存储器的唯一标识符值,例如熔断id(fid)。组合逻辑304可将数字值rng_vdd与fid组合以产生值seed。举例来说,组合逻辑304可使用一或多个异或(xor)逻辑门以将fid的位与数字值rng_vdd的位组合以产生seed的值。在一些实施例中,值seed可用作随机数rand(例如,可省略序列发生器306)。

41.在一些实施例中,序列发生器306可用于基于seed的值产生随机数rand。举例来说,序列发生器306可包含线性反馈移位寄存器(lfsr),所述线性反馈移位寄存器可基于输入种子值(例如,值seed)产生数字。实例序列发生器306可包含散列电路,所述散列电路可将seed的n位值映射到随机数rand的m位值上。在一些实施例中,组合逻辑304可省略,且值rng_vdd可直接用作序列发生器306的种子值。

42.在一些实施例中,随机数发生器300可不断地(例如,与电路可操作的一样快)更新随机数rand的值。在一些实施例中,随机数发生器300可省略锁存器307,且可由adc302直接提供值rng_vdd作为随机数rand。

43.在一些实施例中,序列发生器300可包含时序逻辑电路308,所述时序逻辑电路可控制何时提供随机数rand的新值。举例来说,时序逻辑308可提供耦合到锁存器307的时钟端子的激活信号newrand。当时序逻辑在有效电平下提供信号newrand时,adc rng_vdd_new的电流输出可捕获于锁存器307中且提供为值rng_vdd(例如,覆写rng_vdd的先前值)。

44.在一些实例实施例中,时序逻辑308可将随机数的先前值(例如,rng_vdd)与随机数的当前值(例如,rng_vdd_new)进行比较以确定何时更新随机数的值(例如,何时在有效电平下提供信号newrand)。举例来说,时序逻辑308可定期将当前随机数rng_vdd_new与所存储的随机数rng_vdd进行比较。若值不同,则时序逻辑308可更新计数器。当计数器达到阈值(例如,3、6、9等)时,可在有效电平下提供信号newrand,且可重置计数器。

45.在一些实施例中,时序逻辑308可使用其它方法(替代地或另外)确定何时在有效电平下提供信号newrand。举例来说,时序逻辑308可耦合到时钟信号(或可包含振荡器且产生其自身的时钟信号),且可定期提供信号newrand。实例时序逻辑308可耦合到存储器的信号(例如,字线激活信号),且可响应于那些信号而提供信号newrand。可在其它实施例中使用控制时序的其它方法。

46.图4为根据本公开的一些实施例的随机数发生器的不同组织的框图。图4展示多个随机数发生器,其每一者可包含相对于图3的随机数发生器300所论述的特征和组件中的一或多个。

47.随机数发生器402、404和406中的每一个可与存储器的不同组相关联。举例来说,第一随机数发生器402可与第一组(例如,图2的210)相关联,第二随机数发生器404可与第二组(例如,图2的220)相关联等。随机数发生器402-406中的每一个可耦合到与所述组相关联的电压。举例来说,第一随机数发生器402可耦合到第一电压bank0_vdd。第一电压bank0_vdd可表示沿着局部电压总线(例如,图2的212)的电压。

48.因此,随机数发生器402-406中的每一个可分别提供随机数rand_bank0到rand_bankn,所述随机数与相应组相关联。每一组级随机数可由组特定电路使用。举例来说,第一组随机数rand_bank0可用于将随机性注入到刷新控制电路(例如,图1的116)的操作中。

49.在一些实施例中,可组合组级随机数rand_bank0到rand_bankn中的一或多个以产生总随机数rand。存储器可包含可将组级随机数组合为总随机数rand的任选的总随机数发生器408。在一些实施例中,总随机数发生器408可将随机数例如与一或多个xor门组合。在一些实施例中,总随机数发生器408可包含随机性的其它来源(例如,lfsr)且可使用组合的组级随机数作为种子。

50.在一些实施例中,组级随机数发生器402到406中的不同者可在不同时间激活。举例来说,随机数发生器402和404可为活动的(例如,分别提供rand_bank0和rand_bank1的值),而组级rng 406为非活动的(例如,未提供信号rand_bankn)。在一些实施例中,可基于哪些组是活动的(例如,组地址badd)而激活随机数发生器402-406。

51.在一些实施例中,组可一起分组到组群中,且所述群组可用于确定何时更新与组相关联的随机数。举例来说,当组群中的组中的任一个接收存取命令(例如,如由组地址badd指示)时,那么与所述组群的组相关联的所有随机数发生器可更新其随机数。

52.图5为根据本公开的实施例的刷新控制电路的框图。在一些实施例中,刷新控制电路516可包含在图1的刷新控制电路116中。展示刷新控制电路516的某些内部组件和信号以说明刷新控制电路516的操作。展示虚线518以表示在某些实施例中,组件(例如刷新控制电路516和行解码器508)中的每一个可对应于特定的存储器组,且可针对存储器组中的每一个重复这些组件。因此,可存在多个刷新控制电路516、随机数发生器540和行解码器508。出于简洁起见,将仅描述用于单个组的组件。

53.dram接口526可将一或多个信号提供到地址刷新控制电路516和行解码器508。刷新控制电路516可包含取样时序电路530、侵略者检测器电路232、行锤击刷新(rhr)状态控制电路536和刷新地址发生器534。dram接口526可提供一或多个控制信号,例如刷新信号aref、激活和预充电信号act/pre和行地址xadd。当与刷新控制电路516相关联的组处于刷新模式时,刷新控制电路516基于刷新信号aref提供具有时序的刷新地址rxadd。

54.dram接口526还可将电压vdd提供到随机数发生器540,所述随机数发生器又可基于电压vdd提供随机数rand。随机数发生器540可为组级电路(例如,对于每一组重复)或可为提供单个随机数rand到存储器的每一刷新控制电路516的总随机数发生器。在一些实施例中,随机数发生器540可包含于图1的随机数发生器126、图3的随机数发生器300和/或图4的随机数发生器402-408中。随机数rand可由刷新控制电路516的一或多个组件使用。

55.图5的实例实施例中展示特定配置,其中随机数rand由取样时序电路530和侵略者检测器电路532使用。然而,在其它实施例中,随机数rand可由取样时序电路530和侵略者检测器电路532中的一个或另一个使用。在一些实施例中,取样时序电路530可使用第一随机数,且第二随机数可用于侵略者检测器电路532。在一些实施例中,刷新控制电路516的其它组件可使用随机数rand。

56.侵略者检测器电路532可响应于由取样时序电路530提供的取样信号armsample的激活而对当前行地址xadd进行取样。侵略者检测器电路532可耦合到沿着行地址总线所发送的所有行地址xadd,但仅在存在取样信号armsample的激活时可接收(例如处理、注意)行地址xadd的当前值。在其它实例实施例中,可不使用取样。

57.接收到的行地址(所取样的地址或所有地址)可存储于侵略者电路532中和/或与先前所存储的地址相比较。侵略者检测器电路532可基于当前行地址xadd和/或先前行地址提供匹配地址hitxadd。rhr状态控制电路536可提供信号rhr以指示应发生行锤击刷新(例如,与所标识的侵略者行相对应的受害者行的刷新)。rhr状态控制电路536还可提供内部刷新信号iref,以指示应发生自动刷新。

58.响应于rhr或iref的激活,刷新地址发生器534可提供刷新地址rxadd,所述刷新地址可为自动刷新地址或可为对应于侵略者行的受害者行的一或多个受害者地址,所述侵略者行对应于匹配地址hitxadd。rhr状态控制电路536可响应于刷新信号aref而提供rhr和iref的激活的集合。行解码器508可响应于刷新地址rxadd和行锤击刷新信号rhr而执行刷新操作。行解码器508可基于刷新地址rxadd和内部刷新信号iref而执行自动刷新操作。

59.dram接口526可表示向组的组件提供信号的一或多个组件。在一些实施例中,dram接口526可表示耦合到半导体存储器装置(例如,图1的装置100)的存储器控制器。在一些实施例中,dram接口526可表示例如图1的命令地址输入电路102、地址解码器104和/或命令解码器106的组件。dram接口526可提供行地址xadd、刷新信号aref、电压vdd以及例如激活信号act和预充电信号pre的存取信号。尽管图2中未展示,但dram接口526还可提供组地址badd,所述组地址可指示所存取的行地址xadd位于何处。组地址badd可激活与由组地址badd指示的组相关联的特定刷新控制电路516。dram接口还可通过提供刷新信号aref的激活而使刷新控制电路处于刷新模式中。刷新信号aref可为在刷新模式期间提供的周期信号,所述周期信号可指示刷新操作的时序。通常可将存取信号act和pre作为存取操作的部分连同行地址xadd一起提供。可提供激活信号act以激活存储器的给定组。可提供预充电信号pre以对存储器的给定组进行预充电。行地址xadd可为包含多个位的信号(其可串行或并行地传输)且可对应于激活的存储器组的特定行。

60.在图2的实例实施例中,刷新控制电路516利用取样以监视沿着行地址总线提供的行地址xadd的一部分。因此,代替响应于每一行地址,刷新控制电路516可对行地址总线上的行地址xadd的当前值进行取样,且可基于所取样的行地址而确定哪些地址是侵略者。刷新控制电路516的取样的时序可受提供取样信号armsample的取样时序电路530控制。取样时序电路530可提供取样信号armsample的激活,且信号armsample的每一激活可指示应对行地址的当前值进行取样。armsample的激活可以是

‘

脉冲’,其中armsample升高到高逻辑电平且接着返回到低逻辑电平。

61.信号armsample的激活可以具备周期性时序、随机时序、半随机时序、伪随机时序

或其组合。取样时序电路530提供信号armsample的时序可基于随机数rand。举例来说,振荡器可增加计数器,且当计数器匹配随机数rand的值时,可提供信号armsample。在提供信号armsample之后,取样时序电路530可触发rng 540以提供随机数rand的新值。在其它实施例中,可不使用取样,且侵略者检测器电路532可沿着行地址总线接收行地址xadd的每一值。在此类实施例中,可省略取样时序电路530和取样信号armsample。

62.侵略者检测器电路532可从dram接口526接收行地址xadd,并从取样时序电路530接收信号armsample。当dram接口526将存取操作(例如,读取和写入操作)引导到存储器单元阵列(例如,图1的存储器单元阵列118)的不同行时,行地址总线上的行地址xadd可改变。每当侵略者检测器电路532接收信号armsample的激活(例如,脉冲)时,侵略者检测器电路532可对xadd的当前值进行取样。

63.侵略者检测器电路532可基于所取样的行地址中的一或多个确定侵略者地址,且接着可提供所确定的侵略者地址作为匹配地址hitxadd。侵略者检测器电路532可包含数据存储单元(例如多个寄存器),所述数据存储单元可用于存储所取样的行地址。在一些实例实施例中,当侵略者检测器电路532(例如,响应于armsample的激活)对行地址xadd的新值进行取样时,所述侵略者检测器电路可将所取样的行地址与存储于数据存储单元中的地址进行比较。若所取样的地址与所存储的地址中的一个之间存在匹配,则侵略者检测器电路532可提供匹配信号match。在一些实例实施例中,匹配地址hitxadd可为存储于侵略者检测器电路532中的地址中的一个,所述地址与所取样的地址xadd最频繁地匹配。举例来说,侵略者检测器电路532可对接收每一地址xadd的次数进行计数,且将已接收到最多次的地址提供为匹配地址hitxadd。

64.在一些实施例中,侵略者检测器电路532可对接收地址的次数进行计数,且当地址的计数超出阈值时将所述地址标记为匹配地址hitxadd。在一些实施例中,阈值可基于随机数rand而变化。在一些实施例中,计数值可基于随机数rand而变化。

65.存储器装置可执行一连串自动刷新操作,以便定期刷新存储器装置的行作为刷新模式的部分。rhr状态控制电路536可确定给定刷新操作是自动刷新操作还是目标刷新操作。可产生rhr信号,以便指示装置应刷新特定目标行(例如,受害者行)而非来自自动刷新地址序列的地址。rhr状态控制电路536还可提供内部刷新信号iref,所述内部刷新信号可指示应发生自动刷新操作。在一些实施例中,可产生信号rhr和iref,使得其不同时活动(例如,两者不同时处于高逻辑电平下)。在一些实施例中,可针对每一刷新操作激活iref,且除非rhr也活动,否则可执行自动刷新操作,在rhr也活动的情况下,改为执行目标刷新操作。rhr状态控制电路可响应于刷新信号aref的一或多个激活而执行一连串自动刷新操作和目标刷新操作。

66.在一些实施例中,刷新控制电路516可响应于刷新信号aref的每一激活而执行多个刷新操作。举例来说,每当接收到刷新信号aref时,刷新控制电路516可通过提供k个不同的刷新地址rxadd来执行k个不同的刷新操作。每一刷新操作都可被称为

‘

泵’。k个不同刷新操作中的每一个可为自动刷新操作或目标刷新操作。在一些实施例中,响应于刷新信号aref的激活,每一组泵中的目标和自动刷新操作的数目可为恒定的。在一些实施例中,所述数目可变化。

67.刷新地址发生器534可接收行锤击刷新信号rhr和匹配地址hitxadd。匹配地址

hitxadd可表示侵略者行。刷新地址发生器534可基于匹配地址hitxadd确定一或多个受害者行的位置,且当信号rhr指示目标刷新操作时将所述匹配地址提供为刷新地址rxadd。在一些实施例中,受害者行可包含物理上邻近于侵害者行的行(例如,hitxadd 1和hitxadd-1)。在一些实施例中,受害者行还可包含物理上邻近于侵害者行的物理上相邻行的行(例如,hitxadd 2和hitxadd-2)。受害者行与所标识的侵略者行之间的其它关系可用于其它实例中。举例来说,还可刷新 /-3、 /-4和/或其它行。

68.刷新地址发生器534可基于行锤击刷新信号rhr确定刷新地址rxadd的值。在一些实施例中,当信号rhr不活动时,刷新地址发生器534可提供一连串自动刷新地址中的一个。当信号rhr活动时,刷新地址发生器534可提供例如受害者地址的目标刷新地址作为刷新地址rxadd。在一些实施例中,刷新地址发生器534可对信号rhr的激活进行计数,且相比更远离侵略者地址的受害者行(例如,hitxadd /-2)可更频繁地提供更接近的受害者行(例如,hitxadd /-1)。

69.行解码器508可基于接收到的信号和地址对存储器阵列(未图示)执行一或多个操作。举例来说,响应于激活信号act和行地址xadd(和处于低逻辑电平的iref和rhr),行解码器508可指导对指定行地址xadd进行一或多个存取操作(例如,读取操作)。响应于iref和/或rhr信号活动,行解码器508可刷新刷新地址rxadd。

70.图6为根据本公开的一些实施例的基于存储器的电压产生随机数的方法的框图。在一些实施例中,方法600可由图1-5中表示的设备和组件中的一或多个执行。

71.方法600可通常开始于框610,其描述将电压提供到存储器阵列。存储器阵列可接收可用于为存储器的各种操作供电的系统电压(例如,vdd)。电压可沿着电压总线(例如,图2的202)分布。电压可沿着各种组级总线(例如,图2的212、222、232和242)分布到存储器组。在一些实施例中,沿着组级总线的电压可用作电压。

72.框620可通常跟在框610后,所述框620描述对存储器阵列执行存取操作。执行存取操作可改变电压。举例来说,存取操作可涉及通过将存储器阵列的一或多个字线耦合到电压而激活字线。这可表示相对较大的电压汲取,这可引起电压下降。下降的值和持续时间可部分地基于存储器的哪些字线被激活作为存取操作的部分。

73.框630可通常跟在框620后,所述框630描述基于电压产生随机数。由于电压可随时间变化(例如,利用各种存取操作),因此随机数可具有相对较高的随机性和/或不可预测性。产生随机数可包含使用模/数转换器(adc)基于电压产生二进制数。在一些实施例中,二进制数可与额外值(例如,熔断标识号)组合以产生组合值,且随机数可基于所述组合值。在一些实施例中,二进制数可被序列发生器用作种子以产生随机数。在一些实施例中,二进制数可用作随机数。

74.当然,应了解,本文中所描述的实例、实施例或过程中的任一个可与一或多个其它实例、实施例和/或过程组合或分离和/或在根据本发明系统、装置和方法的单独装置或装置部分中执行。

75.最后,上文的论述意图仅说明本发明系统且不应被理解为将所附权利要求书限制于任何特定实施例或实施例的群组。因此,虽然已参考示例性实施例详细地描述了本发明系统,但还应了解,在不脱离如在所附权利要求书中所阐述的本发明系统的更广和既定精神和范围的情况下所属领域的技术人员可设计许多修改和替代性实施例。因此,说明书和

附图应以说明性方式看待,且并不意图限制所附权利要求书的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。