技术特征:

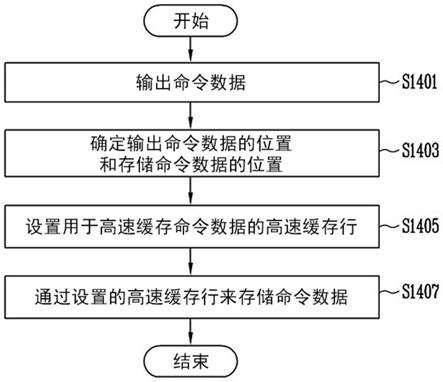

1.一种存储器控制器,包括:存储器缓冲器,存储与从主机接收的请求相对应的命令数据;以及高速缓存存储器,高速缓存所述命令数据,其中所述高速缓存存储器通过基于输出所述命令数据的组件和所述命令数据中包括的标志分配高速缓存行来存储所述命令数据。2.根据权利要求1所述的存储器控制器,进一步包括:中央处理器,生成与所述请求相对应的命令并输出与命令相对应的命令数据;以及直接存储器访问控制器即dma控制器,与存储器装置通信,使得所述存储器装置在没有所述中央处理器的干预的情况下执行与所述请求相对应的操作。3.根据权利要求2所述的存储器控制器,其中当从所述中央处理器输出所述命令数据时,所述高速缓存存储器在不分配所述高速缓存行的情况下高速缓存所述命令数据。4.根据权利要求2所述的存储器控制器,其中当从所述dma控制器输出所述命令数据时,所述高速缓存存储器基于所述命令数据中包括的所述标志来分配所述高速缓存行。5.根据权利要求1所述的存储器控制器,其中所述标志包括关于所述存储器缓冲器中存储所述命令数据的存储区域的起始地址和结束地址的信息。6.根据权利要求5所述的存储器控制器,其中所述高速缓存存储器基于所述起始地址和所述结束地址来确定所述命令数据的大小。7.根据权利要求6所述的存储器控制器,其中当所述起始地址是所述存储器缓冲器的参考地址中的任意一个时,所述高速缓存存储器将所述命令数据从所述起始地址开始划分为多个划分的命令数据,每个划分的命令数据的大小对应于参考高速缓存行的大小。8.根据权利要求6所述的存储器控制器,其中当所述起始地址是除了所述存储器缓冲器的参考地址之外的地址时,所述高速缓存存储器生成并输出与所述起始地址和所述起始地址之后的参考地址之间的第一间隔相对应的第一划分的命令数据,所述第一划分的命令数据是所述命令数据的第一部分。9.根据权利要求8所述的存储器控制器,其中所述高速缓存存储器以与参考高速缓存行的大小相对应的单位,对应于所述起始地址之后的参考地址和所述结束地址之间的间隔对所述命令数据的第二部分进行划分,所述参考高速缓存行具有预定大小。10.根据权利要求8所述的存储器控制器,其中所述高速缓存存储器高速缓存与所述结束地址之前的参考地址和所述结束地址之间的第二间隔相对应的第二划分的命令数据。11.一种操作存储器控制器的方法,所述存储器控制器包括存储器缓冲器和高速缓存存储器,所述方法包括:将与从主机接收的请求相对应的命令数据存储在所述存储器缓冲器中;并且将所述命令数据高速缓存在所述高速缓存存储器中,其中所述高速缓存包括:基于输出所述命令数据的组件和所述命令数据中包括的标志来分配高速缓存行。12.根据权利要求11所述的方法,其中当所述存储器控制器进一步包括中央处理器和直接存储器访问控制器即dma控制器时,所述中央处理器生成与所述请求相对应的命令并输出与所述命令相对应的命令数据,所述dma控制器与存储器装置通信,使得所述存储器装置在没有所述中央处理器的干预的情况下执行与所述请求相对应的操作,

所述高速缓存进一步包括确定输出所述命令数据的组件是所述中央处理器还是所述dma控制器。13.根据权利要求12所述的方法,其中所述高速缓存包括:当从所述中央处理器输出所述命令数据时,在不分配所述高速缓存行的情况下高速缓存所述命令数据。14.根据权利要求12所述的方法,其中所述高速缓存包括:当从所述dma控制器输出所述命令数据时,通过基于所述命令数据中包括的所述标志分配所述高速缓存行来高速缓存所述命令数据。15.根据权利要求11所述的方法,其中所述标志包括关于所述存储器缓冲器中存储所述命令数据的存储区域的起始地址和结束地址的信息。16.根据权利要求15所述的方法,其中分配所述高速缓存行包括:基于所述起始地址和所述结束地址来确定所述命令数据的大小。17.根据权利要求16所述的方法,其中在分配所述高速缓存行时,当所述起始地址是所述存储器缓冲器的参考地址中的任意一个时,将所述命令数据从所述起始地址开始划分为多个划分的命令数据,每个划分的命令数据的大小对应于参考高速缓存行的大小,所述参考高速缓存行具有预定大小。18.根据权利要求16所述的方法,其中在分配所述高速缓存行时,当所述起始地址是除了所述存储器缓冲器的参考地址之外的地址时,生成并输出与所述起始地址和所述起始地址之后的参考地址之间的第一间隔相对应的第一划分的命令数据,所述第一划分的命令数据是所述命令数据的第一部分。19.根据权利要求18所述的方法,其中在分配所述高速缓存行时,以与参考高速缓存行的大小相对应的单位,对应于所述起始地址之后的参考地址和所述结束地址之间的间隔对所述命令数据的第二部分进行划分,所述参考高速缓存行具有预定大小。20.根据权利要求18所述的方法,其中在分配所述高速缓存行时,高速缓存与所述结束地址之前的参考地址和所述结束地址之间的第二间隔相对应的第二划分的命令数据。

技术总结

本技术涉及一种电子装置。一种增加高速缓存存储器的命中率的存储器控制器包括被配置为存储与从主机接收的请求相对应的命令数据的存储器缓冲器,以及被配置为高速缓存命令数据的高速缓存存储器。高速缓存存储器通过基于输出命令数据的组件和命令数据中包括的标志分配高速缓存行来存储命令数据。分配高速缓存行来存储命令数据。分配高速缓存行来存储命令数据。

技术研发人员:金到训

受保护的技术使用者:爱思开海力士有限公司

技术研发日:2021.04.12

技术公布日:2022/2/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。