时钟监测电路

1.相关申请的交叉引用

2.本技术要求于2020年8月19日提交的申请号为10-2020-0103792的韩国专利申请的优先权,该韩国专利申请通过引用整体并入本文。

技术领域

3.实施例涉及一种半导体设计技术,并且更特别地,涉及一种用于半导体装置中的时钟(clock)监测电路。

背景技术:

4.随着vlsi工艺技术的改善,半导体电路受到进程、电压和温度(pvt)变化的更大影响。

5.特别地,例如环形振荡器的在半导体装置内用于生成时钟的时钟生成电路可能受到这种pvt变化的显著影响。即,为了生成设置为特定目标频率的时钟,半导体装置中包括的环形振荡器可以根据pvt变化而生成与特定目标频率具有明显频率差异的时钟。

6.因此,常规地,存在一种直接对由环形振荡器生成的时钟的触发计数进行计数并且检查时钟的生成频率与特定目标频率之间是否存在差异以及存在多大差异的方法。

7.由于半导体装置的尺寸减小并且半导体装置的操作速度增加,因此如果增大半导体装置内使用的时钟的频率,例如,如果时钟的频率变为千兆赫(ghz)或更大,则可能难以使用现有方法。即,可能难以使用直接对由环形振荡器生成的时钟的触发计数进行计数的方法。

8.因此,常规地,使用一种用时钟分频电路以预定比率将由环形振荡器生成的时钟进行分频并且对分频后的时钟进行计数的方法。然而,与直接对由环形振荡器生成的时钟进行计数的方法相比,对分频后的时钟进行计数的方法可能在测量中具有许多误差。

技术实现要素:

9.各个实施例涉及一种能够精确地对由环形振荡器生成的具有高频率的时钟的触发计数进行计数的监测电路。

10.在实施例中,一种监测电路可以包括:时钟生成器,适于生成具有第一目标频率的第一时钟,该第一目标频率根据进程、电压和温度(pvt)变化而不同于目标频率;代码生成器,适于响应于输入时钟而通过改变输入代码的值来生成输出代码,接收与输出代码相关联的反馈信号,并且通过在第一模式下执行一个或多个设置操作并在第二模式下执行一个或多个逆设置操作来改变输入代码的值;以及操作控制器,适于控制代码生成器在测试区段中进入第一模式,在代码生成器进入第一模式的第一时间将第一时钟和起始代码分别作为输入时钟和输入代码传输到代码生成器,在代码生成器退出第一模式的第二时间将输出代码设置为计数代码,控制代码生成器在检查区段中进入第二模式,在代码生成器进入第二模式的第三时间将第二时钟和计数代码分别作为输入时钟和输入代码传输到代码生成

器,并且对在第二模式下的第二时钟的触发数量进行计数,直到输出代码具有与起始代码的值相同的值,以生成监测信息。操作控制器可以从监测电路的外部接收具有比第一目标频率更低的第二目标频率的第二时钟。

11.操作控制器:可以控制代码生成器在测试区段中在第一时间进入第一模式;并且可以控制代码生成器在第二时间退出第一模式,第一时间和第二时间之间的第一时间间隔是预先确定的。

12.操作控制器:可以控制代码生成器在检查区段中在第三时间进入第二模式;并且可以响应于所生成的监测信息而控制代码生成器在第四时间退出第二模式。

13.操作控制器可以响应于外部输入的控制信号而开始或终止测试区段或者检查区段或者测试区段和检查区段两者。

14.在第二模式下的第二时钟的触发数量可以是第一触发数量。操作控制器:在测试区段已经开始之后,可以控制代码生成器在第一时钟的边沿(edge)与第二时钟的边沿同步的第一时间进入第一模式;并且可以控制代码生成器在从第一时间起第二时钟的第二触发数量达到给定数量的第二时间退出第一模式。

15.操作控制器:在检查区段的操作已经开始之后,可以控制代码生成器在第二时钟的边沿同步的第三时间进入第二模式;并且在已经生成监测信息之后,可以控制代码生成器在第二时钟的边沿同步的第四时间退出第二模式。

16.时钟生成器可以响应于从操作控制器接收的使能信号而生成第一时钟。

17.操作控制器:可以响应于控制信号,通过激活使能信号,控制时钟生成器生成第一时钟;并且当代码生成器退出第一模式时,可以通过停用使能信号,控制时钟生成器停止生成第一时钟。

18.操作控制器可以包括:信号生成器,适于响应于控制信号以及第一时钟和第二时钟而生成使能信号和模式选择信号;时钟选择器,适于响应于模式选择信号而在第一模式的第一时间间隔期间选择第一时钟,在第一时间间隔期间将所选择的第一时钟传输到代码生成器,在第二模式的第二时间间隔期间选择第二时钟,并且在第二时间间隔期间将所选择的第二时钟传输到代码生成器,第二时间间隔在第三时间和第四时间之间;代码比较器,适于当响应于模式选择信号而在第二时间间隔期间触发第二时钟时,比较输出代码的值和起始代码的值;代码存储装置,适于在代码生成器退出第一模式的第二时间将输出代码作为计数代码存储,并且在代码生成器进入第二模式的第三时间将所存储的计数代码传输到代码生成器;以及计数器,适于响应于模式选择信号而在第二模式的第二时间间隔期间对第二时钟的第一触发数量进行计数,并且响应于代码比较器的输出信号而生成监测信息。

19.代码比较器:可以存储起始代码;可以在代码生成器进入第一模式的第一时间将所存储的起始代码传输到代码生成器,第一时间响应于模式选择信号而确定;并且当在第二模式的第二时间间隔期间触发第二时钟时,可以比较输出代码的值和所存储的起始代码的值。

20.代码存储装置:可以存储起始代码;可以在代码生成器进入第一模式的第一时间将所存储的起始代码传输到代码生成器,第一时间响应于模式选择信号而确定;并且在第二模式的第二时间间隔期间,可以将所存储的起始代码传输到代码比较器。

21.信号生成器可以包括:内部信号生成器,适于响应于控制信号而生成内部使能信

号和模式选择信号;第一同步器,适于将内部使能信号与第二时钟的边沿同步,并且将同步后的内部使能信号作为使能信号传输到时钟生成器;以及第二同步器,适于检测从时钟生成器接收的第一时钟的边沿与第二时钟的边沿同步的时间。

22.时钟选择器可以包括:多工器(multiplexer),适于响应于模式选择信号而选择第一时钟和第二时钟中的一个;以及时钟传输器,适于响应于第二同步器的输出信号,将所选择的时钟传输到代码生成器。

23.在实施例中,一种控制监测电路的方法,该方法可以包括:在代码生成器进入第一模式的第一时间,将第一时钟作为输入时钟并且将起始代码作为输入代码提供到代码生成器;通过在第一模式下执行一个或多个设置操作,改变输入代码的值以生成输出代码;在代码生成器退出第一模式的第二时间将输出代码设置为计数代码;在代码生成器进入第二模式的第三时间,提供第二时钟作为输入时钟并且提供计数代码作为输入代码,第二时钟具有比第一时钟的频率更低的频率;通过在第二模式下执行一个或多个逆设置操作,改变输入代码的值以生成输出代码;并且对在第二模式下的第二时钟的触发数量进行计数,直到输出代码的值变得等于起始代码的值,以生成监测信息。

24.该方法可以进一步包括:控制代码生成器在第一时间进入第一模式;并且控制代码生成器在第二时间退出第一模式,第一时间和第二时间之间的第一时间间隔是预先确定的。

25.该方法可以进一步包括:控制代码生成器在第三时间进入第二模式;并且响应于所生成的监测信息而控制代码生成器在第四时间退出第二模式。

26.当在第一模式下触发第一时钟时,代码生成器可以执行设置操作,并且当在第二模式下触发第二时钟时,代码生成器可以执行逆设置操作。

27.代码生成器可以包括:多个寄存器,生成输出代码;以及逻辑门,接收输出代码的多个位,并且对所接收的输出代码的位执行逻辑运算,以向多个寄存器中的一个提供指示逻辑运算结果的信号。

28.根据本实施例,半导体装置中包括的环形振荡器所生成的具有相对较高频率的时钟与起始代码一起被输入到线性反馈移位寄存器(lfsr)。lfsr可以执行与高速触发操作相对应的设置操作,并且作为设置操作的结果而生成计数代码。此后,lfsr接收具有相对较低频率的外部输入时钟以及计数代码,并且执行与低速触发操作相对应的设置操作的逆操作。因此,可以以低速对在起始代码和计数代码之间所需的时钟的触发计数进行计数。

29.因此,具有可以精确地对由环形振荡器生成的具有高频率的时钟的触发计数进行计数的效果。

附图说明

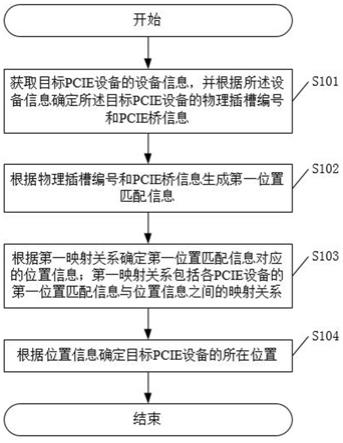

30.图1示出根据实施例的监测电路的操作。

31.图2a示出根据实施例的监测电路中包括的操作控制器。

32.图2b示出根据另一实施例的监测电路中包括的操作控制器。

33.图3示出根据实施例的图2a或图2b的操作控制器中包括的信号生成器和时钟选择器。

34.图4a、图4b和图4c是示出以描述根据实施例的监测电路中包括的代码生成器的示

图。

35.图5是示出根据实施例的适于用作图1的监测电路中包括的时钟生成器的时钟生成器的示图。

具体实施方式

36.下面参照附图更详细地描述本公开的各个示例。然而,本技术的方面和特征可以以不同方式实现,以形成包括任意所公开的实施例的变型的其它实施例。因此,所公开的技术将不被解释为限于本文所阐述的实施例。相反,提供所描述的实施例,使得本公开是彻底且完整的,并且将本公开充分传达给本技术所属领域的技术人员。在整个公开中,相同的附图标记在本公开的各个附图和示例中指代相同的部件。注意的是,对“实施例”、“另一实施例”等的参考不一定意为单个实施例,并且对任何这种短语的不同参考不一定针对相同的(多个)实施例。

37.将理解的是,尽管本文可能使用术语“第一”、“第二”、“第三”等来识别各个元件,但是这些元件不受这些术语的限制。这些术语用于将一个元件与另一元件区分开,否则一个元件与另一元件具有相同或相似的名称。因此,在不脱离本技术的精神和范围的情况下,在一个实例中的第一元件可以在另一实例中被称为第二元件或第三元件。

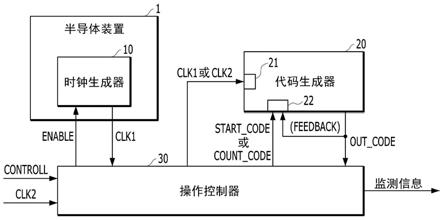

38.附图不一定按比例绘制,并且在某些实例中,为了清楚地示出实施例的特征,比例可能已被放大。当元件被称为连接或联接至另一元件时,应理解的是,前者可以直接连接或联接至后者,或者经由其间的一个或多个中间元件而电连接或联接至后者。另外,还将理解的是,当元件被称为在两个元件“之间”时,该元件可以是这两个元件之间的单个元件,或者也可以存在一个或多个中间元件。

39.本文使用的术语仅用于描述特定实施例的目的,而非旨在限制所公开的技术。如本文所使用的,除非上下文另外明确指出,否则单数形式旨在包括复数形式,反之亦然。类似地,除非从语言或上下文中明确地指示仅一个,否则不定冠词“一”和“一个”意为一个或多个。

40.将进一步理解的是,当在说明书中使用时,术语“包括”、“包括有”、“包含”和“包含有”指明存在所陈述元件并且不排除存在或添加一个或多个其它元件。如本文所使用的,术语“和/或”包括一个或多个相关所列项目的任意组合。

41.除非另有定义,否则本文所使用的包括技术术语和科学术语的所有术语具有与本技术所属领域的技术人员鉴于本公开而通常理解的含义相同的含义。将进一步理解的是,除非在本文中明确定义,否则诸如在常用词典中所定义的那些术语的术语应被解释为具有与在本公开和相关领域的语境中的含义一致的含义,并且不应以理想化或过于形式化的意义来解释。

42.在下面的描述中,阐述了许多具体细节,以便提供对本技术的透彻理解。可以在没有一些或所有这些具体细节的情况下实践本技术。在其它实例中,为了避免不必要地模糊本技术,没有详细描述公知的进程结构和/或进程。

43.还要注意的是,在一些实例中,除非另外特别指出,否则如对相关领域的技术人员而言显而易见的,结合一个实施例描述的特征或元件可以单独使用,或者与另一实施例的其它特征或元件组合使用。

44.下面参照附图详细地描述本公开的实施例,其中相同的附图标记指代相同的元件。

45.图1是示出根据实施例的监测电路的操作的示图。

46.图5是示出根据实施例的适于用作图1的监测电路中包括的时钟生成器10的时钟生成器的示图。

47.首先,参照图1,根据实施例的监测电路可以包括半导体装置1、代码生成器20和操作控制器30,该半导体装置1包括时钟生成器10。

48.半导体装置1中包括的时钟生成器10可以是被设计用于生成具有目标频率的目标时钟的元件。在这种情况下,时钟生成器10可以根据进程、电压和温度(pvt)变化来生成具有与目标频率不同的频率的第一时钟clk1。即,时钟生成器10具有响应于使能信号enable而生成具有目标频率的目标时钟的目的,但是由于pvt变化,可以生成具有与目标频率不同的频率的第一时钟clk1。

49.具体地,参照图1和图5,时钟生成器10可以包括:nor门,使能信号enable和第一时钟clk1被输入到nor门;以及偶数数量的反相器inv1至inv6,用于通过延迟nor门的输出来再次输出第一时钟clk1。在这种情况下,nor门和偶数数量的反相器inv1至inv6可以以反馈回路的形式联接。因此,在时钟生成器10中,响应于为“0”的使能信号enable,第一时钟clk1被输出为“1”,并且同时“1”通过nor门和六个反相器inv1至inv6被反馈并被输入到nor门。因此,响应于被反馈并被输入到nor门的信号“1”,第一时钟clk1被输出为“0”,并且同时“0”通过nor门和六个反相器inv1至inv6再次被反馈并被输入到nor门,使得时钟生成器10的状态返回其初始状态。如上所述,当使能信号enable为“0”时,由于重复这种任务,因此可以触发第一时钟clk1。

50.相反,响应于为“1”的使能信号enable,第一时钟clk1被输出为“0”,并且同时“0”通过nor门和六个反相器inv1至inv6被反馈并被输入到nor门。如上所述,信号“0”被反馈并被输入到nor门,但使能信号enable为“1”。因此,第一时钟clk1被持续输出为“0”,并且同时“0”通过nor门和六个反相器inv1至inv6被反馈并被输入到nor门。如上所述,当使能信号enable为“1”时,不能触发第一时钟clk1。

51.在这种情况下,时钟生成器10中包括的nor门和反相器inv1至inv6是通过cmos晶体管的连接实施的逻辑门。根据半导体装置1的pvt变化,这种cmos晶体管可能错误地操作。例如,cmos晶体管可能在时钟生成器10中包括的反相器inv1至inv6中的每一个的延迟量大于或小于目标延迟量的状态下而操作。

52.因此,当设计半导体装置1时,期望时钟生成器10将生成具有目标频率的目标时钟。然而,当时钟生成器10安装在半导体装置1上并操作时,由于发生pvt变化,时钟生成器10可以生成具有与目标频率不同的频率的第一时钟clk1。

53.此外,每当触发输入时钟21时,代码生成器20可以通过改变输入代码22的值来生成输出代码out_code,并且可以通过反馈来接收所生成的输出代码out_code。在实施例中,代码生成器20可以初始接收输入代码(例如,起始代码start_code或计数代码count_code),当触发输入时钟(例如,第一时钟clk1或第二时钟clk2)时改变所接收的输入代码的值以生成输出代码out_code,并且接收与输出代码out_code相关联的反馈信号feedback。例如,可以通过对输出代码out_code的多个位执行逻辑运算来获得反馈信号feedback。为

了改变输入代码22的值,代码生成器20可以在第一模式下执行设置操作,并且在第二模式下执行设置操作的逆操作(或逆设置操作)。在实施例中,代码生成器20可以是线性反馈移位寄存器(lfsr)。

54.此外,操作控制器30可以控制代码生成器20在测试区段中进入第一模式,可以在代码生成器20进入第一模式的第一时间将第一时钟clk1和起始代码start_code传输到代码生成器20,并且可以在代码生成器20退出第一模式的第二时间将代码生成器20的输出代码out_code设置为计数代码count_code。即,在测试区段的操作开始之后,操作控制器30可以通过将由时钟生成器10生成的第一时钟clk1和起始代码start_code传输到代码生成器20的操作,控制代码生成器20在第一时间进入第一模式。如上所述,操作控制器30可以通过将第一时钟clk1作为代码生成器20的输入时钟21输入并将起始代码start_code作为代码生成器20的输入代码22输入,控制代码生成器20在第一时间进入第一模式。因此,每当在代码生成器20进入第一模式的区段期间触发第一时钟clk1时,代码生成器20可以通过执行设置操作改变输入代码22的值来生成输出代码out_code,并且可以通过反馈接收所生成的输出代码out_code。在这种情况下,在代码生成器20进入第一模式的区段中,第一输入到代码生成器20的输入代码22可以是起始代码start_code,并且第二输入到代码生成器20的输入代码22可以是所反馈的输出代码out_code。因此,在代码生成器20进入第一模式的区段期间,代码生成器20可以通过第一时钟clk1的触发计数来重复执行设置操作。说明书中的术语“代码生成器20进入第一模式的区段”可以对应于代码生成器20进入第一模式的第一时间和代码生成器20退出第一模式的第二时间之间的第一时间间隔。例如,在代码生成器20在第一模式下操作的第一时间间隔期间,代码生成器20可以初始从操作控制器30接收起始代码start_code作为输入代码,当触发第一时钟clk1时执行第一设置操作以生成具有第一值的输出代码out_code,接收与输出代码out_code相关联的反馈信号feedback,当触发第一时钟clk1时执行第二设置操作以生成具有第二值的输出代码out_code等。

55.此外,操作控制器30可以大体上在代码生成器20退出第一模式的第二时间,将由代码生成器20生成的输出代码out_code设置为计数代码count_code。即,操作控制器30可以在代码生成器20退出第一模式的第二时间,通过停止触发由时钟生成器10生成的第一时钟clk1的操作来控制代码生成器20退出第一模式。如上所述,操作控制器30可以停止触发被提供为代码生成器20的输入时钟21的第一时钟clk1,可以在停止触发第一时钟clk1之前将输出代码out_code设置为计数代码count_code,并且可以存储计数代码count_code。

56.此外,操作控制器30可以控制代码生成器20在测试区段之后的检查区段中进入第二模式,可以在代码生成器20进入第二模式的第三时间将第二时钟clk2和计数代码count_code传输到代码生成器20,并且可以通过对第二时钟clk2的触发计数进行计数,直到代码生成器20的输出代码out_code与起始代码start_code具有相同的值,来生成监测信息。在这种情况下,可以在第二时钟clk2具有比第一目标频率更低的第二目标频率的状态下从监测电路的外部输入第二时钟clk2,第一目标频率是时钟生成器10中为第一时钟clk1而设置的。即,在检查区段的操作开始之后,操作控制器30可以通过将外部输入的第二时钟clk2和计数代码count_code传输到代码生成器20,控制代码生成器20进入第二模式。如上所述,操作控制器30可以通过将第二时钟clk2作为代码生成器20的输入时钟21输入并将计数代码count_code作为代码生成器20的输入代码22输入,控制代码生成器20进入第二模式,该计

数代码count_code具有在代码生成器20退出第一模式的第二时间设置的值。因此,每当在代码生成器20进入第二模式的区段期间触发第二时钟clk2时,代码生成器20可以通过执行设置操作的逆操作改变输入代码22的值来生成输出代码out_code,并且可以通过反馈来接收所生成的输出代码out_code。在这种情况下,在代码生成器20进入第二模式的区段中,第一输入到代码生成器20的输入代码22可以是计数代码count_code,并且第二输入到代码生成器20的输入代码22可以是所反馈的输出代码out_code。因此,在代码生成器20进入第二模式的区段期间,代码生成器20可以通过第二时钟clk2的触发计数来重复执行设置操作的逆操作。说明书中的术语“代码生成器20进入第二模式的区段”可以对应于代码生成器20进入第二模式的第三时间和代码生成器20退出第二模式的第四时间之间的第二时间间隔。例如,在代码生成器20在第二模式下操作的第二时间间隔期间,代码生成器20可以初始从操作控制器30接收计数代码count_code作为输入代码,当触发第二时钟clk2时执行第一逆设置操作以生成具有第一值的输出代码out_code,接收与输出代码out_code相关联的反馈信号feedback,当触发第二时钟clk2时执行第二逆设置操作以生成具有第二值的输出代码out_code等。

57.在这种情况下,计数代码count_code可以是由代码生成器20生成的代码,代码生成器20在代码生成器20进入第一模式的第一时间接收起始代码start_code作为输入代码22,并且通过在代码生成器20进入第一模式的区段期间的第一时钟的触发计数,例如n个触发计数,执行设置操作。因此,当代码生成器20在代码生成器20进入第二模式的第三时间接收计数代码count_code作为输入代码22并响应于第二时钟clk2的触发而执行设置操作的第n个逆操作时,代码生成器20的输出代码out_code可以具有与起始代码start_code的值相同的值。在这种情况下,n可以是1或更大的自然数。因此,操作控制器30可以对第二时钟clk2的触发计数进行计数,直到在代码生成器20进入第二模式的区段中输出代码out_code的值与代码生成器20的起始代码start_code的值变得相同,并且可以生成计数值作为监测信息。即,当在代码生成器20进入第二模式的区段中输出代码out_code的值变得等于代码生成器20的起始代码start_code的值时,操作控制器30可以停止对第二时钟clk2的触发计数进行计数的操作,并且可以生成停止的计数值作为监测信息。

58.此外,当在代码生成器20进入第二模式的区段中输出代码out_code的值变得等于代码生成器20的起始代码start_code的值时,即响应于监测信息的生成,操作控制器30可以通过停止将第二时钟clk2传输到代码生成器20来控制代码生成器20退出第二模式。

59.换句话说,操作控制器30可以在测试区段的操作开始之后,通过将第一时钟clk1和起始代码start_code传输到代码生成器20来控制代码生成器20进入第一模式,并且然后可以在经过设置时间之后的时间,通过停止触发传输到代码生成器20的第一时钟clk1,来控制代码生成器20退出第一模式。例如,操作控制器30可以在第一时钟clk1和起始代码start_code被传输到代码生成器20的第一时间控制代码生成器20进入第一模式,并且通过在第二时间停止触发第一时钟clk1来控制代码生成器20退出第一模式,给定时间间隔(例如,预先确定的时间间隔)在第一时间与第二时间之间。

60.更具体地,在测试区段的操作开始之后,在第一时钟clk1的边沿和第二时钟clk2的边沿同步的时间(例如,第一时间),操作控制器30可以通过将第一时钟clk1和起始代码start_code传输到代码生成器20来控制代码生成器20进入第一模式。

61.此外,在从代码生成器20进入第一模式的第一时间起经过与触发第二时钟clk2设置计数的时间相对应的设置时间间隔(例如,第一时间间隔)之后的时间(例如,第二时间),操作控制器30可以通过停止触发传输到代码生成器20的第一时钟clk1来控制代码生成器20退出第一模式。例如,操作控制器30可以控制代码生成器在从第一时间起第二时钟的触发数量达到给定数量(例如,预先确定的数量)的第二时间退出第一模式。

62.此外,在测试区段的操作后的检查区段的操作开始之后,操作控制器30可以通过将第二时钟clk2和计数代码count_code传输到代码生成器20来控制代码生成器20进入第二模式,并且可以响应于监测信息的生成,通过停止将第二时钟clk2传输到代码生成器20来控制代码生成器20退出第二模式。

63.更具体地,在测试区段的操作后的检查区段的操作开始之后,在第二时钟clk2的边沿同步的时间(例如,第三时间),操作控制器30可以通过将第二时钟clk2和计数代码count_code传输到代码生成器20来控制代码生成器20进入第二模式。

64.此外,响应于在从代码生成器20进入第二模式的第三时间起经过给定时间间隔(例如,第二时间间隔)之后计数代码count_code的值与起始代码start_code的值变得相同,即响应于监测信息的生成,操作控制器30可以通过停止将第二时钟clk2传输到代码生成器20来控制代码生成器20退出第二模式。

65.此外,操作控制器30可以响应于从监测电路的外部输入的控制信号controll而开始或终止测试区段或检查区段的操作。例如,操作控制器30可以响应于控制信号controll而开始或终止测试区段或者检查区段或者测试区段和检查区段两者。在这种情况下,控制信号controll可以由用于操作监测电路的装置(未示出)或系统(未示出)生成。即,操作控制器30可以响应于控制信号controll而开始或终止测试区段或检查区段的操作。不论控制信号controll具有任何形式,例如具有k位(k为2或更大的自然数)的并行或串行代码形式,都可以由设计员以各种方式设置。此外,尽管附图中未具体示出,但是操作控制器30可以响应于控制信号controll而执行测试区段或检查区段的操作,并且可以将执行的结果作为对控制信号controll的确认而输出到外部。例如,操作控制器30可以响应于控制信号controll而执行测试区段或检查区段的操作,并且可以将作为运行的结果而可以生成的计数代码count_code和监测信息作为对控制信号controll的确认而输出到外部。

66.更具体地,操作控制器30可以响应于控制信号controll而控制待开始的测试区段的操作,并且然后可以控制代码生成器20进入第一模式和退出第一模式。即,操作控制器30可以在响应于控制信号controll而开始测试区段的操作之后确定时钟生成器10将生成第一时钟clk1的时间,可以通过将触发的第一时钟clk1传输到代码生成器20来确定控制代码生成器20进入第一模式的时间(例如,第一时间),并且可以确定与第一模式的进入区段的持续时间相对应的设置时间间隔(例如,第一时间间隔)。

67.同样地,操作控制器30可以响应于控制信号controll而控制待开始的检查区段的操作,并且然后可以控制代码生成器20进入第二模式。即,操作控制器30可以在响应于控制信号controll而开始检查区段的操作之后,通过将外部输入的第二时钟clk2传输到代码生成器20,确定控制代码生成器20进入第二模式的时间(例如,第三时间)。

68.操作控制器30可以响应于控制信号controll而生成用于打开/关闭时钟生成器10的操作的使能信号enable。具体地,操作控制器30可以响应于控制信号controll而通过激

活使能信号enable,例如使使能信号enable具有对应于“0”的第一逻辑值,来控制时钟生成器10生成第一时钟clk1。此外,操作控制器30可以响应于代码生成器20退出第一模式而通过停用使能信号enable,例如使使能信号enable具有对应于“1”的第二逻辑值,来控制时钟生成器10不生成第一时钟clk1。即,操作控制器30可以仅在代码生成器20已经进入第一模式的区段中控制时钟生成器10操作并生成第一时钟clk1。

69.图2a示出根据实施例的监测电路中包括的操作控制器30a。

70.图2b示出根据另一实施例的监测电路中包括的操作控制器30b。

71.共同参照图2a和图2b,参照图1描述的监测电路的元件之中的操作控制器30a或30b可以包括信号生成器31、时钟选择器32、代码比较器33、代码存储装置35和计数器34。

72.信号生成器31可以响应于外部输入的控制信号controll和第二时钟clk2以及由时钟生成器10生成的第一时钟clk1而生成使能信号enable和模式选择信号mode。

73.此外,时钟选择器32可以响应于由信号生成器31生成的模式选择信号mode,通过选择由时钟生成器10生成的第一时钟clk1并将第一时钟clk1传输到代码生成器20,来控制代码生成器20进入第一模式。此外,时钟选择器32可以响应于由信号生成器31生成的模式选择信号mode,通过选择外部输入的第二时钟clk2并将第二时钟clk2传输到代码生成器20,来控制代码生成器20进入第二模式。

74.此外,在代码生成器20进入第二模式的区段期间,每当触发外部输入的第二时钟clk2时,代码比较器33可以将从代码生成器20接收的输出代码out_code的值与起始代码start_code的值进行比较。即,每当在代码生成器20进入第二模式的区段期间触发第二时钟clk2时,代码比较器33a可以将从代码生成器20接收的输出代码out_code的值与起始代码start_code的值进行比较,该第二模式的进入时间和退出时间通过模式选择信号mode而限定。作为比较的结果,当从代码生成器20接收的输出代码out_code的值与起始代码start_code的值相同时,代码比较器33a可以生成指示输出代码out_code的值与起始代码start_code的值相同的信号(例如,比较信号)comp,并且可以将该信号传输到计数器34。

75.此外,在代码生成器20退出第一模式的时间,代码存储装置35a可以将从代码生成器20接收的输出代码out_code作为计数代码count_code存储,代码生成器20退出第一模式的时间响应于由信号生成器31生成的模式选择信号mode而限定。此外,在代码生成器20进入第二模式的时间,代码存储装置35a可以将所存储的计数代码count_code传输到代码生成器20,代码生成器20进入第二模式的时间响应于由信号生成器31生成的模式选择信号mode而限定。

76.此外,计数器34可以在代码生成器20进入第二模式的区段期间对外部输入的第二时钟clk2的触发计数(或触发数量)进行计数,第二模式的进入时间和退出时间响应于由信号生成器31生成的模式选择信号mode而限定,并且可以响应于代码比较器33a的输出信号而生成监测信息。即,计数器34可以生成第二时钟clk2的触发计数作为监测信息,该第二时钟clk2的触发计数是通过从代码生成器20进入第二模式的时间到由代码比较器33a输出的信号comp指示从代码生成器20接收的输出代码out_code的值与起始代码start_code的值相同的时间,对第二时钟clk2的触发计数进行计数而获得的。

77.参照图2a,代码比较器33a可以存储起始代码start_code的值。因此,在代码生成器20进入第一模式的时间,代码比较器33a可以将起始代码start_code传输到代码生成器

20,代码生成器20进入第一模式的时间响应于由信号生成器31生成的模式选择信号mode而限定。此外,每当在代码生成器20进入第二模式的区段期间触发第二时钟clk2时,代码比较器33a可以将从代码生成器20接收的输出代码out_code的值与所存储的起始代码start_code的值进行比较,该第二模式的进入时间和退出时间响应于由信号生成器31生成的模式选择信号mode而限定。如上所述,如果起始代码start_code存储在代码比较器33a中,则代码存储装置35a可以存储计数代码count_code而不存储起始代码start_code。

78.参照图2b,不同于图2a,起始代码start_code可以不存储在代码比较器33b中。相反,在图2b中,起始代码start_code可以存储在代码存储装置35b中。即,在图2b中,起始代码start_code和计数代码count_code可以存储在代码存储装置35b中。

79.具体地,代码存储装置35b可以存储起始代码start_code。因此,在代码生成器20进入第一模式的时间,代码存储装置35b可以将所存储的起始代码start_code传输到代码生成器20,代码生成器20进入第一模式的时间响应于由信号生成器31生成的模式选择信号mode而限定。此外,在代码生成器20进入第二模式的区段期间,代码存储装置35b可以将所存储的起始代码start_code传输到代码比较器33b,第二模式的进入时间和退出时间响应于由信号生成器31生成的模式选择信号mode而限定。此外,在代码生成器20退出第一模式的时间,代码存储装置35b可以将从代码生成器20接收的输出代码out_code作为计数代码count_code存储,代码生成器20退出第一模式的时间响应于由信号生成器31生成的模式选择信号mode而限定。此外,在代码生成器20进入第二模式的时间,代码存储装置35b可以将所存储的计数代码count_code传输到代码生成器20,代码生成器20进入第二模式的时间响应于由信号生成器31生成的模式选择信号mode而限定。

80.作为参照,时钟选择器32响应于模式选择信号mode而开始将第一时钟clk1传输到代码生成器20的时间可以被限定为代码生成器20进入第一模式的时间。此外,时钟选择器32响应于模式选择信号mode而停止将第一时钟clk1传输到代码生成器20的时间可以被限定为代码生成器20退出第一模式的时间。此外,时钟选择器32响应于模式选择信号mode而开始将第二时钟clk2传输到代码生成器20的时间可以被限定为代码生成器20进入第二模式的时间。此外,时钟选择器32响应于模式选择信号mode而停止将第二时钟clk2传输到代码生成器20的时间可以被限定为代码生成器20退出第二模式的时间。

81.此外,信号生成器31可以响应于外部输入的控制信号controll而生成模式选择信号mode。在这种情况下,代码生成器20的操作结果或计数器34的操作结果可以实时地并入到外部输入的控制信号controll中。例如,通过计数器34将监测信息输出到外部的操作可以并入到控制信号controll中,并且因此可以控制信号生成器31生成用于停止将第二时钟clk2从时钟选择器32传输到代码生成器20的模式选择信号mode。

82.图3示出根据实施例的操作控制器30a或30b中包括的信号生成器31和时钟选择器32。

83.参照图3,在图2a中的操作控制器30a或图2b中的操作控制器30b的元件之中的信号生成器31可以包括内部信号生成器311、第一同步器312和第二同步器313。此外,在图2a中的操作控制器30a或图2b中的操作控制器30b的元件之中的时钟选择器32可以包括多工器321和时钟传输器322。

84.首先,信号生成器31中包括的内部信号生成器311可以响应于外部输入的控制信

号controll而生成内部使能信号in_enable和模式选择信号mode。在这种情况下,内部信号生成器311可以在响应于控制信号controll而开始测试区段的操作之后,控制代码生成器20进入第一模式和退出第一模式。即,内部信号生成器311可以在响应于控制信号controll而开始测试区段的操作之后,通过激活内部使能信号in_enable,确定时钟生成器10的操作开始的时间。此外,内部信号生成器311可以在响应于控制信号controll而开始测试区段的操作之后,通过控制模式选择信号mode以具有第一值,确定控制代码生成器20进入第一模式的时间,并且可以基于模式选择信号mode具有第一值的区段的持续时间有多长,确定与代码生成器20进入第一模式的区段相对应的设置时间。在这种情况下,内部信号生成器311可以控制内部使能信号in_enable被激活的时间与模式选择信号mode被控制以具有第一值的时间彼此同步。内部信号生成器311可以控制内部使能信号in_enable被激活的时间与模式选择信号mode被控制以具有第一值的时间彼此部分不同。

85.同样地,内部信号生成器311可以在响应于控制信号controll而已经开始检查区段的操作之后,控制代码生成器20进入第二模式和退出第二模式。即,内部信号生成器311可以在响应于控制信号controll而已经开始检查区段的操作之后,通过停用内部使能信号in_enable,确定时钟生成器10的操作终止的时间。此外,内部信号生成器311可以在响应于控制信号controll而已经开始检查区段的操作之后,通过控制模式选择信号mode以具有第二值,确定控制代码生成器20进入第二模式的时间,并且可以通过控制模式选择信号mode以具有第三值,确定控制代码生成器20退出第二模式的时间。

86.此外,信号生成器31中包括的第一同步器312可以使内部使能信号in_enable与外部输入的第二时钟clk2的边沿同步,并且可以将同步后的信号作为使能信号enable传输到时钟生成器10。

87.此外,信号生成器31中包括的第二同步器313可以检测从时钟生成器10接收的第一时钟clk1与外部输入的第二时钟clk2的边沿同步的时间。即,第二同步器313可以在第一时钟clk1的边沿与第二时钟clk2的边沿同步的时间生成触发的输出信号。

88.在这种情况下,第一时钟clk1的边沿和第二时钟clk2的边沿可以同步的原因是能够控制时钟生成器10的操作开始/终止的使能信号enable是通过第一同步器312与第二时钟clk2同步的信号。即,使能信号enable被激活或停用的时序(timing)可以通过第一同步器312与第二时钟clk2的边沿同步。因此,由时钟生成器10生成的第一时钟clk1和外部输入的第二时钟clk2具有不同的触发频率,但是第一时钟clk1的边沿和第二时钟clk2的边沿可以周期性地同步。

89.此外,响应于由信号生成器31中包括的内部信号生成器311生成的模式选择信号mode,时钟选择器32中包括的多工器321可以选择由时钟生成器10生成的第一时钟clk1和外部输入的第二时钟clk2中的任意一个,并且可以输出所选择的时钟。即,多工器321可以响应于与代码生成器20进入第一模式的区段相对应的模式选择信号mode的值来选择第一时钟clk1,并且可以输出所选择的第一时钟clk1。例如,多工器321可以响应于具有第一值的模式选择信号mode而选择第一时钟clk1,并且可以输出所选择的第一时钟clk1。此外,多工器321可以响应于与代码生成器20进入第二模式的区段相对应的模式选择信号mode的值来选择第二时钟clk2,并且可以输出所选择的第二时钟clk2。例如,多工器321可以响应于具有第二值的模式选择信号mode而选择第二时钟clk2并输出所选择的第二时钟clk2,并且

可以响应于具有第三值的模式选择信号mode而不选择任何时钟。

90.此外,响应于模式选择信号mode和由信号生成器31中包括的第二同步器313输出的信号,时钟选择器32中包括的时钟传输器322可以将由多工器321选择的时钟,即第一时钟clk1或第二时钟clk2,传输到代码生成器20。即,当将由多工器321输出的第一时钟clk1或第二时钟clk2传输到代码生成器20时,时钟传输器322可以恢复由于多工器321的操作而使相位延迟或抖动的第一时钟clk1或第二时钟clk2,并且可以传输恢复后的第一时钟clk1或第二时钟clk2。

91.图4a、图4b和图4c是示出以描述根据实施例的监测电路中包括的代码生成器20的示例的示图。

92.首先,参照图4a和图4b,可以假设代码生成器20包括至少四个移位寄存器作为线性反馈移位寄存器(lfsr)。然而,本公开的实施例不限于此,并且移位寄存器的数量可以根据实施例而改变。

93.具体地,可以假设图4a所示的代码生成器20的配置针对代码生成器20进入第一模式的情况。此外,可以假设图4b所示的代码生成器20的配置针对代码生成器20进入第二模式的情况。

94.在这种情况下,针对图4a的代码生成器20中包括的四个移位寄存器以及图4b的代码生成器20中包括的四个移位寄存器,可以假设物理上存在的四个移位寄存器根据操作模式以不同方式操作。针对图4a的代码生成器20中包括的四个移位寄存器以及图4b的代码生成器20中包括的四个移位寄存器,还可以假设八个移位寄存器物理上完全彼此分离。

95.参照图1、图4a和图4c,代码生成器20可以执行改变输入代码22的值的操作,从而以这种方式通过每当触发输入时钟21时改变输入代码22的值来生成输出代码out_code并通过反馈接收所生成的输出代码out_code。在图4a中,改变输入代码22的值的操作可以是四个寄存器中的每一个从第一寄存器register 0到第四寄存器register 3分别移位1个位的操作,以及传输作为对由第三寄存器register 2和第四寄存器register 3输出的位执行xor运算的结果而生成的1个位作为第一寄存器register 0的输入的操作,由第三寄存器register 2和第四寄存器register 3输出的位在作为移位操作的结果而生成的输出代码out_code的位之中。在图4a中,因为将第一时钟clk1作为输入时钟21输入并且将起始代码start_code作为输入代码22输入,所以代码生成器20可以在第一模式下操作。即,在图4a中,改变输入代码22的值的操作是设置操作。基于第一时钟clk1的触发计数,输出代码out_code的值可以根据设置序列(sequence)而改变。

96.参照图1、图4b和图4c,代码生成器20可以执行改变输入代码22的值的操作,从而以这种方式通过每当触发输入时钟21时改变输入代码22的值来生成输出代码out_code并通过反馈接收所生成的输出代码out_code。在图4b中,改变输入代码22的值的操作可以是四个寄存器中的每一个从第四寄存器register 3到第一寄存器register 0分别移位1个位的操作,以及传输作为对由第一寄存器register 0和第四寄存器register 3输出的位执行xor运算的结果而生成的1个位作为第四寄存器register 3的输入的操作,由第一寄存器register 0和第四寄存器register 3输出的位在作为移位操作的结果而生成的输出代码out_code的位之中。在图4b中,因为将第二时钟clk2作为输入时钟21输入并且将计数代码count_code作为输入代码22输入,所以代码生成器20可以在第二模式下操作。即,在图4b

中,改变输入代码22的值的操作是设置操作的逆操作。基于第二时钟clk2的触发计数,输出代码out_code的值可以以与设置序列相反的方向改变。

97.如图4c所示,当起始代码start_code的值为“1000”时,如果在触发第一时钟clk1时执行设置操作,则可以生成具有值“0100”的输出代码out_code。此外,在已经反馈并输入具有值“0100”的输出代码out_code的状态下,如果在触发第一时钟clk1时执行设置操作,则可以生成具有值“0010”的输出代码out_code。通过这种方式,输出代码out_code的值可以根据从起始代码start_code起重复执行设置操作的次数而不同。即,起始代码start_code的值与输出代码out_code的值之间的差异可以是指示已经触发第一时钟clk1多少次的信息。

98.相反,当计数代码count_code的值为“0101”时,如果在触发第二时钟clk2时执行设置操作的逆操作,则可以生成具有值“1011”的输出代码out_code。此外,在已经反馈并输入具有值“1011”的输出代码out_code的状态下,如果在触发第二时钟clk2时执行设置操作的逆操作,则可以生成具有值“0110”的输出代码out_code。通过这种方式,如果从计数代码count_code起重复执行设置操作的逆操作,则可以在特定时间生成与起始代码start_code具有相同值的输出代码out_code。即,可以生成第二时钟clk2的触发计数作为监测信息,该第二时钟clk2的触发计数是使计数代码count_code的值与起始代码start_code的值相同所需的。

99.根据本公开的实施例,半导体装置中包括的环形振荡器所生成的具有相对较高频率的时钟(例如,第一时钟clk1)与起始代码(例如,起始代码start_code)一起被输入到线性反馈移位寄存器(lfsr)。lfsr可以执行与高速触发操作相对应的设置操作,并且作为设置操作的结果而生成计数代码(例如,计数代码count_code)。此后,lfsr接收具有相对较低频率的外部输入时钟(例如,第二时钟clk2)以及计数代码,并且执行与低速触发操作相对应的设置操作的逆操作。因此,可以以低速对起始代码和计数代码之间所需的时钟的触发计数进行计数。

100.因此,具有可以精确地对由环形振荡器生成的具有高频率的时钟的触发计数进行计数的效果。例如,根据本公开的实施例的监测电路包括代码生成器,该代码生成器通过在第一模式下使用具有相对较高频率的第一时钟执行一个或多个设置操作,从起始代码起改变输出代码,以生成计数代码。这种代码生成器可以包括线性反馈移位寄存器(lfsr)和逻辑门(例如,xor门),并且因此可以适于使用具有相对较高频率的第一时钟来执行设置操作,以生成计数代码。代码生成器进一步通过在第二模式下使用具有相对较低频率的第二时钟来执行一个或多个逆设置操作,从计数代码起改变输出代码,直到输出代码变得等于起始代码。监测电路中的计数器在监测电路在第二模式下操作的时间间隔期间对第二时钟信号的触发数量进行计数。因此,监测电路可以在不使用高速计数器的情况下精确地计算出环形振荡器的具有高频率的时钟的触发数量。

101.在实施例中,一种控制监测电路的方法包括:在代码生成器进入第一模式的第一时间,将第一时钟作为输入时钟并且将起始代码作为输入代码提供到代码生成器;通过在第一模式下执行一个或多个设置操作,改变输入代码的值以生成输出代码;在代码生成器退出第一模式的第二时间将输出代码设置为计数代码;在代码生成器进入第二模式的第三时间,提供第二时钟作为输入时钟并且提供计数代码作为输入代码,第二时钟具有比第一

时钟的频率更低的频率;通过在第二模式下执行一个或多个逆设置操作,改变输入代码的值以生成输出代码;并且对在第二模式下的第二时钟的触发数量进行计数,直到输出代码的值变得等于起始代码的值,以生成监测信息。

102.在实施例中,该方法进一步包括:控制代码生成器在第一时间进入第一模式;并且控制代码生成器在第二时间退出第一模式,第一时间和第二时间之间的第一时间间隔是预先确定的。

103.在实施例中,该方法进一步包括:控制代码生成器在第三时间进入第二模式;并且响应于所生成的监测信息而控制代码生成器在第四时间退出第二模式。

104.在实施例中,当在第一模式下触发第一时钟时,代码生成器执行设置操作,并且当在第二模式下触发第二时钟时,代码生成器执行逆设置操作。

105.在实施例中,代码生成器包括:多个寄存器,生成输出代码;以及逻辑门,接收输出代码的多个位,并且对所接收的输出代码的位执行逻辑运算,以向多个寄存器中的一个提供指示逻辑运算结果的信号。

106.尽管已经出于说明性目的而描述了各个实施例,但对于本领域技术人员将显而易见的是,在不脱离如所附权利要求所限定的本公开的精神和范围的情况下,可以进行各种改变和修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。