1.本发明涉及画面显示领域,尤其涉及一种视频处理设备以及一种视频处理方法。

背景技术:

2.在目前视频显示行业中,对视频源进行处理都是通过视频处理设备中的可编程逻辑器件完成的,通常都是设置单个可编程逻辑器件来对视频源和视频数据进行处理等操作。

3.由于视频处理设备中单个可编程逻辑器件的处理带宽有限。通常的做法都是更换一个具有更大处理带宽的可编程逻辑器件进行处理。但是,更换成有更大处理带宽的可编程逻辑器件,其成本也会大大增加。

技术实现要素:

4.因此,为克服现有技术的缺陷和不足,本发明实施例提出一种视频处理设备以及一种视频处理方法。

5.一方面,本发明实施例提出的一种视频处理设备,包括:视频输入接口;第一可编程逻辑器件,连接所述视频输入接口;第二可编程逻辑器件,连接所述第一可编程逻辑器件;视频输出接口,连接所述第二可编程逻辑器件;其中,所述第一可编程逻辑器件用于通过所述视频输入接口接收多路视频数据、从所述多路视频数据中选择第一路视频数据和第二路视频数据、对所述第一路视频数据进行第一视频处理得到第一路处理后视频数据、并将所述第一路处理后视频数据和所述第二路视频数据传输至所述第二可编程逻辑器件;所述第二可编程逻辑器件用于对所述第二路视频数据进行第二视频处理得到第二路处理后视频数据、对所述第一路处理后视频数据和所述第二路处理后视频数据进行叠加处理并通过所述视频输出接口输出。

6.在现有技术中,由于单个可编程逻辑器件的处理带宽有限,通常都是更换有更大处理带宽的可编程逻辑器件进行处理。当需要更换有更大处理带宽的可编程逻辑器件,视频处理设备所需的成本也会大大增加。本技术通过设置第一可编程逻辑器件以及第二可编程逻辑器件分别对多路视频数据中的第一视频数据和第二视频数据进行处理,然后进行叠加后输出,平衡资源的消耗,挺高设备处理能力,达到与有更大处理带宽的可编程逻辑器件具有相类似的处理能力,从而减少视频处理设备的整体成本。

7.在本发明的一个实施例中,所述第一可编程逻辑器件包括:视频数据选择模块、第一视频数据处理模块、视频数据打包模块;其中,所述视频数据选择模块,用于从所述多路视频数据中选择所述第一路视频数据和所述第二路视频数据、传输所述第一路视频数据至所述第一视频数据处理模块、以及传输所述第二路视频数据至所述视频数据打包模块;所述第一视频数据处理模块用于对所述第一路视频数据进行所述第一视频处理得到所述第一路处理后视频数据并传输所述第一路处理后视频数据至所述视频数据打包模块;所述视频数据打包模块用于对所述第一路处理后视频数据和所述第二路视频数据分别打包并传

输至所述第二可编程逻辑器件。

8.在本发明的一个实施例中,所述第一视频数据处理模块包括:第一画质调整单元和第一缩放单元;其中,所述第一画质调整单元用于对所述第一路视频数据进行第一画质调整处理得到第一路画质调整后视频数据并将所述第一路画质调整后视频数据输出至所述第一缩放单元;所述第一缩放单元用于对所述第一路画质调整后视频数据进行第一缩放处理得到所述第一路处理后视频数据并输出所述第一路处理后视频数据至所述视频数据打包模块。

9.在本发明的一个实施例中,所述第二可编程逻辑器件包括:视频数据解析模块、第二视频数据处理模块、视频数据叠加模块;其中,所述视频数据解析模块用于将所述第一路处理后视频数据解析后传输至所述视频数据叠加模块,以及将所述第二路视频数据解析后传输至所述第二视频数据处理模块;所述第二视频数据处理模块用于对所述第二路视频数据进行所述第二视频处理得到所述第二路处理后视频数据并传输所述第二路处理后视频数据至所述视频数据叠加模块;所述视频数据叠加模块用于对所述第一路处理后视频数据和所述第二路处理后视频数据进行叠加处理并输出至所述视频输出接口。

10.在本发明的一个实施例中,所述第二视频数据处理模块包括:第二画质调整单元和第二缩放单元;其中,所述第二画质调整单元用于对所述第二路视频数据进行第二画质调整处理得到第二路画质调整后视频数据并输出所述第二路画质调整后视频数据至所述第二缩放单元;所述第二缩放单元用于对所述第二路画质调整后视频数据进行第二缩放处理得到所述第二路处理后视频数据并输出所述第二路处理后视频数据至所述视频数据叠加模块。

11.在本发明的一个实施例中,所述第二可编程逻辑器件还包括背景图像数据获取模块;所述背景图像数据获取模块用于获取背景图像数据并输出至所述视频数据叠加模块

12.在本发明的一个实施例中,所述视频数据叠加模块包括:输出时序产生单元和视频数据叠加单元;其中,所述输出时序产生单元用于根据输出时钟信号产生对应的输出时序,并将所述输出时序输出至所述视频数据叠加单元;所述视频数据叠加单元用于按照所述输出时序对所述第一路处理后视频数据、所述第二路处理后视频数据进行叠加处理后并输出至所述视频输出接口。

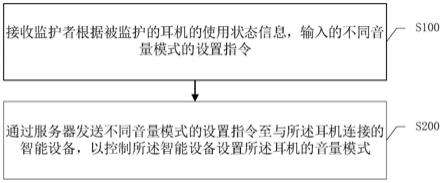

13.另一方面,本发明实施例提出了一种视频处理方法,应用于一种视频处理设备,所述视频处理设备包括第一可编程逻辑器件和第二可编程逻辑器件,所述第一可编程逻辑器件连接所述第二可编程逻辑器件;其特征在于,包括:通过所述第一可编程逻辑器件获取第一路视频数据和第二路视频数据;通过所述第一可编程逻辑器件对所述第一路视频数据进行第一视频处理得到第一路处理后视频数据并将所述第一路处理后视频数据和所述第二路视频数据传输至所述第二可编程逻辑器件;通过所述第二可编程逻辑器件对所述第二路视频数据进行第二视频处理得到第二路处理后视频数据;通过所述第二可编程逻辑器件对所述第一路处理后视频数据和所述第二路处理后视频数据进行叠加处理并输出。

14.在本发明的一个实施例中,所述第一可编程逻辑器件包括:视频数据选择模块、第一视频数据处理模块、视频数据打包模块;所述通过所述第一可编程逻辑器件接收第一路视频数据和第二路视频数据包括:通过所述视频数据选择模块从多路视频数据中选择所述第一路视频数据和所述第二路视频数据,并将所述第一路视频数据传输至所述第一视频数

据处理模块以及将所述第二路视频数据传输至所述视频数据打包模块;所述通过所述第一可编程逻辑器件对所述第一路视频数据进行第一视频处理得到第一路处理后视频数据并将所述第一路处理后视频数据和所述第二路视频数据传输至所述第二可编程逻辑器件包括:通过所述第一视频数据处理模块对所述第一路视频数据进行所述第一视频处理得到所述第一路处理后视频数据并将所述第一路处理后视频数据;通过所述视频数据打包模块对所述第一路处理后视频数据和所述第二路视频数据分别打包并传输至所述第二可编程逻辑器件。

15.在本发明的一个实施例中,所述第二可编程逻辑器件包括:视频数据解析模块、第二视频数据处理模块、视频数据叠加模块;所述通过所述第二可编程逻辑器件对所述第二路视频数据进行第二视频处理得到第二路处理后视频数据包括:通过所述视频数据解析模块对所述第二路视频数据解析后传输至所述第二视频数据处理模块;通过所述第二视频数据处理模块对所述第二路视频数据进行所述第二视频处理得到所述第二路处理后视频数据并传输至所述视频数据叠加模块;所述通过所述第二可编程逻辑器件对所述第一路处理后视频数据和所述第二路处理后视频数据进行叠加处理并输出包括:通过所述视频数据解析模块对所述第一路视频数据解析后传输至所述视频数据叠加模块;通过所述视频数据叠加模块对所述第一路处理后视频数据和所述第二路处理后视频数据进行叠加处理并输出。

16.由上可知,本发明上述技术特征可以具有如下有益效果:在本发明实施例中,设置第一可编程逻辑器件以及第二可编程逻辑器件分别对多路视频数据中的第一路视频数据和第二路视频数据进行处理,然后进行叠加后输出,平衡资源的消耗,挺高设备处理能力,达到与有更大处理带宽的可编程逻辑器件具有相类似的处理能力,从而减少视频处理设备的整体成本。

附图说明

17.为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

18.图1为本发明实施例的一种视频处理设备的结构示意图。

19.图2为本发明实施例的另一种视频处理设备的结构示意图。

20.图3为图1中的第一可编程逻辑器件的模块示意图。

21.图4为图1中的第二可编程逻辑器件的模块示意图。

22.图5为本发明具体实施例的涉及的视频处理设备的一个具体实施方式的结构示意图。

23.【附图标号说明】

24.10:视频处理设备;11:视频输入接口;12:第一可编程逻辑器件;13:第二可编程逻辑器件;14:视频输出接口;15:微处理芯片;16:易失性存储器;

25.121:视频数据选择模块;122:第一视频数据处理模块;123:视频数据打包模块;1221:第一画质调整单元;1222:第一缩放单元;

26.131:视频数据解析模块;132:第二视频数据处理模块;133:视频数据叠加模块;

134:背景图像数据获取模块;1321:第二画质调整单元;1322:第二缩放单元;1331:输出时序产生单元;1332:视频数据叠加单元。

具体实施方式

27.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

28.如图1和图2所示,本发明一实施例提供的一种视频处理设备10,例如包括:

29.视频输入接口11、第一可编程逻辑器件12、第二可编程逻辑器件13以及视频输出接口14。

30.其中,所述第一可编程逻辑器件12连接所述视频输入接口11;所述第二可编程逻辑器件13连接所述第一可编程逻辑器件12;所述视频输出接口14连接所述第二可编程逻辑器件13。

31.其中,所述视频输入接口11用于接收多路视频数据,其例如包括sdi接口、hdmi接口以及dp接口等等,在本实施例中,所述视频输入接口11可以包括1个12g的sdi接口,1个hdmi2.0接口,1个dp1.2接口,在其它实施例中,所述视频输入接口11还可以包括有dvi接口等等,具体此处不做限定。所述多路视频数据为对从多个视频输入接口输入的视频源或者视频源进行解析得到的多路视频数据。其中,所述视频数据可以是4k视频数据,也可以是8k视频数据,在本实施例中,所述多路视频数据例如是4k视频数据(例如分辨率为4096

×

2160的视频数据)。在其它实施例中,所述多路视频数据可以是2k视频数据(例如分辨率为2048

×

1080的视频数据),可以根据实际场景需求进行对应设置,具体此处不做限定。

32.所述第一可编程逻辑器件12用于通过所述视频输入接口11接收多路视频数据,并从所述多路视频数据中选择第一路视频数据和第二路视频数据,对所述第一路视频数据进行第一视频处理得到第一路处理后视频数据、并将所述第一路处理后视频数据和所述第二路视频数据传输至所述第二可编程逻辑器件13。其中,从所述多路视频中选择第一路视频数据和第二路视频数据的操作可以是通过用户对所述多路视频进行选择,然后通过第一可编程逻辑器件执行用户的选择操作后得到的所述第一路视频数据和所述第二路视频数据。在本实施例中,用户通过在视频处理设备10的内嵌软件上从所述多路视频中选择第一路视频数据和第二路视频数据,然后通过视频处理设备10的内嵌软件生成对应的指令发送给第一可编程逻辑器件,然后第一可编程逻辑器件根据所述指令从所述多路视频中选择第一路视频数据和第二路视频数据。在其它实施例中用户还可以通过pc机上的软件进行选择然后生成对应的指令发送给第一可编程逻辑器件进行对应操作,具体此处不作限定。

33.所述第二可编程逻辑器件13用于对所述第二路视频数据进行第二视频处理得到第二路处理后视频数据、对所述第一路处理后视频数据和所述第二路处理后视频数据进行叠加处理并通过所述视频输出接口14输出。

34.所述视频输出接口14用于将叠加处理后的视频数据输出至其他设备中,所述其他设备可以是显示屏,也可以是后端控制卡比如显示控制器(也称发送卡),也可以是智能设备等等。在本实施例中,所述视频输出接口14可例如与显示屏连接,视频输出接口14就可以

直接将叠加处理后的视频数据输出至显示屏中进行显示,在其它实施例中,所述视频输出接口14可以与其他设备进行连接,可以根据实际场景需求设置其它设备(例如说后端控制卡)与视频输出接口14连接,具体此处不做限定。其中,所述视频输出接口14其例如包括sdi接口、hdmi接口以及dp接口等等,在本实施例中,所述视频输出接口14可以包括1个12g的sdi接口,1个hdmi2.0接口,1个dp1.2接口,在其它实施例中,所述视频输出接口14还可以包括有dvi接口等等,具体此处不做限定。

35.在现有技术中,由于单个可编程逻辑器件的处理带宽有限,通常都是更换有更大处理带宽的可编程逻辑器件进行处理。当需要更换有更大处理带宽的可编程逻辑器件,视频处理设备所需的成本也会大大增加。本技术通过设置第一可编程逻辑器件以及第二可编程逻辑器件分别对多路视频数据中的第一视频数据和第二视频数据进行处理,然后进行叠加后输出,平衡资源的消耗,挺高设备处理能力,达到与有更大处理带宽的可编程逻辑器件具有相类似的处理能力,从而减少视频处理设备的整体成本。

36.如图2所示,所述视频处理设备10还可以包括:微处理芯片15以及易失性存储器16。

37.其中,所述微处理芯片15连接所述第一可编程逻辑器件12和所述第二可编程逻辑器件13;所述易失性存储器16连接所示第一可编程逻辑器件12、所述第二可编程逻辑器件13和所述微处理芯片15。所述微处理芯片15可例如为mcu。

38.其中,所述微处理芯片15用于下发指令给所述第一可编程逻辑器件12和所述第二可编程逻辑器件13,以使得所述第一可编程逻辑器件12和所述第二可编程逻辑器件13进行对应的处理。所述指令包括选择指令、处理指令、打包指令等等。

39.所述易失性存储器16用于存储所述第一可编程逻辑器件12、所述第二可编程逻辑器件13和所述微处理芯片15中产生的数据,例如说存储所述第一可编程逻辑器件12中的第一路处理后视频数据、所述第二可编程逻辑器件13中的第二路处理后视频数据以及微处理芯片15中产生的背景图像数据等等。当需要使用上述数据时,直接从易失性存储器16中对需要的数据进行读取即可。所述易失性存储器16可例如为ddr。

40.在本发明另一个具体的实施例中,如图3所示,所述第一可编程逻辑器件12包括:视频数据选择模块121、第一视频数据处理模块122、视频数据打包模块123。

41.其中,所述视频数据选择模块121用于从接收到的所述多路视频数据中选择其中的所述第一路视频数据和所述第二路视频数据,所述第一路视频数据为所述多路视频数据中的一路视频数据,所述第二路视频数据则为所述多路视频数据中除开第一路视频数据中的另一路视频数据。在本实施例中,视频数据选择模块121用于选择所述第一路视频数据和所述第二路视频数据,在其它实施例中,可以根据实际的需求选择三路视频数据或者四路视频数据等等,具体此处不做限定。

42.所述第一视频数据处理模块122用于对所述第一路视频数据进行第一视频处理得到第一路处理后视频数据,并将所述第一路处理后视频数据发送至所述视频数据打包模块123。所述第一视频处理例如是画质调整或者缩放或者裁剪等等处理,可以根据实际需要对第一视频处理进行具体设置,具体此处不做限定。

43.其中,所述第一视频数据处理模块122例如包括第一画质调整单元1221和第一缩放单元1222;

44.所述第一画质调整单元1221用于对所述第一路视频数据进行第一画质调整处理得到第一路画质调整后视频数据并将所述第一路画质调整后视频数据输出至所述第一缩放单元1222;

45.所述第一缩放单元1222用于对所述第一路画质调整后视频数据进行第一缩放处理得到所述第一路处理后视频数据并输出所述视频数据打包模块123。

46.值得一提的是,在本实施例中,所述第一画质调整单元1221和所述第一缩放单元1222的处理方案均可采用现有技术中的成熟方案进行处理,具体此处不再赘述。

47.在本实施例中,所述第一视频数据处理模块122可以包括第一画质调整单元1221和第一缩放单元1222,在其它实施例中,所述第一视频数据处理模块122还可以包括有裁剪单元或者拉伸单元,可以根据实际需求设置多个不同的处理单元对第一路视频数据进行处理,具体此处不做限定。

48.所述视频数据打包模块123用于对所述第一路处理后视频数据和所述第二路视频数据分别打包并传输至所述第二可编程逻辑器件13。其中,所述打包处理例如包括对所述第一路处理后视频数据和所述第二路视频数据分别进行传输协议打包,其中所述传输协议例如为视频编码协议,通过所述视频编码协议打包后生成的数据例如包含传输视频的信息,传输视频的分辨率等等。

49.在本发明另一个具体的实施例中,如图4所示,所述第二可编程逻辑器件13包括:视频数据解析模块131、第二视频数据处理模块132和视频数据叠加模块133;

50.其中,所述视频数据解析模块131用于将所述第一路处理后视频数据解析后传输至所述视频数据叠加模块133,以及将所述第二路视频数据解析后传输至所述第二视频数据处理模块132。所述视频数据解析模块131接收到的视频数据是通过所述视频数据打包模块123分别传输过来的第一路处理后视频数据和第二路视频数据,其通过固定的传输通道即可知道第一路处理后视频数据为第一可编程逻辑器件12中第一视频数据处理模块122处理后的视频数据,对接收的第一路处理后视频数据只进行解析,然后发送至视频数据叠加模块123;所述视频数据解析模块131然后通过固定的传输通道即可知道第二路视频数据是未经过处理的视频数据,然后将所述第二路视频数据发送至第二视频数据处理模块132进行处理。

51.所述第二视频数据处理模块132用于对所述第二路视频数据进行所述第二视频处理得到所述第二路处理后视频数据并传输至所述视频数据叠加模块132;所述第二视频处理例如是画质调整或者缩放或者裁剪等等处理,可以根据实际需要对第二视频处理进行具体设置,具体此处不做限定;

52.其中,所述第二视频数据处理模块132包括:第二画质调整单元1321和第二缩放单元1322;

53.其中,所述第二画质调整单元1321用于对所述第二路视频数据进行第二画质调整处理得到第二路画质调整后视频数据并输出所述第二路画质调整后视频数据至所述第二缩放单元1322;

54.所述第二缩放单元1322用于对所述第二路画质调整后视频数据进行第二缩放处理得到所述第二路处理后视频数据并输出所述视频数据叠加模块133。

55.值得一提的是,在本实施例中,所述第二画质调整单元1321和所述第二缩放单元

1322的处理方案均可采用现有技术中的成熟方案进行处理,具体此处不再赘述。

56.所述视频数据叠加模块133用于对所述第一路处理后视频数据和所述第二路处理后视频数据进行叠加处理并输出至所述视频输出接口14;

57.其中,所述视频数据叠加模块133包括:输出时序产生单元1331和视频数据叠加单元1332;

58.其中,所述输出时序产生单元1331用于根据输出时钟信号产生对应的输出时序,并将所述输出时序输出至所述视频数据叠加单元1332;所述输出时钟信号可以是视频输出接口14中给出的时钟信号,也可以是通过外部设备传输给所述输出时序产生单元1331的时钟信号,具体此处不做限定。

59.所述视频数据叠加单元1332用于按照所述输出时序对所述第一路处理后视频数据、所述第二路处理后视频数据进行叠加处理后输出至所述视频输出接口14。其中,在本实施例中,所述视频数据叠加单元1332的处理方案可采用现有技术中的成熟方案进行处理,具体此处不再赘述。

60.如图4所示,所述第二可编程逻辑器件13还包括背景图像数据获取模块134;

61.其中,所述背景图像数据获取模块134用于获取背景图像数据并输出至所述视频数据叠加模块133,所述背景图像数据可以是bkg视频数据,也可以是logo视频数据,具体此处不做限定。

62.为便于更清楚地理解本实施例的视频处理设备10,下面将结合图1-图5对其工作原理进行举例说明。

63.如图1-图5所示,在本实施例中,多路视频数据均为4k视频数据(例如分辨率为4096

×

2160的视频数据)。

64.在本实施例中,视频处理设备10为单板非插卡式设备,例如说为arm嵌入式器件或者是mcu嵌入式器件。

65.首先,视频输入接口11接收输入的多路视频源,然后第一可编程逻辑器件12对输入的多路视频源进行解码,得到多路视频数据,然后通过第一可编程逻辑器件12中的视频数据选择模块121(如图5所示的mux0,其中图5中两个mux0指的是同一个mux0)从多路视频数据中选择第一路视频数据和第二路视频数据,然后通过视频数据选择模块121将所述第一路视频数据传输至第一视频数据处理模块122,通过视频数据选择模块121将所述第二路视频数据传输至视频数据打包模块123。

66.其中,所述第一视频数据处理模块122中的第一画质调整单元1221(如图5所示的第一可编程逻辑器件12中的csc/gamma)对所述第一路视频数据进行画质调整处理,得到第一路画质调整后视频数据,并将所述第一路画质调整后视频数据发送至第一缩放单元1222,其中,所述第一画质调整单元1221的处理方案可采用现有技术中的成熟方案进行处理,具体此处不再赘述。

67.然后所述第一缩放单元1222(如图5所示的第一可编程逻辑器件12中的scaler)对所述第一画质调整后视频数据进行缩放处理,得到第一路处理后视频数据,将第一路处理后视频数据发送至易失性存储器16(如图5所示的ddr)以及发送至视频数据打包模块123。其中,所述第一缩放单元1222的处理方案可采用现有技术中的成熟方案进行处理,具体此处不再赘述。

68.所述视频数据打包模块123(如图5所示的第一可编程逻辑器件12中的serdes)接收到所述第一路处理后视频数据以及第二路视频数据后,对所述第一路处理后视频数据以及第二路视频数据后分别通过视频数据打包模块123进行传输协议的打包,所述传输协议例如包括视频编码协议,其中,通过传输协议打包后生成的数据中包含有传输视频数据的大小、传输视频的分辨率等必要信息,然后将第一路处理后视频数据传输到所述第二可编程逻辑器件13;然后所述视频数据选择单元121将所述第二路视频数据,传输至视频数据打包模块123直接进行传输协议的打包,传输至所述第二可编程逻辑器件13。

69.所述第二可编程逻辑器件13的视频数据解析模块131(如图5所示的第二可编程逻辑器件中13的serdes)将接收到的所述第一路处理后视频数据和所述第二路视频数据通过传输协议解析出对应的视频数据,如图5所示,所述视频数据解析模块131通过vid0传输通道接收所述第一路处理后视频数据,所述视频数据解析模块131通过vid1传输通道接收所述第二路视频数据,由于vid0和vid1传输通道通过物理方法固定在视频处理设备上,所以,视频数据解析模块131接收到第一路处理后视频数据即可知道第一路处理后视频数据不需要进行视频处理,然后将所述第一路处理后视频数据通过vid0通道传输至视频数据叠加模块133。然后将需要处理的第二路视频数据传输至第二视频数据处理模块132。

70.其中,所述第二视频数据处理模块132中的第二画质调整单元1321(如图5所示的第二可编程逻辑器件13中的csc/gamma)对所述第二路视频数据进行画质调整处理,得到第二路画质调整后视频数据,并将所述第二路画质调整后视频数据发送至第二缩放单元1322。其中,所述第二画质调整单元1321的处理方案可采用现有技术中的成熟方案进行处理,具体此处不再赘述.

71.然后所述第二缩放单元1322(如图5所示的第二可编程逻辑器件13中的scaler)对所述第二路画质调整后视频数据进行缩放处理,得到第二路处理后视频数据,将第二路处理后视频数据通过vid1通道发送至视频数据叠加模块133。其中,所述第二缩放单元1322的处理方案可采用现有技术中的成熟方案进行处理,具体此处不再赘述。

72.所述第二可编程逻辑器件13通过背景图像数据获取模块134(如图5所示的第二可编程逻辑器件13中的bkg/logo)从易失性存储器16中获取到背景图像数据,其中,所述背景图像数据可以是通过微处理芯片15(如图5所示的mcu)存储至易失性存储器16中,然后背景图像数据获取模块134将获取到的所述背景图像数据通过vid2通道发送至视频数据叠加模块133中。

73.所述输出时序产生单元1331(如图5所示的timing_gen)用于根据输出时钟信号产生对应的输出时序,并将所述输出时序输出至所述视频数据叠加单元1332;所述输出时钟信号可以是视频输出接口14中给出的时钟信号,也可以是通过外部设备传输给所述输出时序产生单元1331的时钟信号,具体此处不做限定。

74.所述视频数据叠加单元1332(如图5所示的blender)接收到产生的输出时序后,按照输出时序对所述第一路处理后视频数据、所述第二路处理后视频数据和所述背景图像数据依次叠加后,输出至视频输出接口14中,在本实施例中,所述视频数据叠加单元1332的处理方案可采用现有技术中的成熟方案进行处理,具体此处不再赘述。

75.所述视频输出接口14将叠加后视频数据输出,例如说输出至显示屏中进行显示,或者输出至后端控制卡比如显示控制器(也称发送卡)再进行传输等等。

76.上述可编程逻辑器件的数量可以根据所述第一可编程逻辑器件12中的视频数据选择模块121选择的多路视频数据来确定,例如说通过视频数据选择模块121选择三路视频数据,则可编程逻辑器件的数量为3个,即通过选择多路视频数据确定使用多个可编程逻辑器件。

77.综上所述,在现有技术中,由于单个可编程逻辑器件的处理带宽有限,通常都是更换有更大处理带宽的可编程逻辑器件进行处理。当需要更换有更大处理带宽的可编程逻辑器件,视频处理设备所需的成本也会大大增加。本技术通过设置第一可编程逻辑器件以及第二可编程逻辑器件分别对多路视频数据中的第一视频数据和第二视频数据进行处理,然后进行叠加后输出,平衡资源的消耗,挺高设备处理能力,达到与有更大处理带宽的可编程逻辑器件具有相类似的处理能力,从而减少视频处理设备的整体成本。

78.另外,可以理解的是,前述各个实施例仅为本发明的示例性说明,在技术特征不冲突、结构不矛盾、不违背本发明的发明目的前提下,各个实施例的技术方案可以任意组合、搭配使用。

79.在本发明所提供的几个实施例中,应该理解到,所揭露的系统,装置和/或方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述单元/模块的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多路单元或模块可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

80.所述作为分离部件说明的单元/模块可以是或者也可以不是物理上分开的,作为单元/模块显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多路网络单元上。可以根据实际的需要选择其中的部分或者全部单元/模块来实现本实施例方案的目的。

81.另外,在本发明各个实施例中的各功能单元/模块可以集成在一个处理单元/模块中,也可以是各个单元/模块单独物理存在,也可以两个或两个以上单元/模块集成在一个单元/模块中。上述集成的单元/模块既可以采用硬件的形式实现,也可以采用硬件加软件功能单元/模块的形式实现。

82.上述以软件功能单元/模块的形式实现的集成的单元/模块,可以存储在一个计算机可读取存储介质中。上述软件功能单元存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)的一个或多个处理器执行本发明各个实施例所述方法的部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(read-only memory,简称rom)、随机存取存储器(random access memory,简称ram)、磁碟或者光盘等各种可以存储程序代码的介质。

83.最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。