1.本公开的实施例涉及电机领域,特定来说涉及来自初始位置检测时序参数的电机电 阻及电感值。

背景技术:

2.电子装置及集成电路(ic)技术的激增已导致ic产品的商业化。随着新电子装置被开 发且ic技术进步,新ic产品被商业化。电子装置中所需的一个实例ic产品是直流(dc) 电机控制器。在一个实例电机控制器中,使用无传感器场定向控制(foc)算法来确定转 子位置且生成用于3相dc电机(例如,无刷dc电动机或“bldc”电机)的电机控制信 号,所述3相dc电机具有定子(所述电机的固定部分)及转子(所述电机的旋转部分)。为 了确定转子位置,无传感器foc算法使用经测量相电流,而不是接触式传感器或霍尔效 应传感器,所述接触式传感器或霍尔效应传感器往往随时间而磨损及/或增加电机设计复 杂性。另外,无传感器foc算法使用电机线圈的电感(l)值及电机线圈的电阻(r)值来确 定转子位置。在常规的无传感器foc算法案例中,r及l参数是使用仪器来测量且由 电机控制器存储为配置值,这表示非所要延迟及成本。改进电机控制器ic产品的工作 正在进行中。

技术实现要素:

3.根据本公开的至少一个实例,一种系统包括具有定子及转子的电机。所述系统还包 括耦合到所述定子的脉冲生成电路。所述系统还包括耦合到所述脉冲生成电路的电机控 制器。所述电机控制器经配置以:基于在初始位置检测(ipd)间隔期间获得的时序参数确 定所述电机的电感及电阻值;基于所述经确定电感及电阻值确定转子位置;及基于所述 经确定转子位置生成用于所述脉冲生成电路的控制信号。

4.根据本公开的至少一个实例,一种电机控制器装置包括:处理器;及感测电路,其 经耦合到所述处理器。所述感测电路包括:第一相电流感测电路;第二相电流感测电路; 及时序电路,其经耦合到所述第一及第二相电流感测电路。所述时序电路经配置以测量 由于在ipd间隔期间由所述第一及第二相电流感测电路感测到的不同相电流所致的电 流上升时间及下降时间。所述处理器经配置以基于所述经测量电流上升时间及下降时间 确定所述电机的电感及电阻值,且其中所述处理器经配置以基于所述经确定电感及电阻 值提供用于所述电机的控制信号。

5.根据本公开的至少一个实例,一种电机控制方法包括在ipd间隔期间将不同相电流 脉冲注入到电机中。所述电机控制方法还包括测量所述不同相电流脉冲中的每一者的电 流上升时间及电流下降时间。所述电机控制方法还包括基于所述经测量电流上升时间及 电流下降时间估计所述电机的电感及电阻值。所述电机控制方法还包括基于所述经估计 电感及电阻值计算与所述电机相关的转子位置。所述电机控制方法还包括基于所述经计 算转子位置将控制信号提供到脉宽调制(pwm)信号生成器。

附图说明

6.对于各种实例的详细描述,现在将参考附图,其中:

7.图1是展示根据实例实施例的系统的框图;

8.图2a及2b是展示根据实例实施例的具有无传感器场定向控制(foc)电机控制的系 统的框图;

9.图3a是表示根据实例实施例的逆变器电路及电机的组件的图;

10.图3b是根据实例实施例的用于分析负载电流(i

l

(t))的电阻器

‑

电感器(rl)电路的图;

11.图4a是根据实例实施例的相电流及转子位置的矢量表示的图;

12.图4b是根据实例实施例的与获得相电流上升时间及下降时间相关的波形的时序图;

13.图4c是展示根据实例实施例的用于获得电流上升时间及下降时间值的时序逻辑的 框图;

14.图5a是展示根据图4b的时序图的通过电机的相电流的图;

15.图5b是展示根据实例实施例的通过电机的相电流的图;

16.图6a到6c是展示根据实例实施例的通过电机的其它相电流的图;及

17.图7是展示根据实例实施例的电机控制器方法的流程图。

具体实施方式

18.本文中公开一种包含在电子电路或电机控制器中的感测电路,其中所述感测电路包 含用于测量在初始位置检测(ipd)间隔期间注入的相电流脉冲的时序参数的时序逻辑。使 用由所述感测电路获得的所述时序参数来估计电机的电阻(r)及电感(l)值。在一些实例 实施例中,使用所述经估计r及l值连同在所述ipd间隔期间获得的相电流测量来确 定转子位置。接着使用所述经确定转子位置来生成输入到脉宽调制(pwm)信号生成器的 控制信号(例如,(α、β)固定正交参考系中的定子矢量电压的分量)。使用从所述pwm信 号生成器输出的pwm信号来生成栅极驱动信号以控制逆变器(例如,3相逆变器)的开关 以将电流提供到电机。

19.在一些实例实施例中,所述感测电路的所述时序逻辑包含具有下限及上限的比较器。 使用所述比较器的输出来跟踪所述下限到所述上限之间的电流上升时间。还使用所述比 较器的所述输出来跟踪所述上限与所述下限之间的电流下降时间。在一些实例实施例中, 使用时钟计数及存储单元(例如,寄存器)来基于所述比较器输出存储电流上升时间值及 电流下降时间值。而且,在所提出感测电路中,所述时序逻辑在所述电流上升时间值及 所述电流下降时间值中解决比较器延迟。在一些实例实施例中,通过将所述下限及所述 上限两者与所述比较器一起使用来解决所述比较器延迟,从而得到更准确的电流上升时 间及电流下降时间值。

20.在不同实例中,所述感测电路是集成电路(ic)、多裸片模块(mdm)、多芯片模块、 片上系统(soc)或其它商用电路或装置的部分。在一些实例实施例中,所述感测电路是与 电机控制器相同的ic的部分。在其它实例中,所述感测电路及所述电机控制器在不同 ic上。在任一情况下,所述电机控制器使用感测电路测量来估计如本文中所描述的r及 l,且

执行其它电机控制操作。为了提供更好的理解,如下般使用附图来描述各种感测电 路选项及相关电机控制系统或案例。

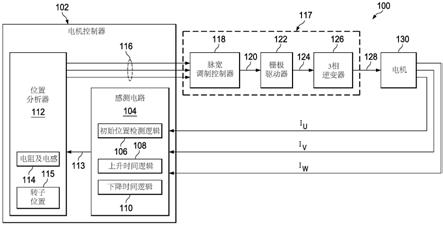

21.图1是展示根据实例实施例的系统100的框图。如所展示,系统100包括耦合到脉 冲生成电路117的电机控制器102,其中脉冲生成电路117经耦合到电机130且将相电 压及电流128提供到电机130。在图1的实例中,脉冲生成电路117包含pwm控制器 118,所述pwm控制器118经耦合到电机控制器102且经配置以基于来自电机控制器 102的位置分析器112的控制信号116生成pwm信号120。pwm信号122由栅极驱动 器122接收,所述栅极驱动器122将驱动信号124提供到3相逆变器126的开关(未展 示),从而得到用于电机130的相电压及电流128。

22.如所展示,电机130还作为包含电机控制器102的组件的反馈或控制回路的部分耦 合到电机控制器102。更具体来说,电机控制器102包含感测电路104,所述感测电路 104经配置以获得第一相电流(i

u

)的第一相电流感测测量、第二相电流(i

v

)的第二相电流 感测测量及/或第三相电流(i

w

)的第三相电流感测测量。在图1的实例中,感测电路104 被表示为包含用于在ipd间隔期间获得相电流感测值的ipd逻辑106。在一些实例实施 例中,ipd逻辑106包含电流感测电路及/或其它组件以测量在ipd间隔期间注入的相电 流脉冲(例如,及)。所述感测电路还包含经配置以在ipd 间隔期间测量相电流上升时间及下降时间值的上升时间逻辑108及下降时间逻辑110 (在本文中有时被称为时序逻辑)。

23.在一些实例实施例中,上升时间逻辑108经配置以获得在ipd间隔期间注入到电机 130中的一或多个相电流脉冲(例如,及)的上升时间参数。 在一些实例实施例中,上升时间逻辑108包含具有下限及上限的比较器(例如,图4c中 的比较器431)。上升时间逻辑108还包含时钟电路系统及经配置以基于比较器的输出存 储时钟计数的存储单元(例如,寄存器)。下降时间逻辑110经配置以获得在ipd间隔期 间注入到电机130中的一或多个相电流脉冲(例如,及) 的下降时间参数。在一些实例实施例中,下降时间逻辑110包含具有下限及上限的比较 器。下降时间逻辑110还包含时钟电路系统及经配置以基于比较器的输出存储时钟计数 的存储器(例如,寄存器)。

24.在图1的实例中,由感测电路104获得的值113被提供到位置分析器112。在一些 实例实施例中,值113包含相电流测量,及时序参数,例如在ipd间隔期间注入到电机 130中的一或多个相电流脉冲(例如,及)的脉冲上升时间 值及脉冲下降时间值。如图1中所表示,位置分析器112包含经配置以基于包含在值113 中的至少一些时序参数估计电机130的r及l值的r及l指令114。位置分析器112使 用经估计r及l值以及相电流测量来确定转子位置115,从所述转子位置115确定控制 信号116(例如,(α、β)固定正交参考系中的定子矢量电压的分量)。在一些实例实施例 中,位置分析器112的操作包含无传感器场定向控制(foc)算法操作来确定在图1的实 例中,控制信号116从位置分析器112提供到脉冲生成电路117。在一些实例实施例中, 位置分析器112使用无传感器foc算法来至少部分地基于基于包含在从感测电路104 获得的值113中的时序参数估计的r及l值来确定转子位置115。通过如本文中所描述 般估计r及l,可避免使用外部仪器来测量r及l。

25.图2a及2b是展示根据实例实施例的具有无传感器foc电机控制的系统200的框 图。如所展示,系统200包括经配置以执行由框222、224、226、228、230、232、234、 236、238、240、242、244及246所表示的各种无传感器foc算法操作的处理器220。 更具体来说,框222对应于基于从电流感测电路204(图1中的电流感测电路104的实 例)获得的第一及第二相电流感测测量的克拉克操作。框224对应于基于来自框222的 输出(i

α

及i

β

)及来自框226的θ估计(θ

est

)的帕克操作。框226对应于基于来自框222的 输出的反电磁力(bemf)观测器操作。框228对应于涉及ω

cmd

的速度曲线操作,其中ω

cmd

是命令电机速度。框230对应于基于框228的输出的加速度控制操作。框232对应于基 于框226及230的输出的速度控制器操作。框234对应于基于框232的输出的电流控制 操作,其中块234的输出是命令电流(i

q_cmd

)。框236对应于基于来自框234的i

q_cmd

及来自框224的i

q

的转矩控制器操作。框238对应于基于框236的输出(v

q

)的电压斜坡 操作。框240对应于基于来自框232的第一电流(i

d_cmd

)及来自框224的第二电流(i

d

)的 通量控制器操作。框242对应于基于框240的输出(v

d

)的电压斜坡操作。框244对应于 基于来自框238及242的输出的逆帕克操作。框246对应于基于来自框244的输出(v

α 及v

β

)的逆克拉克及空间矢量调制(svm)操作。

26.在一些实例实施例中,框246的输出对应于用于耦合到电机的脉冲生成电路117的 控制信号116(例如,(α、β)固定正交参考系中的定子矢量电压的分量)。而且,脉冲生成 电路117包含pwm控制器118、栅极驱动器122及3相逆变器126。作为系统200的 控制回路的部分,与在ipd间隔期间注入到电机130中的相电流脉冲相关的时序参数使 用感测电路204获得。在图2的实例中,感测电路204被表示为具有ipd逻辑206(图1 中的ipd逻辑106的实例)、上升时间逻辑208(图1中的上升时间逻辑108的实例)、下 降时间逻辑210(图1中的下降时间逻辑110的实例)、模数转换器(adc)212及处理器 214。在一些实例实施例中,ipd逻辑206包含电流感测电路及/或其它组件以测量在ipd 间隔期间注入的相电流脉冲(例如,及)。上升时间逻辑 208经配置以获得在ipd间隔期间注入到电机130中的一或多个相电流脉冲的上升时间 参数。在一些实例实施例中,上升时间逻辑208包含具有下限及上限的比较器(例如,图 4c中的比较器431)。上升时间逻辑208还包含时钟电路系统及经配置以基于比较器的 输出存储时钟计数的存储装置(例如,寄存器)。下降时间逻辑210经配置以获得在ipd 间隔期间注入到电机130中的一或多个相电流脉冲的下降时间参数。在一些实例实施例 中,下降时间逻辑210包含具有下限及上限的比较器。下降时间逻辑210还包含时钟电 路系统及经配置以基于比较器的输出存储时钟计数的存储装置(例如,寄存器)。

27.在一些实例实施例中,使用adc 212来将由ipd逻辑206获得的电流感测测量转 换为离散数字值。作为另一选项,比较adc 212的输出与下限及上限(执行数字比较而 非模拟比较以确定上升时间值及下降时间值)。在此类实施例中,上升时间逻辑208及下 降时间逻辑210经配置以基于数字比较器的输出测量及存储时钟计数。

28.在一些实例实施例中,处理器214经配置以基于电流测量、上升时间值及下降时间 值估计电机130的r及l值。在此类实施例中,将经估计r及l值提供到处理器220 以用于确定转子位置(例如,bemf观测器226可将r及l值用作无传感器foc算法的 部分)。在一些实例实施例中,处理器214与处理器220分离。在其它实例中,处理器 214及处理器220对应于一个处理器。通过如本文中所描述般估计r及l,可避免使用 外部仪器来测量r及l。

29.图3a是表示根据实例实施例的逆变器电路(例如,图1及2中的3相逆变器126)及 电机302(图1及2中的电机130的实例)的组件的图。图3a的逆变器电路对应于呈所 展示布置的晶体管q1到q6。更具体来说,q1及q2的电流端子串联耦合在电源电压 (v

dd

)节点与接地节点之间。q1与q2之间的节点304经耦合到电机302的u相,其中 u相包含对应于电机的定子组件的电阻(r)及电感(l)。而且,q3及q4的电流端子串联 耦合在v

dd

节点与接地节点之间。q3与q4之间的节点306经耦合到电机302的v相, 其中v相包含对应于电机302的定子组件的电阻(r)及电感(l)。而且,q5及q6的电流 端子串联耦合在v

dd

节点与接地节点之间。q5与q6之间的节点308经耦合到电机302 的w相,其中w相包含对应于电机的定子组件的电阻(r)及电感(l)。

30.利用图3a中所表示的布置,不同相电流脉冲是可能的。更具体来说,不同相电流 脉冲包含及其中通过驱动图3a中所表示的q1到q6 的不同组合来获得每一相电流脉冲。在所提出实例中,使用在ipd间隔期间的一或多个 相电流脉冲(例如及)的时序参数来确定电机(例如电机302) 的r及l值。

31.图3b是根据一些实例的用于分析负载电流(i

l

(t))的电阻器

‑

电感器(rl)电路310的 图。如所展示,rl电路310被表示为电压源312、开关314、电阻器(r)及电感器(l)。 当开关314在t=0闭合时,电流是i

l

(t)且跨l的电压是v

l

。在一些实例实施例中,通过 采用基尔霍夫电流定律来确定i

l

(t),从而得到:

[0032][0033][0034]

对于

[0035]

对于i

l

(0)=0,其中τ=l/r=时间常数

[0036][0037][0038]

其中i1是电流下限,i2是电流上限,v是3相逆变器电源电压,r是u相与v相之间的 电机电阻值,t1是电流上升时间值,t2是电流下降时间值,且l是u相与v相之间的 电机电感值。在一些实例实施例中,方程式1及2用于估计r及l值,其中经估计r及 l值在所要准确度内,这是因为t1的值(例如,从图1中的上升时间逻辑108或图2中 的上升时间逻辑208获得)及t2(例如,从图1中的下降时间逻辑110或图2中的下降 时间逻辑210获得)足够准确。

[0039]

图4a是根据实例实施例的相电流及转子位置的矢量表示的图400。在图400中, 及的相电流脉冲连同脉冲持续时间信息一起表示。在图 4a的实例中,最短脉冲对应于其中最短脉冲对应于最接近的转子位置,其中在图 400

的矢量表示410中描述转子位置。

[0040]

图4b是根据实例实施例的与获得相电流上升时间及下降时间值相关的波形的时序 图420。在时序图420中,表示各种波形,包含ipd开始波形、pwm_uhs_on波形、 pwm_uls_on波形、pwm_vls_on波形、v相电流(i

v

)波形、ipd_comp_out波形 及dly_counter波形。ipd开始波形是ipd脉冲的ipd起始信号。pwm_uhs_on 波形是驱动u相开关的u高侧导通信号(例如,q1导通)。pwm_uls_on波形是驱动 u相开关的u低侧导通信号(例如,q2导通)。pwm_vls_on波形是驱动v相开关的 v低侧导通信号(例如,q4导通)。v相电流波形是指示由于经注入ipd脉冲所致的 v相电流的感测电流值。

[0041]

如所展示,v相电流波形从vref/2值(零电流,加偏压到中间值)渐变越过下限及 上限直到超过上限的点401为止。vph电流波形从点421渐变越过上限及下限到vref/2 值。在图4b的实例中,下限从vref/2值偏移达一定量。一旦下限被vph电流达到且 在比较器延迟(td)之后,就将比较器输入阈值更改为上限。由于如由ipd_comp_out 波形所表示的间隔422内的比较器延迟,比较器输出保持为高。从vph电流横穿下限 及比较器(td)的延迟到vph电流横穿上限及比较器(td)的延迟的持续时间被测量为t1 计数。一旦上限被vph电流达到且在比较器延迟(td)之后,就将pwm_uhs_on变为 低。vph电流开始衰减且比较器输出保持为高直到电流下降到上限以下且如由 ipd_comp_out波形所表示的间隔426内的比较器延迟(td)之后为止。一旦上限被vph 电流从点421沿另一方向达到且在比较器延迟(td)之后,就将比较器输入阈值更改为下 限。比较器输出在如由ipd_comp_out波形所表示的间隔428内变为低。一旦间隔428 完成,比较器输出就在间隔429内变为高直到当vph电流达到下限时且在如由 ipd_comp_out波形所表示的比较器延迟(td)之后变为低为止。

[0042]

在一些实例实施例中,使用vph_current(来自电流感测电路)、ipd_comp_out (来自具有下限及上限的比较器)及相关时序逻辑组件跟踪上升时间值(t1)及下降时间值 (t2)。图4c是展示根据实例实施例的用于获得电流上升时间及下降时间值的时序逻辑 430(图1及2中的上升时间逻辑108、208及下降时间逻辑110、210的实例)的框图。 在图4c的实例中,时序逻辑430包含经配置以比较vph_current与上限及下限的比 较器431,相应寄存器432、434,及用于存储表示t1及t2的时钟计数的时钟436、438。 在所提出实例中,使用下限及上限进行比较器操作解决比较器延迟,从而得到更准确的 上升时间及下降时间值。

[0043]

在一些实例实施例中,基于电流感测电路准确性选择下限。低于下限时,假定电流 感测放大器输出未准确地表示流动通过所述相的电流。而且,上限是基于包含以下项的 准则来确定:1)电流比较器生成足够宽的脉冲用于时序测量;2)上限在ipd期间产生低 声学噪声(例如,小于目标水平);及3)上限在ipd期间未引起转子移动。

[0044]

利用时序逻辑430,存在上升及下降时间的改进准确性,这有助于确保基于上升及 下降时间的r及l估计足够准确以用于转子位置估计中。在替代实施例中,使用两个单 独比较器,其中一个比较器使用下限且另一比较器使用上限。另一选项是数字化电流感 测测量,且使用下限及上限在数字域中执行比较。

[0045]

图5a及5b是展示根据图4b的时序图420的通过电机的相电流的图500及520。 在图500中,在所展示布置中,电机(例如,图1及2中的电机130)被表示为电感器(l

u

、 l

v

、l

w

)且3相逆变器(例如,图1及2中的3相逆变器126)被表示为呈所展示配置的开 关q1到q6。更具体来说,q1及q2的电流端子串联耦合在电压电源502与接地节点 504之间。q1与q2之间的节点

508经耦合到电机302的l

u

。而且,q3及q4的电流 端子串联耦合在电压电源502与接地节点504之间。q3与q4之间的节点510经耦合到 电机302的l

v

。而且,q5及q6的电流端子串联耦合在电压电源502与接地节点504 之间。q5与q6之间的节点512经耦合到l

w

。在图5a的图500中,q1及q4导通, 而q2、q3、q5及q6关断,从而得到在如本文中所描述的ipd间隔期间的通过电机的 电流506及t1的测量(参见,例如图4b)。在图5b的图520中,q2及q4导通,而q1、 q3、q5及q6关断,从而得到在如本文中所描述的ipd间隔期间的通过电机的电流516 及t2的测量(参见,例如图4b)。

[0046]

图6a到6c是根据一些实例的展示通过电机的其它相电流的图600、610及620。 在图6a的图600中,电机(例如,图1及2中的电机130)被表示为l

u

、l

v

、l

w

且3相 逆变器(例如,图1及2中的3相逆变器126)被表示为呈图5a及5b中所展示的相同布 置的q1到q6。在图6a的图600中,q1及q4导通,而q2、q3、q5及q6关断,从 而得到通过电机的电流606。在图6b的图610中,q2及q6导通,而q1、q4、q5及 q6关断,从而得到通过电机的电流616。在图6c的图620中,q2、q3及q5导通,而 q1、q4及q6关断,从而得到通过电机的电流626a及626b。利用图600、610及620 中所表示的电流606、616、626a,626b,将更新用于估计电机的r及l的感测操作及 计算以将时序信息用于可用电流。

[0047]

图7是展示根据一些实例的方法700的流程图。如所展示,方法700包括在框702 处在ipd间隔期间将相电流注入到电机中。在框704处,(例如,使用图1中的感测电 路104或图2中的感测电路204)基于经注入相电流脉冲测量下限与上限之间的电流上升 时间。在框706处,(例如,使用图1中的感测电路104或图2中的感测电路204)基于 经注入相电流脉冲测量上限与下限之间的电流下降时间。在框708处,(例如,使用图1 中的位置分析器112,或图2中的处理器214或220)基于经测量电流上升时间及电流下 降时间(例如,使用方程式1及2,其中t1是经测量电流上升时间且t2是经测量电流下 降时间)计算电机r及l值。在框710处,基于电机的经估计r及l值确定转子位置。 在框712处,基于经确定转子位置将控制信号(例如,(α、β)固定正交参考系中的定子矢 量电压的分量)提供到pwm信号生成器。在框714处,基于控制信号生成pwm信号。 在框716处,基于pwm信号生成栅极驱动信号以控制3相逆变器的开关且将电流提供 到电机。

[0048]

在一些实例实施例中,在框712处确定的控制信号(例如,控制信号116)是(α、β)固 定正交参考系中的定子矢量电压的分量。这些控制信号是到pwm生成器(例如,空间矢 量pwm生成器)的输入。在框714处生成的pwm信号用于控制施加到电机的电压及电 流的频率及量值两者。因此,与固定频率电机驱动器相比,pwm逆变器供电的电机驱 动器提供更好的效率及更高的性能。pwm逆变器(例如,3相逆变器126)递送到电机的 能量由在框714处生成的pwm信号(例如,pwm信号120)控制,所述pwm信号确定 驱动信号(例如,驱动信号124)到pwm逆变器的功率晶体管的栅极的时序。在不同实例 实施例中,不同pwm技术(确定调制信号及从调制信号确定开关导通/开关关断时刻的 方式)是可能的。可用选项包含正弦波pwm、磁滞pwm及相对新的空间矢量(sv)pwm。

[0049]

典型的三相逆变器基于驱动信号a、a’、b、b’、c及c’控制六个功率晶体管(q1到 q6)以提供三个输出电压(va、vb及vc)。具体来说,a是高侧开关q1的驱动信号,a’是 低侧开关q2的驱动信号,b是高侧开关q3的驱动信号,b’是低侧开关q4的驱动信号, c是高侧开关q5的驱动信号,c’是低侧开关q6的驱动信号。当高侧晶体管接通时(即, 当a、b或c是1时),

电机的电感值。

[0059]

在一些实例实施例中,系统(例如,图1中的系统100或图2a及2b中的系统200) 包含:电机(例如,图1及2b中的电机130),其具有定子及转子;及脉冲生成电路(例 如,图1及2b中的脉冲生成器电路117),其经耦合到定子。所述系统还包含耦合到脉 冲生成电路的电机控制器(例如,图1中的电机控制器102,或图2a及2b中的处理器 214及220)。电机控制器经配置以基于在ipd间隔期间获得的时序参数(例如,图1中的 值113,或图4b中的t1及t2)确定电机的电感及电阻值(例如,本文中的r及l)。电 机控制器还经配置以基于经确定电感及电阻值确定转子位置(例如,图1中的转子位置 115)。电机控制器还经配置以基于经确定转子位置生成用于脉冲生成电路的控制信号(例 如,图1及2b中的控制信号116)。

[0060]

在一些实例实施例中,电机控制器包括经配置以测量由于在ipd间隔期间注入的不 同相电流所致的在下限与上限之间的电流上升时间及下降时间的时序逻辑(例如,图1中 的上升时间逻辑108、图1中的下降时间逻辑110、图2b中的上升时间逻辑208、图2b 中的下降时间逻辑210)。在一些实例实施例中,不同相电流仅包含两个相电流,且其中 电流上升时间及电流下降时间用作用于确定电机的电感及电阻值的时序参数。在一些实 例实施例中,不同相电流包含三相电流,且其中电流上升时间及电流下降时间用作用于 确定电机的电感及电阻值的时序参数。

[0061]

在一些实例实施例中,时序逻辑包括经配置以接收感测信号(例如,图4b中的 vph_current)且比较感测信号与下限及上限的比较器(例如,图4c中的比较器431)。 在一些实例实施例中,时序逻辑还包含耦合到比较器的输出的时钟(例如,图4c中的t1 时钟436或t2时钟438)。在一些实例实施例中,时序逻辑还包含耦合到时钟且经配置 以基于比较器的输出存储电流上升时间值(例如,t1)及电流下降时间值(例如,t2)的寄 存器(例如,图4c中的t1寄存器432或t2寄存器434)。时序逻辑在经存储电流上升时 间值及经存储电流下降时间值中解决由于比较器所致的延迟。在一些实例实施例中,基 于电流下限(例如,方程式1中的i1)、电流上限(例如,方程式2中的i2)、电流上升时间 (例如,t1)、电流下降时间值(例如,t2)、电机的电阻值(例如,依图1中的值114的r) 与电机的电感值(例如,依图1的值114的l)之间的关系确定电机的电感及电阻值。在 一些实例实施例中,所述关系被给出为:及其中i1是电流下限值,i2是电流上限值,v是3相逆变器的电源,r是电机的电阻值,t1 是电流上升时间值,t2是电流下降时间值,且l是电机的电感值。

[0062]

利用所提出解决方案,使用在ipd间隔期间注入的相电流脉冲的时序参数来实现电 机r及l值的准确测量。不需要单独的硬件,这是因为使用现存ipd分析组件来测量 时序参数。更具体地说,取代仅测量ipd分析期间的相电流值,还测量至少一个相电流 脉冲的上升时间值(t1)及下降时间值(t2)。使用t1及t2值来准确地估计电机的r及l 值,接着使用所述r及l值(例如,通过无传感器foc算法)来确定转子位置。

[0063]

在一些实例实施例中,电机控制器装置(例如,图1中的电机控制器102)包含处理 器(图1中的位置分析器112、图2a及2b中的处理器214、220)及耦合到处理器的感测 电路(例如,图1中的感测电路104或图2b中的感测电路204)。感测电路包含第一相电 流感测电路(例如,图2中的第一电流感测电路205a)及第二相电流感测电路(例如,图2 中的第二电

流感测电路205b)。感测电路还包含耦合到第一及第二相电流感测电路的时 序电路(例如,图2b中的上升时间逻辑208及下降时间逻辑210),其中所述时序电路经 配置以测量由于在ipd间隔期间由第一及第二相电流感测电路感测到的不同相电流所 致的电流上升时间(例如,图4b中的t1)及下降时间(例如,图4b中的t2)。处理器经配 置以基于经测量电流上升时间及下降时间确定电机的电感及电阻值(例如,图1中的r 及l值114),且其中处理器经配置以基于经确定电感及电阻值提供控制信号(例如,图1 及2b中的控制信号116)。

[0064]

在一些实例实施例中,处理器使用无传感器foc算法来基于经确定电感及电阻值 确定转子位置,且其中经确定转子位置用于生成控制信号。在一些实例实施例中,不同 相电流包含由第一及第二相电流感测电路感测到的两个相电流(例如,u及v相),且其 中时序电路包括经配置以比较每一经感测相电流与下限及上限(例如,参见图4b中的下 限及上限)的比较器(例如,图4c中的比较器431)。时序逻辑还包含耦合到比较器的输 出的时钟(例如,ti时钟436或t2时钟438)。时序逻辑还包含耦合到时钟且经配置以基 于比较器的输出存储电流上升时间值及电流下降时间值的寄存器(例如,图4c中的t1 寄存器432或t2寄存器434)。在一些实例实施例中,时序逻辑在经存储电流上升时间 值及经存储电流下降时间值中解决由于比较器所致的延迟。

[0065]

在一些实例实施例中,感测电路进一步包括第三相电流感测电路(例如,以感测图1 中所表示的i

w

),其中时序电路包括经配置以比较每一经感测相电流与下限及上限的比 较器(例如,图4c中的比较器431)。

[0066]

在一些实例实施例中,处理器经配置以基于电流下限(例如,方程式1中的i1)、电 流上限(例如,方程式2中的i2)、电流上升时间值(例如,t1)、电流下降时间值(例如, t2)、电机的电阻值(例如,依图1中的值114的r)与电机的电感值(例如,依图1的值 114的l)之间的关系确定电机的电感及电阻值。在一些实例实施例中,所述关系被给出 为:及其中i1是电流下限值,i2是电流上限 值,v是3相逆变器电源电压,r是电机的电阻值,t1是电流上升时间值,t2是电流 下降时间值,且l是电机的电感值。

[0067]

贯穿本描述及权利要求书已使用某些术语来指代特定系统组件。如所属领域的技术 人员将明白,不同方可通过不同名称来指代组件。本文献并非意在区分仅在名称不同但 在其相应功能或结构上相同的组件。在本公开及权利要求书中,术语“包含”及“包括

”ꢀ

以开放式方式使用,且因此应被解释为意指“包含但不限于

…”

。

[0068]

贯穿说明书使用术语“耦合”。所述术语可涵盖实现与本公开的描述一致的功能关 系的连接、通信或信号路径。例如,如果装置a生成用于控制装置b以执行动作的信 号,那么在第一实例中,装置a通过直接连接耦合到装置b,或在第二实例中,装置a 通过中介组件c耦合到装置b,前提是中介组件c未改变装置a与装置b之间的功能 关系,使得由装置a经由由装置a生成的控制信号控制装置b。

[0069]

以上论述意在说明本发明的原理及各种实施例。一旦完全明白以上公开,许多变型 及修改对于所属领域的技术人员将变得显而易见。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。