1.本发明涉及集成电路技术领域,尤其涉及一种快速自动频率校准装置及方法。

背景技术:

2.频率合成器(fs,frequency synthesizer)是现代无线收发器中一个非常重要的模块,如图1a所示为fs的基本结构示意图,包括锁相环(pll,phase locked loop)结构1、电容阵列2和频率校准模块3,pll结构1主要由鉴频鉴相器pfd(phase frequency detector)11、电荷泵cp(charge pump)12、环路滤波器lpf(low pass filter)13、分频器(divider)14和压控振荡器vco(voltage controlled oscillator)15组成。

3.为了保证电源电压温度(pvt,power voltage temperature)变化时具有较强的鲁棒性,通常要求fs输出较宽的频率范围,这就意味着片上vco需具有较宽的调谐范围。而vco的宽带调谐范围一般是通过固定电感调整电容阵列2得到,比如采用2进制权重形式的电容阵列,通过调整接入的电容大小获得宽带调谐范围。这样,vco的调谐特性曲线就会有多条子带。

4.在快速跳频通信系统中,如军事雷达,fs切换频率时,需要快速的找到合适的子带以满足通信系统的锁定时间要求。同时,vco子带之间一般会有一定比例的交叠,而由于vco调谐增益及cp输出电压的非线性,当fs锁定在vco子带二端时相位噪声一般较差,因此最好是将fs锁定在子带中间位置。为了快速准确的选择合适的子带,就需要用到自动频率校准(afc,automatic frequency calibration)电路。现有的频率校准方案一般可以分为两种,一种是基于控制电压的闭环校准方案,另一种是基于计数形式的开环校准方案。

5.基于控制电压的闭环校准方案,采用如图1b所示的电路结构,通过设置vco的控制字,在闭环状态下判断vco控制电压是否落入设定的范围来确定所设置的vco控制字是否合适。该方案由于工作在闭环模式下,因此每次环路锁定需要较长时间,这个时间根据环路带宽而定,通常是几十us甚至上百us,如果vco子带很多,那么整个afc的校准时间将会很长,可能达到ms级别,这在快速跳频系统中是不可接受的。

6.基于计数形式的开环校准方案,采用如图1c所示的电路结构,在一个固定的时间窗口中对参考频率信号f

ref

和vco的输出频率信号f

vco

同时进行计数,根据计数的结果来判断当前vco的输出频率,从而对vco输出频带进行调整。该方案在进行计数时是基于开环结构,因此稳定时间较快。现在fs中一般都采用这种方法。但是由于计数器只能计算整数个周期,而vco频带间有时候频率间隔很小,所对应的整数分频比相差可能小于1,因此为了正确区分子带,只能通过增加计数窗口的时间来保证准确性,需要在一个较长时间内进行计数,这样就增加了afc的校准时间,在快速跳频系统中也是难以接受的。

技术实现要素:

7.本发明针对现有技术中自动频率校准方案校准时间长(几十上百微秒),无法满足高性能快速校准系统的应用要求的技术问题,提供了一种新的技术来提高频率校准速度,

降低校准时间。

8.一方面,本发明提供了一种快速自动频率校准装置,包括:

9.全局时钟产生电路,包括:第一输入端和第二输入端;所述第一输入端与压控振荡器连接,用于输入vco频率信号;所述第二输入端与参考信号源连接,用于输入参考频率信号;通过控制vco频率信号对参考频率信号过采样,获取全局时钟信号;

10.整数周期计算单元,包括:第三输入端和第四输入端;所述第三输入端与所述压控振荡器连接,用于输入vco频率信号;所述第四输入端与所述全局时钟产生电路连接,用于输入所述全局时钟信号;通过对所述vco频率信号和所述全局时钟信号进行处理,获取参考频率信号周期内vco频率信号的整数周期个数;

11.反相延迟采样电路,包括:第五输入端和第六输入端;所述第五输入端与压控振荡器连接,用于输入vco频率信号;所述第六输入端与参考信号源连接,用于输入参考频率信号;通过对vco频率信号进行多次反相延迟处理,获得反相延迟信号,并通过所述参考频率信号对所述反相延迟信号进行采样,获得采样信号;

12.小数周期计算单元,与所述反相延迟采样电路的输出端相连,用于基于所述采样信号计算参考频率信号与其后面邻近的vco频率信号上升沿之间的差值,并基于所述差值确定参考频率信号周期内vco频率信号的小数周期个数;

13.加法器,与所述整数周期计算单元和所述小数周期计算单元的输出端相连,用于将所述整数周期个数和所述小数周期个数进行相加处理,获得参考频率信号周期内vco频率信号的完整周期个数;

14.数字控制逻辑电路,与所述加法器相连,用于基于所述完整周期个数生成控制逻辑字,以控制校准压控振荡器的输出频率。

15.可选的,所述整数周期计算单元,还包括:

16.第一计数器,用于在参考频率信号周期内、在vco频率信号的上升沿的触发下进行累加计数,获取多个第一计数值;

17.第一计数输出单元,用于在所述全局时钟信号的控制下输出多个第一计数值;

18.第一计算单元,用于基于多个第一计数值计算参考频率信号周期内vco频率信号的整数周期个数。

19.可选的,所述第一计数器的工作频率为ghz级别,所述第一计数器包含多级异步计数器和多级同步计数器。

20.可选的,所述反相延迟采样电路,还包括:

21.反相延迟单元,用于对vco频率信号进行多次反相延迟处理,获得反相延迟信号;

22.采样单元,用于控制参考频率信号对所述反相延迟信号进行采样,获得采样信号。

23.可选的,所述反相延迟单元包含m个反相器,m为正整数,m≥tvco/tinv;

24.其中,tvco为vco频率信号周期时间,tinv为反相器的延迟时间。

25.可选的,所述小数周期计算单元,包括:

26.第二计数器,用于在vco频率信号周期内、在参考频率信号的上升沿的触发下进行累加计数,获取多个第二计数值;

27.第二计算单元,用于获取多个第二计数值分别对应的多组采样信号,并基于多组采样信号计算参考频率信号与其后面邻近的vco频率信号上升沿之间的差值,并基于所述

差值确定参考频率信号周期内vco频率信号的小数周期个数。

28.可选的,所述全局时钟信号用于对所述整数周期计算单元和所述小数周期计算单元中的计数器进行同步。

29.另一方面,本发明还提供了一种快速自动频率校准方法,包括如下步骤:

30.通过控制vco频率信号对参考频率信号过采样,获取全局时钟信号;

31.通过对所述vco频率信号和所述全局时钟信号进行处理,获取参考频率信号周期内vco频率信号的整数周期个数;

32.通过对vco频率信号进行多次反相延迟处理,获得反相延迟信号,并通过所述参考频率信号对所述反相延迟信号进行采样,获得采样信号;

33.基于所述采样信号计算参考频率信号与其后面邻近的vco频率信号上升沿之间的差值,并基于所述差值确定参考频率信号周期内vco频率信号的小数周期个数;

34.将所述整数周期个数和所述小数周期个数进行相加处理,获得参考频率信号周期内vco频率信号的完整周期个数;

35.基于所述完整周期个数生成控制逻辑字,以控制校准压控振荡器的输出频率。

36.可选的,所述通过对vco频率信号进行多次反相延迟处理,获得反相延迟信号,具体为:

37.通过对vco频率信号进行m次反相延迟处理,获得反相延迟信号;其中,m为正整数,m≥tvco/tinv;其中,tvco为vco频率信号周期时间,tinv为反相器的延迟时间。

38.可选的,所述基于所述采样信号计算参考频率信号与其后面邻近的vco频率信号上升沿之间的差值,并基于所述差值确定参考频率信号周期内vco频率信号的小数周期个数,具体包括:

39.在vco频率信号周期内、在参考频率信号的上升沿的触发下进行累加计数,获取多个第二计数值;

40.获取多个第二计数值分别对应的多组采样信号,并基于多组采样信号计算参考频率信号与其后面邻近的vco频率信号上升沿之间的差值,并基于所述差值确定参考频率信号周期内vco频率信号的小数周期个数。

41.本发明中提供的一个或多个技术方案,至少具有如下技术效果或优点:

42.本发明快速自动频率校准方案采用整数周期计算单元和小数周期计算单元分别对参考频率信号周期内vco频率信号的整数周期个数和小数周期个数进行计数,其中在进行小数周期计数时,通过反相延迟采样电路对vco频率信号进行多次反相延迟处理,并通过所述参考频率信号对所述反相延迟信号进行采样,获得采样信号,进而基于所述采样信号计算参考频率信号与其后面邻近的vco频率信号上升沿之间的差值,并基于所述差值确定参考频率信号周期内vco频率信号的小数周期个数;整数周期个数和小数周期个数相加,能够快速且准确地获取参考频率信号周期内vco频率信号的完整周期个数,即准确且快速地获取vco频率信号的当前输出频率,以准确地生成控制逻辑字控制校准压控振荡器的输出频率。有效地降低了校准时间,校准时间降低至2us以内,具有很明显的改善效果能够满足高性能快速校准系统的应用要求。

附图说明

43.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其它的附图。

44.图1a为本发明背景技术提供的一种现有频率合成器的基本结构示意图;

45.图1b为本发明背景技术提供的基于控制电压的闭环校准方案的结构示意图;

46.图1c为本发明背景技术提供的基于计数形式的开环校准方案的结构示意图;

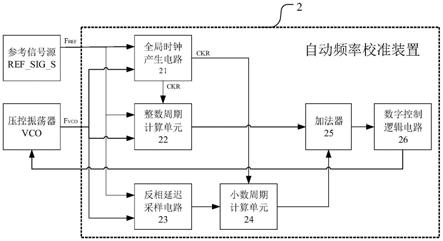

47.图2a为本发明实施例提供的一种快速自动频率校准装置结构示意图;

48.图2b为本发明实施例提供的另一种快速自动频率校准装置结构示意图;

49.图3a为本发明实施例提供的全局时钟产生电路硬件实现图;

50.图3b为本发明实施例提供的全局时钟产生电路产生全局时钟的波形图;

51.图4为本发明实施例提供的压控振荡器输出频率信号、参考频率信号和全局时钟信号的瞬态时序关系图;

52.图5a为本发明实施例提供的参考频率信号f

ref

上升沿与其前一个vco输出频率f

vco

的上升沿临近情况下的误差示意图;

53.图5b为本发明实施例提供的参考频率信号f

ref

上升沿与其前一个vco输出频率f

vco

的下降沿临近情况下的误差示意图;

54.图6为本发明实施例提供的vco输出频率f

vco

经过延迟链结构的时间数据转换器延迟处理的时序图;

55.图7为本发明实施例提供的一种快速自动频率校准装置应用于频率合成器中的整体方案图;

56.图8为本发明实施例提供的一种快速自动频率校准装置的校准时间仿真图。

具体实施方式

57.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对照附图说明本发明的具体实施方式。显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图,并获得其它的实施方式。

58.为使图面简洁,各图中只示意性地表示出了与本发明相关的部分,它们并不代表其作为产品的实际结构。另外,以使图面简洁便于理解,在有些图中具有相同结构或功能的部件,仅示意性地绘示了其中的一个,或仅标出了其中的一个。在本文中,“一个”不仅表示“仅此一个”,也可以表示“多于一个”的情形。

59.下面以具体实施例详细介绍本发明的技术方案。

60.实施例一

61.请参考图2a,本技术实施例提供的一种快速自动频率校准装置2,包括:

62.全局时钟产生电路21,包括:第一输入端和第二输入端;所述第一输入端与压控振荡器vco连接,用于输入vco频率信号fvco;所述第二输入端与参考信号源ref_sig_s连接,用于输入参考频率信号f

ref

;通过控制vco频率信号fvco对参考频率信号f

ref

进行采样,获取

全局时钟信号ckr;其中,全局时钟信号ckr用于对整数周期计算单元22和小数周期计算单元24中的计数器进行同步。

63.整数周期计算单元22,包括:第三输入端和第四输入端;所述第三输入端与所述压控振荡器vco连接,用于输入vco频率信号fvco;所述第四输入端与全局时钟产生电路21连接,用于输入全局时钟信号ckr;通过对vco频率信号fvco和全局时钟信号ckr进行处理,获取参考频率信号f

ref

周期内vco频率信号fvco的整数周期个数;

64.反相延迟采样电路23,包括:第五输入端和第六输入端;所述第五输入端与压控振荡器vco连接,用于输入vco频率信号fvco;所述第六输入端与参考信号源ref_sig_s连接,用于输入参考频率信号f

ref

;通过对vco频率信号fvco进行多次反相延迟处理,获得反相延迟信号,并通过参考频率信号f

ref

对所述反相延迟信号进行采样,获得采样信号;

65.小数周期计算单元24,与反相延迟采样电路23的输出端相连,用于基于所述采样信号计算参考频率信号f

ref

与其后面邻近的vco频率信号fvco上升沿之间的差值,并基于所述差值确定参考频率信号f

ref

周期内vco频率信号fvco的小数周期个数;

66.加法器25,与整数周期计算单元22和小数周期计算单元24的输出端相连,用于将所述整数周期个数和所述小数周期个数进行相加处理,获得参考频率信号f

ref

周期内vco频率信号fvco的完整周期个数;

67.数字控制逻辑电路26,与加法器25相连,用于基于所述完整周期个数生成控制逻辑字,以控制校准压控振荡器vco的输出频率。

68.在本实施例中,仍请参考图2a,快速自动频率校准装置用于频率合成器fs中对压控振荡器vco的输出频率进行快速校准,vco校准后的输出频率作为fs的最终输出频率。

69.本方案将数字电路的思想应用于fs模拟电路。通过计数将数字转换为时间是本方案的关键。在整数周期计算单元22和小数周期计算单元24分别设置有计数器,由于两个计数器的时钟不同步,计算结果可能不准,因此需要对时钟同步,形成全局时钟。全局时钟产生电路21如图3a和图3b所示,通过vco输出频率信号fvco对参考频率信号f

ref

过采样得到。

70.计算所述整数周期个数的原理:在每个vco输出频率信号fvco上升沿到来的时刻,整数周期计算单元22的计数器加1,计数结果在全局时钟信号ckr上升沿到来时输出,用n表示,如图4所示。前后二次计数之差表示在一个f

ref

周期内fvco输出的整数周期个数。

71.在具体实施过程中,请参考图2b,整数周期计算单元22,包括:

72.第一计数器221,用于在参考频率信号f

ref

周期内、在vco频率信号fvco的上升沿的触发下进行累加计数,获取多个第一计数值;

73.第一计数输出单元222,用于在全局时钟信号ckr的控制下输出多个第一计数值;

74.第一计算单元223,用于基于多个第一计数值计算参考频率信号f

ref

周期内vco频率信号fvco的整数周期个数。

75.在具体实施过程中,整数周期计算是通过高速计数器实现。由于需要计算一个f

ref

周期内fvco输出的整数周期个数,第一计数器221的工作频率为ghz级别。第一计数器221包含多级异步计数器和多级同步计数器,具体的,采用九级计数,在前三级计数器采用异步计数器,而后六级采用同步计数器。整数计数主要是模拟形式的d触发器链路,这里不再一一赘述。

76.在计算获得参考频率信号f

ref

周期内vco频率信号fvco的整数周期个数的同时,需

要计算小数周期个数,小数周期个数需要基于反相延迟采样电路23输出的采样信号计算获得,仍请参考图2b,反相延迟采样电路23,包括:

77.反相延迟单元231,用于对vco频率信号fvco进行多次反相延迟处理,获得反相延迟信号;

78.采样单元232,用于控制参考频率信号f

ref

对所述反相延迟信号进行采样,获得采样信号。

79.具体的,反相延迟单元231包含m个反相器:

80.m≥tvco/tinv

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(i)

81.其中,m为正整数,tvco为vco频率信号fvco周期时间,tinv为反相器的延迟时间。

82.仍请参考图2b,小数周期计算单元24,包括:

83.第二计数器241,用于在vco频率信号fvco周期内、在参考频率信号f

ref

的上升沿的触发下进行累加计数,获取多个第二计数值;

84.第二计算单元242,用于获取多个第二计数值分别对应的多组采样信号,并基于多组采样信号计算参考频率信号f

ref

与其后面邻近的vco频率信号fvco上升沿之间的差值,并基于所述差值确定参考频率信号f

ref

周期内vco频率信号fvco的小数周期个数。

85.具体的,如图4所示,在重定时之后,ckr与f

ref

之间会存在一定误差,而由于ckr是fvco过采样f

ref

得到的,因此ckr与f

ref

之间的误差也就是f

ref

与其后面邻近的fvco上升沿之间的误差ε,需要准确计算出该误差才能估计出当前分频比。误差估计方法如图5a-5b所示,图5a为参考频率信号f

ref

上升沿与其前一个vco输出频率fvco的上升沿临近的情况,图5b为参考频率信号f

ref

上升沿与其前一个vco输出频率fvco的下降沿临近的情况。

86.首先需要分别估计f

ref

上升沿与其前一个fvco上升沿和下降沿之间的延时差δt

r

和δt

f

,然后通过公式(ii)计算获得误差:

87.ε=1-δt

r

/t

v

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(ii)

88.其中t

v

=2|δt

r-δt

f

|。vco频率信号fvco经过一系列反相器延迟链后被f

ref

信号采样,通过采样结果中1-0及0-1的跳变位置可以得到δt

r

和δt

f

,进而通过上式计算出误差。

89.在具体实施过程中,反相延迟采样电路23可通过时间数据转换器(tdc,time to digital converter)实现,如图6所示,为延迟链结构的tdc的时序图,d(1)~d(8)为fvco的多个延迟信号。例如,在参考频率信号(f

ref

)的第10个时钟上升沿,采样得到的结果为10000111,则信号从1跳变到0发生在第一个bit,而从0跳变到1则发生在第五个bit,因此可以得到参考频率信号f

ref

落后其前面临近的fvco上升沿1个反相器延时t

inv

,而此时vco的频率周期为2*(5-1)=8个反相器延时(8*t

inv

),因此计算得到的相位误差ε[10]=1-t

inv

/(8*t

inv

)=7/8。通过tdc结合计数器的方法,可以在一个周期内就得到当前频率的准确值,因此可以快速的进行自动频率校准。同时,要求反相器的个数m满足式(i)的约束。

[0090]

进一步,将整数周期个数和小数周期个数结合起来,就可以得到一个参考周期(f

ref

)内vco的周期个数。

[0091]

结合图4和表1,为一个计数例子,f

ref

周期为2.6,f

vco

和f

ref

存在初始相位差ε,经过第一次重定时,f

ref

与f

vco

之间存在0.7的相位误差,第一次ckr上升沿时输出计数值c=1。第二次重定时,f

ref

与f

vco

之间存在0.1的相位误差,第二次ckr上升沿时输出c=3。通过计算:

[0092]

f

ref

[k]=c[k]-c[k-1] ε[k-1]-ε[k]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(iii)

[0093]

即可以得到瞬态分频比。每次输出结果如表1所示。也就是说,最多只需要二个参考信号周期,就可以精确计算得到此时的f

ref

与f

vco

分频比及f

vco

输出频率。

[0094]

表1每次ckr上升沿到来时各参数的值

[0095]

kε[k]c[k]f

ref

[k]10.71 20.132.630.562.640.992.650.3112.660.7142.6

[0096]

本方案自动频率校准装置应用于频率合成器的整体方案如图7所示,频率合成器包括锁相环回路(由鉴频鉴相器pfd、电荷泵cp、低通滤波器lpf、压控振荡器vco、分频器div组成)和本方案自动频率校准装置2,在进行校准时,环路断开,vco的输出频率信号f

vco

和参考频率信号f

ref

被送到自动频率校准装置2中,经过计算比较后输出控制逻辑调整字bn4<5:0>,对vco进行校准,校准后的vco的输出频率经后合成器输出本振信号lo,即为fs当前最终的输出频率。每次比较和计算一共耗费10个参考时钟周期,一共进行7次比较,因此可以大大缩小afc校准时间。仿真结果如图8所示,可以看到,从自动频率校准开始到结束,一共进行了7次比较,耗时1.4us。

[0097]

本方案技术效果主要是大大减小afc校准时间,传统的开环或者闭环校准需要几十上百微秒,但是采用本方案提出的基于tdc的afc方案,可以将校准时间降低至2us以内,具有很明显的改善效果。

[0098]

实施例二

[0099]

基于同一发明构思,本发明实施例还提供一种快速自动频率校准方法,包括如下步骤:

[0100]

通过控制vco频率信号fvco对参考频率信号f

ref

过采样,获取全局时钟信号ckr;

[0101]

通过对所述vco频率信号fvco和所述全局时钟信号ckr进行处理,获取参考频率信号f

ref

周期内vco频率信号fvco的整数周期个数;

[0102]

通过对vco频率信号fvco进行多次反相延迟处理,获得反相延迟信号,并通过所述参考频率信号f

ref

对所述反相延迟信号进行采样,获得采样信号;

[0103]

基于所述采样信号计算参考频率信号f

ref

与其后面邻近的vco频率信号fvco上升沿之间的差值,并基于所述差值确定参考频率信号f

ref

周期内vco频率信号fvco的小数周期个数;

[0104]

将所述整数周期个数和所述小数周期个数进行相加处理,获得参考频率信号f

ref

周期内vco频率信号fvco的完整周期个数;

[0105]

基于所述完整周期个数生成控制逻辑字,以控制校准压控振荡器vco的输出频率。

[0106]

进一步,所述通过对vco频率信号fvco进行多次反相延迟处理,获得反相延迟信号,具体为:

[0107]

通过对vco频率信号fvco进行m次反相延迟处理,获得反相延迟信号;其中,m为正

整数,m≥tvco/tinv;其中,tvco为vco频率信号fvco周期时间,tinv为反相器的延迟时间。

[0108]

在具体实施过程中,所述基于所述采样信号计算参考频率信号f

ref

与其后面邻近的vco频率信号fvco上升沿之间的差值,并基于所述差值确定参考频率信号f

ref

周期内vco频率信号fvco的小数周期个数,具体包括:

[0109]

在vco频率信号fvco周期内、在参考频率信号f

ref

的上升沿的触发下进行累加计数,获取多个第二计数值;

[0110]

获取多个第二计数值分别对应的多组采样信号,并基于多组采样信号计算参考频率信号f

ref

与其后面邻近的vco频率信号fvco上升沿之间的差值,并基于所述差值确定参考频率信号f

ref

周期内vco频率信号fvco的小数周期个数。

[0111]

根据上面的描述,上述快速自动频率校准方法应用于上述快速自动频率校准装置中,所以,该方法与上述装置的一个或多个实施例一致,在此就不再一一赘述了。

[0112]

尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例做出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

[0113]

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。