1.本发明涉及宽带无线通信数字信号处理领域,主要解决无线通信系统中由于模数转换器的时钟误差带来的最佳采样点偏离而引起的传输质量恶化问题。具体是一种根据接收信号进行模数转换器采样频率误差估计并在频域进行偿的方法,用于无线通信宽带数字信号处理。

背景技术:

2.由于模拟器件性能的局限性,无线通信接收机模拟数字转换器的时钟频率存在一定偏差,造成数字采样点不一定在符号峰值点上,从而造成接收端信噪比降低。此外,对于带限成型滤波的调制信号,采样时刻的偏差还会引入码间串扰,从而降低信噪比,在高阶调制下,这种情况更加严重。因此,精确的定时同步是可靠接收的基础,不能有效的进行定时同步,会引起接收机信噪比降低、误比特率升高,传输质量的恶化。

3.实现定时同步的方法一般有同源时钟法、数据辅助法和自同步三类法。同源时钟法即让收发时钟都同步到一个主时钟上,由主时钟提供一个精确的定时信号,接收端估计并补偿收发端的信号时延,但在实际中,由于发射机和接收机的使用场景和空间距离限制,不一定具备收发时钟同源的条件。数据辅助法在发送端周期性的插入一些特定的辅助数据,接收端利用这些信息提取出定时信息进行辅助同步。此外,在宽带并行架构的接收机中,进行数据辅助需要进行大量的运算,对接收机的时钟和计算资源需求也非常高。自同步法是通过对接收机收到的信息进行参数估计或环路滤波估计出定时误差,从而进行误差校正进行补偿。自同步法分为开环同步和闭环同步两类,开环同步适用于信噪比很大的场景。闭环同步的方法通过误差估计后反馈调整采样时钟或在数字域通过调整滤波器达到误差校正的目的。

4.oerder m和meyr h.在其1988年的论文《digital filter and square timing recovery》中给出了一种估计定时误差的方法,基于该方法清华大学林长贝博士提出了一种高速并行接架构下的定时误差补偿方法,但这种方法的收敛速度较慢,且在一定条件下存在收敛不稳定的情况。

技术实现要素:

5.为了克服现有技术的不足,本发明提供一种改进的宽带并行接收机定时同步方法。本发明的目的是针对无线通信宽带信号由于模拟数字转换器时钟偏差在接收端造成接收信号信噪比下降,从而带来的通信质量下降,提出一种并行架构下的定时误差估计和补偿方法。本专利基于此架构提出一种改进方法,重点是对环路滤波器系数做出了改进,从而改进收敛速率和收敛后的稳定性。

6.本发明解决其技术问题所采用的技术方案包括以下步骤:

7.步骤1,信号m和定时误差δ,初始化m=0,δ=0,滤波器的傅里叶点数为n,定时相位校正的滤波器系数初始化第1到位为1,到位为0,到n位为1;初始

化定时误差估计实部re=0,估计虚部xm=0,定时误差估计次数count=0,累积定时误差ε

sum

=0,环路滤波后定时误差ε=0,转到步骤2;

8.步骤2,用做完ifft后的32路i路数据和q路数据计算定时误差的实部re和虚部xm,计算后转到步骤3;

9.完成ifft后定时误差估计次数count加1;

10.步骤3,判断count是否为31,若count为31,count置为0,转到步骤4,否则令re=re

′

,xm=xm

′

,返回步骤2;

11.步骤4,计算定时误差相位角转到步骤5;

12.步骤5,进行环路滤波,设置环路滤波系数k1和k2;计算累积定时误差ε

sum

′

和环路滤波后定时误差ε,按照下式计算:

[0013][0014][0015]

转到步骤6;

[0016]

步骤6,判断ε当前取值,如果ε>1,则ε减1,令m=1;如果ε<

‑

1,则ε加1,且令m=

‑

1;其它情况下ε保持不变,m=0;判断之后转到步骤7;

[0017]

步骤7,修正定时相位校正滤波器系数,控制fifo输出;

[0018]

修正后的定时相位校正滤波器系数;如果m=1,则i路fifo和q路fifo进行下次输出时同时跳掉第一个采样点;如果m=

‑

1,则i路fifo和q路fifo进行下次输出时需要从上一次输出的最后一个采样点开始读取;如果m=0,则保持不变;完成后将m置为0,count置为0,re=re

′

,xm=xm

′

,ε

sum

=ε

′

sum

返回步骤2。

[0019]

所述步骤2中,实部re和虚部xm按照以下公式计算:

[0020][0021][0022]

其中re

′

为最终的实部,re为当前的估计实部,xm

′

为最终的虚部,xm为当前的估计虚部,i从0变到7,i和q的下标表示做完ifft后的路数索引。

[0023]

所述步骤4中,计算定时误差相位角的公式为:

[0024][0025]

其中arg(

·

)函数的取值范围为[

‑

π,π];

[0026]

所述设置环路滤波系数为

[0027]

所述步骤7中,修正后的定时相位校正滤波器系数第1到16位为e

j2πs(k

‑

1)/n

,其中,其中到位保持0不变,第到n位为其由

[0028]

本发明的有益效果在于采用通过接收数据进行定时误差估计,通过修正定时相位陵正滤波器系数补偿时钟误差带来的相位偏移,通过控制fifo输出修正时钟误差带来的频率偏移,通过这种方法解决模拟数字转换器时钟不准确带来的采样时刻偏移,信噪比降低,传输不可靠问题。具有如下优势:

[0029]

1)本发明采用的并行架构,更适合高速传输的宽带信号,本发明的方法通过修改也可用于串行架构的接收机。

[0030]

2)本发明中使用的环路滤波器系数k1和k2经过优化设计,使算法具有更快的收敛特性。

[0031]

3)本发明采用的修正定时相位校正滤波器系数经过优化设计,收敛后不容易失锁。

附图说明

[0032]

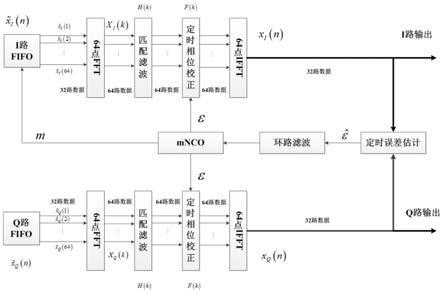

图1是本发明的宽带并行接收机定时同步方法信号处理架构图。

[0033]

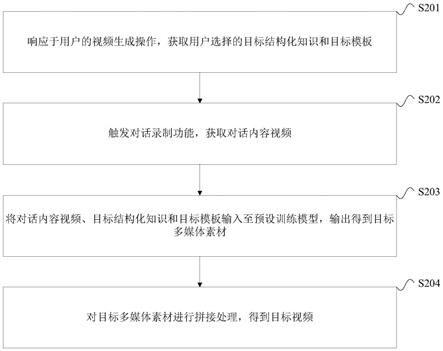

图2是本发明的环路滤波器计算流程图。

[0034]

图3是

‑

100ppm时钟失配情况下定时误差仿真图。

[0035]

图4是

‑

100ppm时钟失配情况下环路滤波器输出仿真图。

具体实施方式

[0036]

下面结合附图和实施例对本发明进一步说明。

[0037]

本发明在发射端采用4倍差值情况下,通过在接收端通过累积一定长度的采样信号通过om算法进行定时误差估计,再将估计结果反馈给前置fifo和定时相位校正滤波器,从而达到定时同步的目的。实现本发明的核心技术为确定fifo输出是否跳过当前信号或保留上一个采样点的信号m和定时误差δ。当m为1时,fifo需跳过第一个采样点再输出,当m为

‑

1时,fifo需将已输出的最后一个采样点再输出一次,当m为0,fifo正常输出采样点。信号并行路数为32,傅里叶变换和逆傅里叶变换点数为64。

[0038]

下面结合附图对本发明详细说明实施方式,实施例共4个,实施例1包含初始化及变量count不为31的情况,包含步骤1到步骤3。实施例2为count为31,需要进行定时误差估计和补偿,但定时误差ε介于

‑

1到1之间的情况。包含步骤4到步骤7。实施例3为count为31,需要进行定时误差估计和补偿,但定时误差ε小于

‑

1情况。包含步骤6到步骤7。

[0039]

实施例1

[0040]

步骤1,初始化m=0,δ=0,本例中匹配滤波器系数h(k),k=1,2,

…

64,为滚降系数为0.4的根升余弦滤波器,匹配滤波器系数h(k)是进行64点傅里叶变换的结果,为一个64位复数向量,在整个算法运行过程中保持不变。定时相位校正的滤波器初始化第1到16位为1,17到49位为0,50到64位为1。初始化定时误差估计实部re=0,虚部im=0,定时误差估计次数count=0,累积定时误差ε

sum

=0,环路滤波后定时误差ε=0。

[0041]

步骤2,从i路fifo和q路fifo各输出32个数据,采用重叠保留法或重叠相加法进行64位fft,得到64位fft后的结果x

i

(k)和x

q

(k)。将x

i

(k)和x

q

(k)分别和匹配滤波器系数h(k)

对位相乘。再将结果与定时相位误差校正滤波器对位相乘。最后采用重叠保留法或重叠相加法进行ifft,取前32位为定时误差输出,即:

[0042][0043][0044]

本发明针对的是8路并行4倍插值的接收机,x

i

(n)、x

q

(n)和一次对应32个数,h(k)和f(k)是64位的复数向量。

[0045]

利用ifft后的32路数据x

i

(n)和x

q

(n)计算计算定时误差的实部re和虚部xm。

[0046][0047][0048]

之后将变量count加1。

[0049]

步骤3,判断count的值是否为31,如果不是,则令re=re

′

,xm=xm

′

返回步骤2,i路fifo和q路fifo各自再输出32个数据并进行后续的操作,然后计算re

′

和xm

′

,直到count为31时转入才转入步骤4,这种情况在实施例2种介绍实施过程。

[0050]

实施例2:

[0051]

步骤4,计算定时误差相位角

[0052][0053]

假设count为31时,re=20.8,im=3.898,则定时误差相位角转到步骤5。

[0054]

步骤5,进行环路滤波,环路滤波系数累积定时误差ε

sum

和环路滤波后定时误差ε按照下式计算

[0055][0056][0057]

以为例,经过环路滤波后ε=

‑

0.0166。

[0058]

步骤6,判断ε是否大于1或小于

‑

1,如果ε>1,则ε=ε

‑

1,m=1;如果ε<

‑

1,则ε=ε 1,m=

‑

1;其它情况ε保持不变,m=0。由于ε=

‑

0.0166,故m=0,转到步骤7。

[0059]

步骤7,修正定时相位校正滤波器系数,控制fifo输出。

[0060]

修正后的定时相位校正滤波器系数第1到16位为e

j2πs(k

‑

1)/64

,其中k=1,2,

…

,16。17到49位保持0不变,第50到64位为e

‑

j2πs(64

‑

k 1)/64

,其中k=51,52,

…

,64,ε=

‑

0.0166情况下,修正后的滤波器系数如下表所示。由于m=0,不需要进行fifo输出的控制,则将count置为0,re=re

′

,xm=xm

′

,ε

sum

=ε

′

sum

,返回步骤2。

[0061]

[0062][0063]

实施例3:

[0064]

当经过步骤5定时误差计算,得到ε小于

‑

1时,以ε=

‑

1.0928为例。

[0065]

步骤6,判断ε是否大于1或小于

‑

1,如果ε>1,则ε=ε

‑

1,m=1;如果ε<

‑

1,则ε=ε 1,m=

‑

1;其它情况ε保持不变,m=0。由于ε=

‑

1.0928,故ε=

‑

1.0928 1=

‑

0.0928,m=

‑

1,转到步骤7。

[0066]

步骤7,修正定时相位校正滤波器系数,控制fifo输出。

[0067]

修正后的定时相位校正滤波器系数第1到16位为e

j2π(

‑

0.0928)(k

‑

1)/64

,其中k=1,2,

…

,16。17到49位保持0不变,第50到64位为e

‑

j2π(

‑

0.0928)(64

‑

k 1)/64

,其中k=51,52,

…

,64。由于m=

‑

1,i路和q路fifo需要将上一次已经输出的最后一个数据作为本次输出的第一个数据,其余数据依次后推,以i

‑1(n)表示前一次i路fifo输出的数据,n表示前一时刻数据在fifo中的位置,i0(n)表示fifo调整后需要输出的数据,不同变量m情况下,i0(n)对应关系如下表所示:

[0068]

[0069][0070]

[0071]

q路与i路相同。fifo控制后,将count置为0,返回步骤2。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。