技术特征:

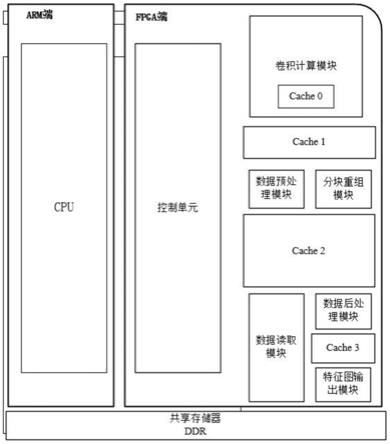

1.一种面向fpga的稀疏卷积神经网络多级存储计算系统,其特征在于,包括arm端和fpga端;所述arm端用于获取网络模型权重参数和输入特征图数据,根据所述网络模型权重参数和输入特征图数据的存储信息生成流程控制指令,并将所述流程控制指令发送到fpga端;所述fpga端接收到所述流程控制指令后,从所述arm端中读取所述网络模型权重参数和输入特征图数据,并进行计算,最后将计算结果反馈给所述arm端。2.如权利要求1所述的一种面向fpga的稀疏卷积神经网络多级存储计算系统,其特征在于,所述arm端包括片外存储器访问控制模块、ddr访问控制模块和流程控制模块;所述ddr访问控制模块内开辟有权重缓冲区和特征图缓冲区;所述片外存储器访问控制模块从片外存储器中将所述网络模型权重参数和输入特征图数据读入到所述ddr访问控制模块中;所述ddr访问控制模块将所述网络模型权重参数和输入特征图数据对应写入到所述权重缓冲区和特征图缓冲区;所述流程控制模块根据所述网络模型权重参数和输入特征图数据的存储信息生成流程控制指令,并将所述流程控制指令发送到fpga端。3.如权利要求2所述的一种面向fpga的稀疏卷积神经网络多级存储计算系统,其特征在于,所述fpga端包括控制模块、数据读取模块、数据预处理模块、卷积计算模块、分块重组模块、数据后处理模块和特征图输出模块;所述控制模块接收到所述流程控制指令后,对所述流程控制指令进行解析,从而获得所述存储信息;所述控制模块将所述存储信息发送至所述数据读取模块;所述数据读取模块根据所述存储信息从所述ddr访问控制模块中将所述网络模型权重参数和输入特征图数据读入到fpga端的内部存储器中;所述数据预处理模块对所述内部存储器中的输入特征图数据进行稀疏编码和分组编码处理;所述卷积计算模块对预处理后的网络模型权重参数和输入特征图数据进行卷积计算;所述分块重组模块对所述卷积计算模块的计算结果数据进行重组;所述数据后处理模块对重组后的数据进行预分块,并对块内的数据做线性激活、池化操作、稀疏编码和像素激活值分组处理;所述特征图输出模块将所述数据后处理模块处理后的数据发送至所述特征图缓冲区。4.如权利要求3所述的一种面向fpga的稀疏卷积神经网络多级存储计算系统,其特征在于,所述控制模块包括层级指令解析单元、fpga状态监视单元、多模块控制单元、配置寄存器组和六个状态寄存器组;所述层级指令解析单元对所述arm端中流程控制模块发送过来的所述流程控制指令进行分析,从而获得所述存储信息;所述指令解析单元将所述存储信息存储在所述配置寄存器组中;所述fpga状态监视单元包括六个状态机,每个状态机均对应有一个状态寄存器组;所述fpga状态监视单元通过所述六个状态机同时分别对所述数据读取模块、数据预处理模块、卷积计算模块、分块重组模块、数据后处理模块和特征图输出模块的工作状态进行监

测,并将所述工作状态存入对应的状态寄存器组中;所述多模块控制单元根据所述工作状态生成控制指令,并将所述控制指令发送给对应的模块,以此来控制各个模块的初始化、启动、停止、复位和状态转换。5.如权利要求3所述的一种面向fpga的稀疏卷积神经网络多级存储计算系统,其特征在于,所述数据预处理模块中的分组编码处理具体包括:根据卷积核大小对所述网络模型权重参数和输入特征图数据进行分块,并在每个分块内根据像素激活值的块内位置对所述像素激活值进行编号,不同分块内相同编号的激活值视为一组;在读取激活值时,按照组的顺序进行读取数据。6.如权利要求3所述的一种面向fpga的稀疏卷积神经网络多级存储计算系统,其特征在于,所述卷积计算模块中的卷积计算,具体包括基于笛卡尔积的高速乘累加计算任务和针对存储访问冲突的低速累加计算任务。7.如权利要求3所述的一种面向fpga的稀疏卷积神经网络多级存储计算系统,其特征在于,所述fpga端还包括一个多级存储结构;所述多级存储结构根据所述内部存储器与所述卷积计算模块之间的距离,从远到近将所述内部存储器分为四个等级,生成四级存储结构;所述四级存储结构均采用乒乓轮转设计;其中每级均包括两个存储单元,所述两个存储单元轮转使用,其中未使用的存储单元提前读入下一次计算所需数据。

技术总结

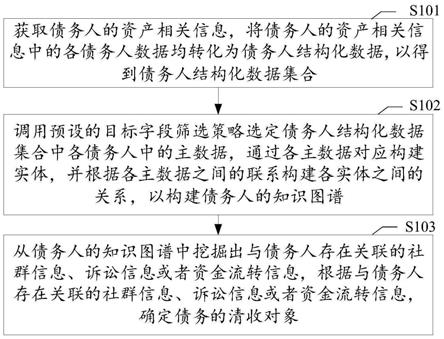

本发明公开了一种面向FPGA的稀疏卷积神经网络多级存储计算系统,其特征在于,包括ARM端和FPGA端;其中ARM端用于获取网络模型权重参数和输入特征图数据,根据网络模型权重参数和输入特征图数据的存储信息生成流程控制指令,并将该流程控制指令发送到FPGA端;FPGA端接收到所述流程控制指令后,从ARM端中读取网络模型权重参数和输入特征图数据,并进行计算,最后将计算结果反馈给所述ARM端;其中FPGA端的计算架构设计以并行计算阵列和多级存储结构为核心,发挥FPGA高并行度、高吞吐量和低功耗的硬件优势,充分利用稀疏卷积神经网络的稀疏特性,获得尽可能高的加速比,快速高效的实现卷积神经网络的前向推理过程。实现卷积神经网络的前向推理过程。实现卷积神经网络的前向推理过程。

技术研发人员:姜宏旭 胡宗琦 李波 张永华 田方正 张润华 谢传良

受保护的技术使用者:北京航空航天大学

技术研发日:2021.09.08

技术公布日:2021/12/11

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。