技术特征:

1.一种集成接收器电路,所述集成接收器电路包括:分数分频锁相环,所述分数分频锁相环提供时钟信号;相位插值器,所述相位插值器向所述时钟信号施加可控相移以提供采样信号;采样元件,所述采样元件通过根据所述采样信号对模拟接收信号进行采样来产生数字接收信号;定时误差估计器,所述定时误差估计器产生定时误差信号,所述定时误差信号指示所述采样信号相对于所述模拟接收信号的所估计的定时误差;第一反馈路径,所述第一反馈路径将所述定时误差信号耦合至所述相位插值器,以最小化所述所估计的定时误差的相位分量;第二反馈路径,所述第二反馈路径将所述定时误差信号耦合至所述相位插值器;以及第三反馈路径,所述第三反馈路径将所述定时误差信号耦合到所述分数分频锁相环,所述第二反馈路径和所述第三反馈路径最小化所述所估计的定时误差的频率偏移分量。2.如权利要求1所述的集成接收器电路,进一步包括解调器,所述解调器从所述数字接收信号中提取所传送的码元流。3.如权利要求1所述的集成接收器电路,其特征在于,所述第二反馈路径包括频率误差累加器并且所述第三反馈路径包括分频比误差累加器。4.如权利要求3所述的集成接收器电路,其特征在于,如在所述频率偏移分量的短期变化与长期变化之间进行比较,所述频率误差累加器优先对短期变化进行响应,并且所述分频比误差累加器优先对长期变化进行响应。5.如权利要求4所述的集成接收器电路,其特征在于,所述频率误差累加器包括泄漏的积分器,并且所述分频比累加器包括没有泄漏的积分器。6.根据权利要求5所述的集成接收器电路,其特征在于,所述第一反馈路径具有可编程相位误差比例系数k

p

,所述第二反馈路径具有可编程频率误差比例系数k

f

和可编程泄漏系数k

l

,并且所述第三反馈路径具有分频比误差比例系数k

d

。7.如权利要求1所述的集成接收器电路,进一步包括相位误差累加器,所述相位误差累加器由所述第一反馈路径和所述第二反馈路径共享。8.如权利要求1所述的集成接收器电路,其特征在于,所述第一反馈路径包括第一相位误差累加器,并且所述第二反馈路径包括频率误差累加器和第二相位误差累加器,所述第二相位累加器与所述第一相位误差累加器分离。9.如权利要求8所述的集成接收器电路,其特征在于,所述第二反馈路径以低于由所述第一反馈路径使用的时钟频率的时钟频率操作。10.一种时钟恢复方法,所述方法包括在集成接收器电路中:使用分数分频锁相环生成时钟信号;利用相位插值器对所述时钟信号的相位进行插值,以产生采样信号;根据所述采样信号对模拟接收信号进行采样,以获得数字接收信号;产生定时误差信号,所述定时误差信号指示所述采样信号相对于所述模拟接收信号的所估计的定时误差;经由第一反馈路径将所述定时误差信号耦合到所述相位插值器,以最小化所述所估计的定时误差的相位分量;

经由第二反馈路径将所述定时误差信号耦合到所述相位插值器,以最小化所述所估计的定时误差的短期频率偏移分量;以及经由第三反馈路径将所述定时误差信号耦合到所述分数分频锁相环,以最小化所述所估计的定时误差的长期频率偏移分量。11.如权利要求10所述的时钟恢复方法,进一步包括对所述数字接收信号进行解调以提取所传送的码元流。12.如权利要求10所述的时钟恢复方法,其特征在于,所述第二反馈路径包括频率误差累加器并且所述第三反馈路径包括分频比误差累加器。13.如权利要求12所述的时钟恢复方法,其特征在于,所述频率误差累加器包括泄漏的积分器,并且所述分频比累加器包括没有泄漏的积分器。14.根据权利要求13所述的时钟恢复方法,其特征在于,所述第一反馈路径具有可编程相位误差比例系数k

p

,所述第二反馈路径具有可编程频率误差比例系数k

f

和可编程泄漏系数k

l

,并且所述第三反馈路径具有分频比误差比例系数k

d

。15.一种包括用于制造集成接收器电路的半导体制造工艺掩模图案的非暂态信息存储介质,包括:分数分频锁相环,所述分数分频锁相环提供时钟信号;相位插值器,所述相位插值器对所述时钟信号施加可控相移,以提供采样信号;采样元件,所述采样元件通过根据所述采样信号对模拟接收信号进行采样来产生数字接收信号;定时误差估计器,所述定时误差估计器产生定时误差信号,所述定时误差信号指示所述采样信号相对于所述模拟接收信号的所估计的定时误差;第一反馈路径,所述第一反馈路径将所述定时误差信号耦合到所述相位插值器,以最小化所述所估计的定时误差的相位分量;第二反馈路径,所述第二反馈路径将所述定时误差信号耦合至所述相位插值器;以及第三反馈路径,所述第三反馈路径将所述定时误差信号耦合到所述分数分频锁相环,所述第二反馈路径和所述第三反馈路径最小化所述所估计的定时误差的频率偏移分量。16.如权利要求15所述的存储介质,其特征在于,所述第二反馈路径包括频率误差累加器并且所述第三反馈路径包括分频比误差累加器。17.如权利要求16所述的存储介质,其特征在于,如在所述频率偏移分量的短期变化与长期变化之间进行比较,所述频率误差累加器优先对短期变化进行响应,并且所述分频比误差累加器优先对长期变化进行响应。18.如权利要求17所述的存储介质,其特征在于,所述频率误差累加器包括泄漏的积分器,并且所述分频比累加器包括没有泄漏的积分器。19.根据权利要求18所述的存储介质,其特征在于,所述第一反馈路径具有可编程相位误差比例系数k

p

,所述第二反馈路径具有可编程频率误差比例系数k

f

和可编程泄漏系数k

l

,并且所述第三反馈路径具有分频比误差比例系数k

d

。

技术总结

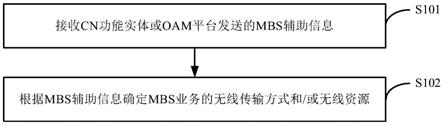

本发明涉及使用三个反馈路径的二阶时钟恢复。说明性的数字通信接收器和基于分数分频锁相环的时钟恢复方法提供对任何所包括的相位插值器中的非线性显著降低的敏感度。一个接收器实施例包括:分数分频锁相环,提供时钟信号;相位插值器,对时钟信号施加可控相移以提供采样信号;采样元件,通过对模拟接收信号进行采样产生数字接收信号;定时误差估计器,产生定时误差信号;第一反馈路径,将定时误差信号耦合至相位插值器以最小化所估计的定时误差的相位分量;第二反馈路径,将定时误差信号耦合至相位插值器;以及第三反馈路径,将定时误差信号耦合至分数分频锁相环,第二反馈路径和第三反馈路径最小化所估计的定时误差的频率偏移分量。率偏移分量。率偏移分量。

技术研发人员:Y

受保护的技术使用者:默升科技集团有限公司

技术研发日:2021.05.14

技术公布日:2021/11/19

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。