1.本实用新型涉及电子通信设备领域,具体涉及一种万兆双光口网卡。

背景技术:

2.网卡(也被称为网络适配器)是一块被设计用来允许计算机在计算机网络上进行通讯的计算机硬件。由于其拥有mac地址,因此属于osi模型的第2层。它使得用户可以通过电缆或无线相互连接。每一个网卡都有一个被称为mac地址的独一无二的48位串行号,它被写在卡上的一块rom中。但是传统的网络适配器,功能性和兼容性已经不能很好地满足不同cpu平台及系统的适配与应用。

技术实现要素:

3.为了解决上述问题,本实用新型提供了一种万兆双光口网卡,具体方案如下:

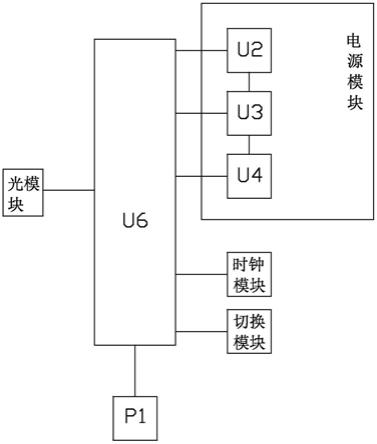

4.一种万兆双光口网卡,包括基础板,所述基础板上板载有主芯片u6,所述主芯片u6通过插槽p1与主板连接,所述基础板上还板载有与所述主芯片u6连接的电源模块、时钟模块、切换模块和光模块;

5.所述电源模块包括与所述主芯片u6连接的电源管理芯片u3、电平转换芯片u1和降压调节芯片u2和同步升压芯片u4。

6.进一步地,所述电源管理芯片u3的第一引脚串联第一电阻r1与主工作电路连接,所述电源管理芯片u3的第八引脚通过所述插槽p1与主板电源连接作为电输入端,所述电源管理芯片u3的第三引脚、第四引脚和第八引脚之间设有滤波电路;所述电源管理芯片u3的第五引脚和第九引脚接地;所述电源管理芯片u3的第六引脚串联第一电感l1作为电输出端,所述电源管理芯片u3的第六引脚也连接有滤波电路;所述电源管理芯片u3的第七引脚串联第一电容c1后与第六引脚连接;所述电源管理芯片u3的第二引脚串联第二电阻r2后接地,所述电源管理芯片u3的第六引脚与所述第二引脚之间并联有第三电阻r3;

7.所述电平转换芯片u1的第六引脚和第七引脚接电,所述电平转换芯片u1的第二引脚接地;电平转换芯片u1的第六引脚串联有第四电阻r4;所述电平转换芯片u1的第三引脚与第六引脚连接;所述电平转换芯片u1的第四引脚和第五引脚与所述主芯片u6连接;所述电平转换芯片u1的第一引脚和第八引脚与所述插槽p1连接;

8.所述降压调节芯片u2的第六引脚和第四引脚接电,所述降压调节芯片u2的第二引脚和第五引脚并联后接地;所述降压调节芯片u2的第一引脚串联第五电阻r5后与第六引脚连接,所述降压调节芯片u2的第六引脚还通过第二电容c2接地;所述降压调节芯片u2的第四引脚还连接第二电感l2和第三电容c3后接地;所述降压调节芯片u2的第三引脚连接有并联的第四电容c4和第六电阻r6,所述第四电容c4与所述压调节芯片u2的第四引脚连接,所述第六电阻r6接地;所述降压调节芯片u2的第三引脚和第四引脚之间并联有第七电阻r7;

9.所述同步升压芯片u4的第二引脚与主工作电路连接,所述同步升压芯片u4的第三引脚、第四引脚、第五引脚和第六引脚与第二引脚并联,所述同步升压芯片u4的第十四引脚

通过第九电阻r9与第二引脚并联;所述同步升压芯片u4的第十一引脚接地,所述同步升压芯片u4的第十二引脚与第十一引脚接地,所述同步升压芯片u4的第十五引脚分别通过第十七电阻r17和十八电阻r18与第二引脚和第十一引脚并联;所述同步升压芯片u4的第二十二引脚接电,所述同步升压芯片u4的第七引脚、第二十三引脚和第二十四引脚与第二十二引脚并联,所述同步升压芯片u4的第一引脚通过第十电容c10与第二十二引脚并联;所述同步升压芯片u4的第八引脚接地,所述同步升压芯片u4的第九引脚、第十引脚、第二十一引脚和第二十五引脚与第八引脚并联;所述同步升压芯片u4的第二十引脚和第二十一引脚通过第十一电容c11串联;所述同步升压芯片u4的第十三引脚分别通过第十九电阻r19和二十电阻r20与第二十引脚和第二十一引脚并联;

10.所述同步升压芯片u4的第二引脚设有滤波电路,所述同步升压芯片u4的第十七引脚和第十六引脚之间设有滤波电路,所述同步升压芯片u4的第二十二引脚设有滤波电路,所述同步升压芯片u4的第二十二引脚和第十八引脚之间设有滤波电路。

11.进一步地,所述时钟模块包括时钟驱动芯片u5,所述时钟驱动芯片u5的第一引脚和第十七引脚并联后接地,所述时钟驱动芯片u5的第二引脚和第五引脚接电;所述时钟驱动芯片u5的第二引脚串联有第八电阻r8,所述时钟驱动芯片u5的第五引脚并联第五电容c5后接地;所述时钟驱动芯片u5的第六引脚和第七引脚连接有振荡电路,所述时钟驱动芯片u5的第九引脚、第十引脚、第十一引脚和第十二引脚与所述主芯片u6连接。

12.进一步地,所述振荡电路包括振荡芯片y,所述振荡芯片y的第四引脚串联第三电感l3后接电,所述振荡芯片y的第三引脚与所述时钟驱动芯片u5连接,所述振荡芯片y的第二引脚接地;所述振荡芯片y的第四引脚还并联第六电容c6后接地,所述振荡芯片y的第三引脚串联有第十电阻r10。

13.进一步地,所述切换模块包括与所述主芯片u6连接的缓存芯片u8、跳线jmp以及排针接口j1,所述跳线jmp连接有电流监控芯片u7;

14.所述电流监控芯片u7的第一引脚、第三引脚、第五引脚和第六引脚接电,所述电流监控芯片u7的第二引脚和第五引脚接地,所述电流监控芯片u7的第四引脚串联第七电容c7后与第二引脚连接;所述电流监控芯片u7的第一引脚还串联有第十一电阻r11,所述电流监控芯片u7的第三引脚还串联有第十二电阻r12,所述电流监控芯片u7的第五引脚还串联有第十三电阻r13,所述电流监控芯片u7的第六引脚并联第八电容c8后接地;所述电流监控芯片u7的第五引脚还连接有滤波电路;

15.所述缓存芯片u8的第一引脚、第二引脚、第五引脚和第六引脚与所述主芯片u6连接,所述缓存芯片u8的第四引脚接地;所述缓存芯片u8的第八引脚接电,所述缓存芯片u8的第八引脚还通过第九电容c9与第四引脚并联;所述缓存芯片u8的第三引脚和第七引脚分别串联第十四电阻r14和第十五电阻r15后与第八引脚并联;

16.所述跳线jmp的第一引脚、第二引脚、第三引脚、第五引脚和第六引脚与所述主芯片u6连接,所述跳线jmp的第四引脚接地,所述跳线jmp的第七引脚与所述电流监控芯片u7连接,所述跳线jmp的第九引脚接电;所述跳线jmp的第九引脚还并联有第三电感l3;

17.所述排针接口j1的第一引脚和第二引脚与所述主芯片u6连接,所述排针接口j1的第三引脚接地。

18.进一步地,所述光模块包括光接口j2和j3,所述光接口j2和j3各自通过一个电压

转换芯片u9与所述主芯片u6连接,所述电压转换芯片u9的第二引脚和第十九引脚接电,所述电压转换芯片u9的第十一引脚接地;所述电压转换芯片u9的第十引脚串联第十六电阻r16后与第二引脚并联;所述电压转换芯片u9的第一引脚、第三引脚、第四引脚、第五引脚、第六引脚、第七引脚、第八引脚、第九引脚与所述主芯片u6连接,所述电压转换芯片u9的第十二引脚、第十三引脚、第十四引脚、第十五引脚、第十六引脚、第十七引脚、第十八引脚、第二十引脚与所述光接口j2或光接口j3连接

19.本实用新型的有益效果在于,本实用新型提供的网卡,相较于传统网卡,极大地提高了各方面性能,能满足不同cpu平台及系统的适配与应用:

20.1、提供四端口rj45接口连接;

21.2、创新的电源管理功能和节能以太网(eee),集成的直接存储器提高效率并降低功耗;

22.3、灵活的i/o虚拟化技术为端口区分和服务质量(qos)提供了多达32条虚拟通道;

23.4、可拓展的iscsi提供具有成本效益的san连接性能;

24.5、高性能主机接口设计pci express 2.1。

附图说明

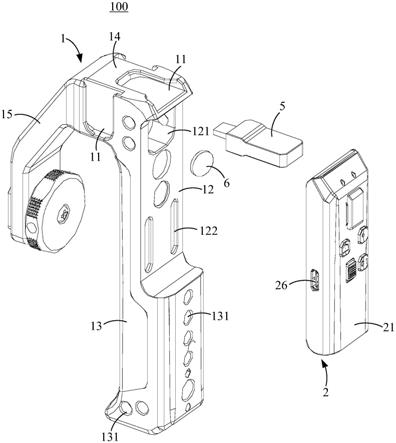

25.图1.本实用新型的连接示意图,

26.图2.本实用新型电源管理芯片的电路图,

27.图3.本实用新型电平转换芯片的电路图,

28.图4.本实用新型降压调节芯片的电路图,

29.图5.本实用新型同步升压芯片的电路图,

30.图6.本实用新型时钟驱动芯片的电路图,

31.图7.本实用新型振荡电路的电路图,

32.图8.本实用新型另一些实施例的连接示意图,

33.图9.本实用新型电流监控芯片的电路图,

34.图10.本实用新型缓存芯片的电路图,

35.图11.本实用新型跳线的电路图,

36.图12.本实用新型排针接口的电路图,

37.图13.本实用新型再一些实施例的连接示意图,

38.图14.本实用新型电压转换芯片的电路图。

具体实施方式

39.下面结合附图和实施例对本实用新型作进一步的描述,下列实施例仅用于解释本实用新型的实用新型内容,不用于限定本实用新型的保护范围。

40.一种万兆双光口网卡,包括基础板,基础板上板载有主芯片u6(sapphire),如图1所示,主芯片u6通过插槽p1(pcie

‑

x8)与主板连接,基础板上还板载有与主芯片u6连接的电源模块、时钟模块、切换模块和光模块;

41.电源模块包括与主芯片u6连接的电源管理芯片u3(tps54627dda)、电平转换芯片u1(txs0102dctr)和降压调节芯片u2(sy8011bdqc)和同步升压芯片u4(sy8182qcc)。

42.如图2,电源管理芯片u3的第一引脚串联第一电阻r1与主工作电路连接,电源管理芯片u3的第八引脚通过插槽p1与主板电源连接作为电输入端,电源管理芯片u3的第三引脚、第四引脚和第八引脚之间设有滤波电路;电源管理芯片u3的第五引脚和第九引脚接地;电源管理芯片u3的第六引脚串联第一电感l1作为电输出端,电源管理芯片u3的第六引脚也连接有滤波电路;电源管理芯片u3的第七引脚串联第一电容c1后与第六引脚连接;电源管理芯片u3的第二引脚串联第二电阻r2后接地,电源管理芯片u3的第六引脚与第二引脚之间并联有第三电阻r3。

43.如图3,电平转换芯片u1的第六引脚和第七引脚接电,电平转换芯片u1的第二引脚接地;电平转换芯片u1的第六引脚串联有第四电阻r4;电平转换芯片u1的第三引脚与第六引脚连接;电平转换芯片u1的第四引脚和第五引脚与主芯片u6连接;电平转换芯片u1的第一引脚和第八引脚与插槽p1连接。

44.如图4,降压调节芯片u2的第六引脚和第四引脚接电,降压调节芯片u2的第二引脚和第五引脚并联后接地;降压调节芯片u2的第一引脚串联第五电阻r5后与第六引脚连接,降压调节芯片u2的第六引脚还通过第二电容c2接地;降压调节芯片u2的第四引脚还连接第二电感l2和第三电容c3后接地;降压调节芯片u2的第三引脚连接有并联的第四电容c4和第六电阻r6,第四电容c4与压调节芯片u2的第四引脚连接,第六电阻r6接地;降压调节芯片u2的第三引脚和第四引脚之间并联有第七电阻r7。

45.如图5,同步升压芯片u4的第二引脚与主工作电路连接,同步升压芯片u4的第三引脚、第四引脚、第五引脚和第六引脚与第二引脚并联,同步升压芯片u4的第十四引脚通过第九电阻r9与第二引脚并联;同步升压芯片u4的第十一引脚接地,同步升压芯片u4的第十二引脚与第十一引脚接地,同步升压芯片u4的第十五引脚分别通过第十七电阻r17和十八电阻r18与第二引脚和第十一引脚并联;同步升压芯片u4的第二十二引脚接电,同步升压芯片u4的第七引脚、第二十三引脚和第二十四引脚与第二十二引脚并联,同步升压芯片u4的第一引脚通过第十电容c10与第二十二引脚并联;同步升压芯片u4的第八引脚接地,同步升压芯片u4的第九引脚、第十引脚、第二十一引脚和第二十五引脚与第八引脚并联;同步升压芯片u4的第二十引脚和第二十一引脚通过第十一电容c11串联;同步升压芯片u4的第十三引脚分别通过第十九电阻r19和二十电阻r20与第二十引脚和第二十一引脚并联;

46.同步升压芯片u4的第二引脚设有滤波电路,同步升压芯片u4的第十七引脚和第十六引脚之间设有滤波电路,同步升压芯片u4的第二十二引脚设有滤波电路,同步升压芯片u4的第二十二引脚和第十八引脚之间设有滤波电路。

47.如图6,时钟模块包括时钟驱动芯片u5(si53340

‑

b

‑

gm),时钟驱动芯片u5的第一引脚和第十七引脚并联后接地,时钟驱动芯片u5的第二引脚和第五引脚接电;时钟驱动芯片u5的第二引脚串联有第八电阻r8,时钟驱动芯片u5的第五引脚并联第五电容c5后接地;时钟驱动芯片u5的第六引脚和第七引脚连接有振荡电路,时钟驱动芯片u5的第九引脚、第十引脚、第十一引脚和第十二引脚与主芯片u6连接。

48.参照图7,振荡电路包括振荡芯片y(sit8209ac

‑

33

‑

33e

‑

156.25),振荡芯片y的第四引脚串联第三电感l3后接电,振荡芯片y的第三引脚与时钟驱动芯片u5连接,振荡芯片y的第二引脚接地;振荡芯片y的第四引脚还并联第六电容c6后接地,振荡芯片y的第三引脚串联有第十电阻r10。

49.如图8,所述切换模块包括与所述主芯片u6连接的缓存芯片u8(w25q16fwsnig)、跳线jmp(jmp5*2)以及排针接口j1(3px2.54mm),所述跳线jmp连接有电流监控芯片u7(tps3808g01dbvt);

50.如图9,电流监控芯片u7的第一引脚、第三引脚、第五引脚和第六引脚接电,电流监控芯片u7的第二引脚和第五引脚接地,电流监控芯片u7的第四引脚串联第七电容c7后与第二引脚连接;电流监控芯片u7的第一引脚还串联有第十一电阻r11,电流监控芯片u7的第三引脚还串联有第十二电阻r12,电流监控芯片u7的第五引脚还串联有第十三电阻r13,电流监控芯片u7的第六引脚并联第八电容c8后接地;电流监控芯片u7的第五引脚还连接有滤波电路;

51.如图10,缓存芯片u8的第一引脚、第二引脚、第五引脚和第六引脚与主芯片u6连接,缓存芯片u8的第四引脚接地;缓存芯片u8的第八引脚接电,缓存芯片u8的第八引脚还通过第九电容c9与第四引脚并联;缓存芯片u8的第三引脚和第七引脚分别串联第十四电阻r14和第十五电阻r15后与第八引脚并联;

52.如图11,跳线jmp的第一引脚、第二引脚、第三引脚、第五引脚和第六引脚与主芯片u6连接,跳线jmp的第四引脚接地,跳线jmp的第七引脚与电流监控芯片u7连接,跳线jmp的第九引脚接电;跳线jmp的第九引脚还并联有第四电感l4;

53.如图12,排针接口j1的第一引脚和第二引脚与主芯片u6连接,排针接口j1的第三引脚接地。

54.结合图13和图14,光模块包括光接口j2(sfp

‑

1)和j3(sfp

‑

1),光接口j2和j3各自通过一个电压转换芯片u9(txs0108epwr)与主芯片u6连接,电压转换芯片u9的第二引脚和第十九引脚接电,电压转换芯片u9的第十一引脚接地;电压转换芯片u9的第十引脚串联第十六电阻r16后与第二引脚并联;电压转换芯片u9的第一引脚、第三引脚、第四引脚、第五引脚、第六引脚、第七引脚、第八引脚、第九引脚与主芯片u6连接,电压转换芯片u9的第十二引脚、第十三引脚、第十四引脚、第十五引脚、第十六引脚、第十七引脚、第十八引脚、第二十引脚与光接口j2或光接口j3连接。

55.本技术记载的网卡,对性能进行了优化,使系统i/o不再是高端网络应用的瓶颈;本技术能够通过捆绑组实现容错,来自故障端口的通信将被路由至同组中其他成员;本技术具有集成的硬件加速功能,能够执行tcp/udp/ip校验和分载及tcp分段任务;主机处理技术可分载加速器,释放cpu资源,以处理其他应用程序。

56.综上,仅为本实用新型之较佳实施例,不以此限定本实用新型的保护范围,凡依本实用新型专利范围及说明书内容所作的等效变化与修饰,皆为本实用新型专利涵盖的范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。