用于显示端口隧穿的带宽管理分配

1.相关申请的交叉引用

2.根据美国专利法第119条e款,本技术要求享有于2020年4月27日提交的标题为“bandwidth management allocation for displayport tunneling”的序号为63/016,121的美国临时专利申请的权益,其全部内容通过引用并入本文。

背景技术:

3.显示端口(dp)是一种数字显示接口,其用于将图像、视频和/或另一多媒体资源连接到显示设备(例如,计算机监视器)。通用串行总线(usb)是一种通信和互连协议。usb协议与电缆和连接器以及用于计算机、外围设备和其他组件之间的通信和功率递送的协议密切相关。

附图说明

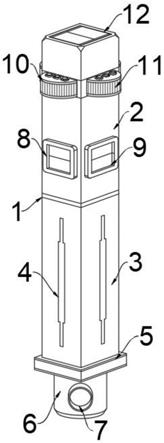

4.图1是根据本公开的实施例的示例通用串行总线系统的示意图。

5.图2a是根据本公开的实施例的示例通用串行总线协议栈的示意图。

6.图2b是示出根据本公开的实施例的示例通用串行总线功能层通信通路的示意图。

7.图3是根据本公开的实施例的示例通用串行总线分组的示意图。

8.图4是根据本公开的实施例的示例显示端口信号的示意图。

9.图5是根据本公开的实施例的示例系统500的示意图,该示例系统500使用显示端口隧穿通过通用串行总线(usb)集线器来将显示端口源耦合到显示端口汇聚结点(display port sink)。

10.图6是根据本公开的实施例的用于将显示端口信号映射到通用串行总线分组上的过程流程图。

11.图7示出了包括互连架构的计算系统的实施例。

12.图8示出了包括分层栈的互连架构的实施例。

13.图9示出了要在互连架构内生成或接收的请求或分组的实施例。

14.图10示出了用于互连架构的发射器和接收器对的实施例。

15.图11示出了用于包括处理器的计算系统的框图的另一个实施例。

16.图12示出了用于包括多个处理器插口(socket)的计算系统的块的实施例。

17.附图未按比例绘制。贯穿各个附图,类似的附图标记指代类似的部分。

具体实施方式

18.图1是根据本公开的实施例的示例通用串行总线(usb)系统100的示意图。图1示出了示例usb系统100的双总线架构(例如,通过usb4或更高的协议实现的那些)。按照架构,向后兼容性利用最低的互操作性得到支持,该互操作性从usb 2.0开始,逐步发展到usb 3.2,并且最后达到基于跨互连组件支持的最高公共总线级别的usb4。

19.usb系统100可以包括通过usb链路连接到usb4集线器104的usb4主机102。usb4集

线器104可以通过usb链路连接到usb4设备106。usb4集线器104还可以连接到其他类型的设备(例如,显示器或外围设备或其他类型的设备)。usb4主机102可以是(或者可以耦合到)主机设备(例如,主机设备、计算机、服务器、母板、处理器或处理器组或其他类型的主机设备)。usb4集线器104可以是(或者可以包括)加密狗(dongle)、对接站或其他中间设备。usb4设备106可以是端点设备、外围设备、存储器或连接到usb4主机102和/或usb4集线器104的其他类型的设备。

20.系统100可以包括usb4主机102。usb4主机可以包括主机路由器110、内部主机控制器和显示端口源112(例如,displayport2.0源)。displayport2.0(或dp2.0)源可以是图形处理器,并且可以包括支持dp2.0和更高版本的displayport发送器(dptx)。dptx可以符合视频电子标准协会(vesa)displayport2.0协议标准或将来的displayport协议标准版本。

21.usb4主机支持20g usb4操作(gen2x2)和可选地40g usb4操作(gen3x2)。usb4主机还可以支持在其所有dfp上的displayportalt模式。参见关于dfp上的displayportalt模式支持的要求和细节的完整定义的usb type

‑

c规范。

22.usb4主机也可以可选地包含pcie控制器114。pcie控制器114可以包括(或连接到)pcie根复合体或pcie交换机复合体,以用于控制到一个或多个外围设备的基于pcie的路由。pcie控制器114可以通过一个或多个pcie适配器(例如,pcie面向下游的适配器128、130)连接到usb4主机路由器110。usb4集线器104可以经由pcie面向上游的适配器154和pcie面向下游的适配器156和158包括(或连接到)pcie交换机144。usb4设备106可以包括pcie功能180,其是跨usb4结构100与pcie控制器114通信的pcie下游连接的组件或端点设备。usb4设备路由器178可以包括pcie面向上游的适配器190,以将pcie功能180与上游连接的组件(例如,usb4集线器104、pcie交换机144和pcie控制器114)耦合。

23.usb4主机104可以包括usb主机路由器110。usb4集线器106可以包括usb集线器路由器142。usb4设备106可以包括usb设备路由器178。路由器是usb4架构的基本构建块。路由器将隧穿协议(tunneled protocol)流量映射到usb4分组,并通过usb4结构100来路由分组。路由器还经由其时间管理单元(tmu)(例如,tmu 140、170和196)贯穿usb4结构来分发和同步时间。路由器由位于usb4主机内的连接管理器(例如,主机接口适配器)124发现并配置。路由器包括在适配器之间创建内部路径所必需的平面点对点、可配置的交换机。usb4主机102、usb4集线器104或usb4设备106的每个实例内通常存在一个路由器。存在两种类型的路由器:主机路由器和设备路由器。

24.usb4主机或usb4外围设备可以可选地支持与thunderbolt 3(tbt3)产品的互操作性。需要usb4集线器以支持与其所有dfp上的thunderbolt 3产品的互操作性。除了其所有dfp之外,还需要基于usb4的对接(dock)来支持与其ufp上的thunderbolt 3产品的互操作性。

25.当与tbt3产品互操作时,thunderbolt alt模式被建立在产品之间的链路上。usb type

‑

c规范描述了usb4产品如何进行协商并进入thunderbolt alt模式。

26.usb4主机102可以包括(或者可以连接到)显示端口(dp)源112(例如,图形处理单元(gpu)或图形、视频、图像的其他源等)。usb4主机路由器110可以包括dp_in适配器126,该dp_in适配器126可以促进到dp源112的接口。在实施例中,dp源可以是usb4外围设备,或者可以经由基于displayport的互连(例如,经由displayport2.0协议互连)连接到usb4主机

路由器110。

27.usb4集线器104可以包括用于将dp信令输出到诸如显示器或监视器之类的dp汇聚结点的dp_out适配器152。usb4集线器104还可以经由usb4隧道将dp信令发送到usb4设备106。usb4设备106可以包括用于将dp信号输出到dp汇聚结点182的dp_out适配器192,dp汇聚结点182可以是显示器或监视器。

28.内部的增强型超高速主机116显露了一个或多个下游usb3端口,这些端口可以连接到usb端点或下游usb3协议适配器。内部的增强型超高速集线器接口的上游端口与上游usb3协议适配器接合,该上游usb3协议适配器将分组转发到usb4集线器的面向上游的端口。

29.每个路由器包含高达64个适配器。适配器提供路由器和外部实体之间的接口。存在三种类型的适配器:协议适配器、通道适配器和控制适配器。协议适配器用于在被支持的本机协议和usb4隧道之间进行转换。存在四种类型的协议适配器:usb3适配器136、138、164、166、168和194;displayport(dp)适配器126、152和182;pcie适配器128、130、154、156、158和190;以及主机接口适配器124。

30.路由器可以支持内部的控制适配器,该内部的控制适配器仅用于发送和接收往返传输层的控制分组。与非控制适配器不同,控制适配器不直接地连接到链路,并且因此不具有与之相关联的物理层。

31.usb4端口是提供usb4功能接口的实体,该usb4功能接口驻留在usb4链路的每一端上。它由usb4数据总线的发送和接收通道以及双线式边带(two

‑

wire sideband)(sb)信道(sbtx/sbrx)组成。usb4端口作为单通道链路或双通道链路操作。当作为单通道链路操作时,usb4端口的通道1被禁用。当作为双通道链路操作时,通道0和1在逻辑上绑定在一起以提供单个数据信道。示例usb4端口被示出为元素132、134、160、162和188。usb4端口可以容纳usb type

‑

c连接器或thunderbolt(例如,tbt3)类型连接器等。

32.usb4结构的主要通信信道在将两个usb4端口互连的usb4链路上。usb4链路传输路由器之间的隧穿协议流量和总线管理流量二者的分组。usb4端口的边带信道用于初始化和管理usb4端口之间的usb4链路。针对启用usb4的usb type

‑

c端口,完整的接口包括usb4端口、usb 2.0数据总线、和usb type

‑

c配置信道(cc)以及电源/接地(vbus、vconn和gnd)。

33.在高级别处,usb4集线器104在功能上类似于usb 3.2集线器——它由一个面向上游的端口和一个或多个面向下游的端口组成。usb4集线器104在功能上作为树状结构操作,以用于使得一个或多个面向下游的端口能够由一个面向上游的端口来服务,通常出于端口扩展的目的。

34.除了特定于usb4的集线器功能之外,还支持usb 3.2和usb 2.0集线器功能,使得usb4集线器的面向下游的端口可以支持与usb 3.2和usb 2.0设备的向后兼容性。可以经由连接到usb 2.0集线器146的usb 2.0主机118和usb 2.0功能184提供usb 2.0功能性。

35.usb4集线器包含设备路由器、增强型超高速usb集线器、pcie交换机和usb 2.0集线器。usb4集线器支持20g usb4操作(gen2x2)和40g usb4操作(gen3x2)。需要usb4集线器以支持在其所有dfp上的displayport alt模式。参见关于dfp上的displayport alt模式支持的要求和细节的全部定义的usb type

‑

c规范。

36.usb4主机102、集线器104和设备106可以包括一个或多个usb type

‑

c连接器端口

120、122、172、174、176和198。usb type

‑

c连接器端口可以接收usb type

‑

c连接器,以用于连接的usb兼容组件以及用于在组件之间传送信息和功率。

37.图2a是根据本公开的实施例的示例usb协议栈200的示意图。usb4协议栈200可以包括电气层202和逻辑层204。电气层202和逻辑层204可以被认为是物理层206的子块。电气层202定义了usb4链路的电气信令特性,包括加扰、编码、抖动和电压。逻辑层206建立了两个路由器之间的usb4链路,并且提供了在它们之间发送和接收字节流的服务。逻辑层204驻留在电气层202之上并且在传输层208的下方。逻辑层204将往返传输层208的流量视为字节流。

38.由逻辑层204提供的服务为:具有链路伙伴的usb4链路的建立和维护;经由不同的速度和宽度的性能可扩展性;错误检测和恢复机制;利用不同的介质(例如,无源电缆、有源电缆和重定时器)的操作;针对诸如时钟补偿、数据加扰、前向纠错码和电源管理之类的机制的支持。

39.usb4链路由配套的边带信道协助和管理,该边带信道配置usb4链路的参数,与重定时器(如果存在)交互并且执行usb4链路txffe握手,确保usb4链路收发器和重定时器的正确的掉电/唤醒序列。

40.传输层208通过总线转发隧穿分组并控制分组。传输层208定义分组格式、路由、服务质量(qos)支持、流控制和时间同步。传输层208是执行协议复用的地方。

41.配置层204执行路由器配置任务并处理传入控制分组。配置层204针对域内的控制分组提供寻址方案,处理控制分组,并且为控制分组提供可靠的传输机制。控制分组向连接管理器提供对路由器的配置空间的访问。

42.协议适配器层204执行隧穿协议流量和usb4传输层分组之间的映射。协议适配器层204由它发送和接收的隧穿协议流量的类型定义。

43.usb4主机支持usb3隧穿、displayport隧穿和主机到主机隧穿。usb4主机也可以可选地支持pcie隧穿。usb4集线器支持usb3隧穿、displayport隧穿、pcie隧穿和主机到主机隧穿。存在usb4集线器支持displayport隧穿的多种方式。例如,usb4集线器充当用于displayport隧穿的“直通(pass through)”(即,usb4集线器直接在其两个usb4端口之间路由隧穿流量)。usb4集线器包含接收来自usb4端口的隧穿displayport流量并将其发送到displayport汇聚结点的dp out适配器。

44.图2b是示出根据本公开的实施例的示例通用串行总线功能层通信路径的示意图220。该通信构造可以包括传送分组和有序集合的usb4链路222。

45.控制分组226由连接管理器224用于配置和管理跨总线的路由器。控制分组226还由路由器用于与连接管理器224通信。基于标识生成树(spanning tree)中的路由器的位置的路由字符串来在总线上路由控制分组226。当控制分组226源自连接管理器224时,路由字符串标识该分组所针对的路由器。当控制分组226源自路由器时,路由器字符串标识发送分组的路由器。非目标路由器中的控制适配器将分组转发到usb4端口。目标路由器的控制适配器消费控制分组226。

46.在隧穿分组230中通过usb4结构对协议流量228进行封装和隧穿。隧穿分组230沿着一个或多个路径横穿usb4结构。

47.链路管理分组232被限制到单个usb4链路222。链路管理分组232源自链路的一端

处的路由器的传输层208,并且终止于链路的另一端处的路由器的传输层。定义了以下链路管理分组:时间同步分组——用于同步总线上的路由器的时钟;流控制分组——用于防止缓冲器溢出;空闲分组——确保当没有其他传输层分组正在被发送时,稳定的字节流被馈送到逻辑层。

48.逻辑层204将有序集合234用于诸如符号同步、链路训练和通道之间的延迟校正(de

‑

skew)之类的任务。有序集合238是66位符号(以gen 2速度)或132位符号(以gen 3速度)。

49.边带信道240处理以下事件:通道初始化;usb4端口上的连接或断开连接;通道禁用或启用;以及进入或退出睡眠状态。

50.当退出电源管理链路状态时,低频周期性信令(lfps)236用于两个链路伙伴之间的带内通信。

51.传输层分组是来自协议适配器层的隧穿分组、来自配置层的控制分组或是在传输层内生成的(即,在传输层内生成的链路管理分组)。

52.隧穿分组由源适配器的协议适配器层生成,并且被移交给传输层。隧穿分组应当具有针对表1中的传输层分组定义的报头。源适配器的协议适配器层应当将大于256字节的协议流量分段成多个隧穿分组。来自隧穿分组的协议流量的重组应当由目的地适配器的协议适配器层执行。

53.传输层分组的大小始终是4字节的倍数。源适配器的协议适配器层应当向隧穿分组的有效载荷添加0到3个字节之间的填充,以确保隧穿分组的大小是4字节的倍数。目标适配器的协议适配器层应当移除任何填充字节。

54.填充字节的内容是特定于实施方式的,并且不能被假设为具有任何特定值。然而,推荐使用零字节填充。

55.图3是根据本公开的实施例的示例usb分组的示意图。在usb4中,每个分组大小可以包括256个字节(包括报头)。存在两种类型的报头:传输层报头格式,其包括协议定义的字段(pdf)和长度——包含有效载荷大小(以字节为单位,不包括填充大小)。报头的第二种类型是每一特定pdf格式定义的传输单元报头。示例分组300被示出包括传输层报头302以及若干个传输单元报头304、308、310和312。

56.表1示出了示例传输层分组报头格式。

57.表1.传输层报头格式。

[0058][0059]

分组300还可以包括数据字段306和314。数据字段的长度可以由传输层报头302定义。

[0060]

通过displayport sst主链路携带的视频和音频数据被组织成帧。每个帧包含若干条有效扫描线,后跟垂直消除时段(blanking period)。每条扫描线包含有效像素数据,后跟水平消除时段。有效像素数据被组织成固定大小的块(其被称为传输单元)。每个传输单元(tu)包含有效像素数据,后跟填充符号。在水平和垂直消除时段期间也会发送填充符号。

[0061]

当displayport sst主链路被映射到usb4上时,连续的主链路数据流被封装到隧穿分组中。在封装之前,所有的填充符号(在tu内以及在消除时段期间)由dp_in适配器丢弃。当主链路数据流从隧穿分组中提取时,填充符号会由dp out适配器重新创建。为了实现在dp out适配器处的填充符号的准确的重建,dp_in适配器在每个隧穿分组中都包括填充计数字段。填充计数字段指定紧接在分组之前丢弃的填充符号的数量。

[0062]

图4是根据本公开的实施例的示例显示端口信号400的示意图。显示端口链路层作为四个主链路通道进行操作,每个通道符号数据大小为32位,并且每个有效的链路层时钟总共携带128位。displayport2.0链路层帧可以包含1024个多流传输分组(mtp)。图4示出了示例dp2.0链路层mtp和链路层帧。

[0063]

示例链路层帧n 402可以包括1024个mtp(例如,mtp2 406)。基于displayport规范,每个流包括有用的数据、控制信息和填充符号。每64个链路符号(或有效的时钟周期)被称为时隙:每个多流传输分组(mtp)包括64个时隙。displayport规范允许通过链路传送高达64个独立的流,每个时隙一个流,或者将多个时隙组合用于单个流。图4示出了三个流的示例,其中,每个流使用不同数量的时隙:(有效载荷1 408使用时隙0

‑

29,有效载荷2 410使用时隙30

‑

44,并且有效载荷3 412使用时隙45

‑

55)。另外,时隙56

‑

63 414是未分配的并且被填充有具有为0的值的填充。未使用的时隙是未分配的并且由0x00数据填充。

[0064]

1024个mtp的每个帧402从链路层控制分组(llcp)404开始,该链路层控制分组404包括信息的四个数据字节。

[0065]

此公开描述了使用usb4传输的displayport2.0信息的隧穿。逻辑上,隧道的两个端点为displayport链路dptx和dprx,如vesa定义的。通过隧道本身,传输了控制和数据,而空闲时,由displayport使用的填充或填补信息从隧道中剥离出来。

[0066]

此公开从dptx的角度描述了一组被保留的隧道显示端口配置数据(dpcd)寄存器,并且从usb4驱动程序(或连接管理器(cm))的角度描述了一组usb4寄存器,以促进usb4驱动程序和dptx之间的通信信道。通过此信道,dptx可以查询可用的带宽的量,并且可以请求并确保一部分用于显示端口使用。

[0067]

本公开的优点对于本领域技术人员来说将是显而易见的。在各种优点之中,有一个优点是usb4带宽被优化,这是因为带宽并未针对显示端口信令被过度分配。另外,当多个流正在共享资源时,dptx可以控制带宽请求并优化其请求的带宽。

[0068]

图5是根据本公开的实施例的示例系统500的示意图,该示例系统500使用显示端口隧穿通过usb结构来将显示端口源耦合到显示端口汇聚结点。系统500可以包括通过usb4集线器504互连到usb4端点506的usb4主机502。usb4主机502类似于图1中描述的usb4主机102。usb4端点506类似于图1中描述的usb4端点106。usb4集线器504类似于图1中描述的usb4集线器104。

[0069]

usb4主机502可以包括usb4主机路由器510。usb4主机路由器510可以包括:主机接口524;显示端口输入(dp_in)适配器526a、526b;以及usb4兼容的端口532。usb4集线器可以包括usb4集线器路由器542。usb4集线器路由器542可以包括usb4兼容的端口550、560和显示端口输出(dp_out)适配器552。dp_out适配器552可以耦合到与dp2.0协议兼容的dp端口554。usb4设备506可以包括usb4设备路由器578。usb4设备路由器578可以包括usb4端口588和具有dp2.0端口554的dp_out适配器592。

[0070]

usb4主机可以包括(或连接到)显示端口源512。显示端口源512可以是图形处理单元或符合dp2.0协议的其他显示端口源。显示端口源512可以通过显示端口链路516a连接到dp_in适配器526a。显示端口源512也可以通过显示端口链路516b连接到dp_in适配器526b。多个显示端口输出信号可以由显示端口源512生成。系统500可以通过显示端口隧穿来支持多个显示端口信号。

[0071]

例如,显示端口源512可以跨链路516a输出第一显示端口信号。该第一显示端口信号可以通过usb4主机502、usb4集线器504和usb设备506跨usb4链路514a路由到显示端口汇聚结点582。第二显示端口汇聚结点594可以直接地链接到usb4集线器504。显示端口源512可以跨链路516b输出第二显示端口信号。第二显示端口信号可以通过usb4链路514b路由到显示端口汇聚结点594。

[0072]

由于带宽需求改变,例如通过增加或减少用于显示端口流的资源,连接管理器520可以使用与usb4驱动程序522和dp_in适配器526a、526b相关联的寄存器来分配带宽。在dptx无法通知usb4驱动程序所需的实际带宽的情况下,可调整的带宽分配防止浪费带宽资源。另外,自适应的带宽分配允许dptx重新平衡可用的带宽,从而允许针对显示端口数据的多个流的带宽分配的优化。

[0073]

连接管理器(cm)520可以是负责枚举、配置和管理域的软件实体。cm 520执行诸如

路径设置/拆卸、热插入/拔出和带宽管理之类的任务。例如,cm 520可以是或可以包括usb驱动程序522。

[0074]

图6是根据本公开的实施例的用于在通用串行总线链路上的显示端口隧穿的带宽分配的过程流程图600。在开始时,通过usb4驱动程序(例如,连接管理器)和显示端口驱动程序(dptx)二者来检查带宽分配管理位设置(602)。cm先前估计了要分配给显示端口的带宽,以尝试最大化分配给dp的带宽。dptx可以读取来自dpcd寄存器的估计的带宽(604)。dptx将估计的带宽报告给操作系统(os)(606)。os可以基于预期的使用、应用、分辨率等来确定期望的或必需的带宽。所请求的带宽被提供给dptx(608)。dptx将所请求的带宽写入到dpcd中(例如,写入到dpcd寄存器的e0031h“请求bw更新”字段中)(610)。

[0075]

dpcd通过dp_in适配器寄存器进行镜像。cm可以读取来自dp_in适配器寄存器(例如,adp_dp_cs_8,7:0)的所请求的带宽(612)。cm可以基于针对显示端口适配器的可用的带宽来确定是否准予所请求的带宽(614)。cm将成功位(如果所请求的带宽被准予)或失败位(如果所请求的带宽未被准予)写入到dp_in适配器寄存器中(616)。cm还将被准予的带宽写入到dp_in适配器寄存器中,并且将irq发送到dptx。

[0076]

在dptx接收irq之后,dptx读取dpcd更新状态位(e0025h),以确定针对带宽分配的请求是否是成功的,并且如果准予是成功的,则dptx可以读取被分配的带宽字段(e0024h)(618)。dptx然后可以使用被分配的带宽进行操作(620)。

[0077]

以下段落提供了根据本公开的实施例的用于执行带宽分配管理的各个方面的示例伪代码。

[0078]

启用带宽分配管理

[0079]

用于dp隧穿的带宽分配管理使用usb4路由器(通过dp_in适配器)、usb4驱动程序(或连接管理器(cm))和dptx驱动程序的支持。默认情况下,用于dp隧穿的带宽分配管理处于关闭状态,并且仅当两个软件实体(usb4驱动程序和dptx驱动程序)写入到其相应的带宽分配管理支持的寄存器时,该模式才会激活。

[0080]

当该模式被激活之后,执行以下流程以针对dp隧穿分配带宽:

[0081]

带宽分配

[0082]

1.dptx读取由cm动态地设置的估计的可用带宽。

[0083]

2.dp_in适配器用usb4驱动程序已经提供的最新的估计来进行响应。

[0084]

3.dptx将此带宽通知回控制或管理dptx的操作系统(os)或其他控制器逻辑。

[0085]

4.os从dptx请求以一定的流特性进行操作,这暗示一定的带宽。

[0086]

5.dptx请求带宽分配。

[0087]

6.dp_in适配器通过与usb4驱动程序的握手请求来分配带宽。

[0088]

7.如果所请求的带宽由usb4驱动程序准予——dp_in适配器将其报告给dptx驱动程序。

[0089]

8.dptx以新的流特性进行操作,并且过程完成。

[0090]

9.如果请求已经失败,则usb4驱动程序提供可能的最大带宽,并且dp_in适配器将其作为新的估计的带宽报告给dptx。

[0091]

10.dptx将通知os它失败了,并且供应新的较低的估计的带宽。

[0092]

11.os将从dptx os请求以新的流特性进行操作,这暗示较低的带宽。

[0093]

12.dptx请求新的带宽分配。

[0094]

13.dp_in适配器准予请求——过程完成。

[0095]

dp带宽改变

[0096]

在存在改变dp流带宽的需要的情况下(例如,操作系统(os)想要使用mst(多个流)在相同的dp端口上改变流的分辨率或禁用流或激活附加的流),带宽分配的相同的过程进行重复。在新的所请求的带宽低于当前分配的带宽的情况下,改变可以被确保成功,并且dp_in适配器将通知usb4驱动程序带宽被释放。

[0097]

重新平衡带宽

[0098]

作为信息的一部分,dptx从dpcd寄存器获取的是dp隧道通过的usb4链路的编号。在多个流通过相同的usb4链路的情况下(这意味着它们共享相同的链路资源),dptx会意识到这一点,并且可以相应地重新平衡请求带宽。

[0099]

dptx(例如,gpu)行为

[0100]

表2提供了在dptx可访问的显示端口源处的添加的显示端口配置数据(dpcd)寄存器的示例。寄存器由dp_in适配器寄存器进行镜像。表3中示出了dp_in适配器寄存器。

[0101]

表2.示例dpcd寄存器

[0102][0103][0104]

设置带宽分配管理模式

[0105]

为了进入带宽分配管理模式:

[0106]

1.dptx读取dpcd e0020h并且验证位7被设置为lb,这指示dp_in适配器和usb4驱动程序二者均支持带宽分配管理模式。

[0107]

2.dptx写入dpcd e0030h,将位7设置为lb。

[0108]

请求带宽分配

[0109]

在进入带宽分配管理模式之后,dptx执行以下流程:

[0110]

1.dptx读取dpcd e0022h。所有带宽字段中的带宽的粒度均根据此字节。

[0111]

2.dptx读取dpcd e0023h以了解估计的带宽。

[0112]

3.dptx根据估计的带宽来向os发送带宽。

[0113]

4.当由os针对所要求的带宽进行指示时,dptx用所请求的带宽写入dpcd e0031h。

[0114]

5.dptx等待irq被接收。

[0115]

6.dptx读取e0025h。

[0116]

6.1如果位0被设置为1b:

[0117]

6.1.1 dptx将dpcd e0025h位0写入为1b的值。

[0118]

6.1.2过程已经结束。

[0119]

6.2如果位1被设置为1b:

[0120]

6.2.1 dptx将dpcd e0025h位1写入为1b的值。

[0121]

6.2.2 dptx重复上述步骤2的过程。

[0122]

改变带宽分配

[0123]

在os想要改变所请求的带宽的情况下,dptx将从步骤2开始遵循c程序。如果os正在减少所请求的带宽,则确保该过程将成功。

[0124]

估计的带宽改变

[0125]

1.dp_in适配器发起到dptx的irq。

[0126]

2.dptx读取e0025h

[0127]

2.1如果位2被设置为1b

[0128]

2.1.1 dptx将dpcd e0025h位2写入为1b的值。

[0129]

2.1.2具有os的dptx决定是否改变所请求的带宽,并且如果是,则遵循c程序。

[0130]

带宽共享

[0131]

当附接了多个屏幕时,dptx可以读取dpcd e0021h,其指示当退出usb4路由器时dp隧道通过的通道适配器编号。通过读取来自所有被服务的端口的通道适配器编号,它可以推断哪些流共享相同的通道适配器,并且可以通过上面描述的“请求带宽分配”程序来按需平衡带宽。

[0132]

dp_in适配器行为

[0133]

表3提供了dp_in适配器寄存器的示例寄存器条目。dp_in适配器寄存器由dpcd寄存器进行镜像,如上所示。

[0134]

表3.示例dp_in适配器寄存器条目

[0135][0136][0137]

配置

[0138]

当usb4驱动程序启用dp隧穿时,它设置:

[0139]

adp_dp_cs_2[12:11](粒度);

[0140]

adp_dp_cs_2[18:13](通道适配器编号);

[0141]

如果adp_dp_cs_2[20]支持带宽分配管理模式,则将adp_dp_cs_2[20](cm带宽管理模式支持)设置为1b;

[0142]

adp_dp_cs_2[31:24](估计的带宽)。

[0143]

当dptx读取以下dpcd时,dp_in适配器从以下寄存器中复制值:

[0144]

dpcd e0020h[7]<=adp_dp_cs_2[20];

[0145]

dpcd e0021h[5:0]<=adp_dp_cs_2[18:13];

[0146]

dpcd e0022h[7:0]<={0,adp_dp_cs_2[12:11]};

[0147]

dpcd e0023h[7:0]<=adp_dp_cs_2[31:24];

[0148]

设置带宽分配管理模式

[0149]

如果dptx将dpcd e0030h[0]写入1b,则意味着它启用了带宽分配管理模式,dp_in适配器将adp_dp_cs_8[30](dptx带宽管理模式支持)设置为1b。

[0150]

请求带宽分配

[0151]

当dptx写入dpcd e0031h时,设置请求带宽更新字段,dp_in适配器进行以下操作:

[0152]

设置adp_dp_cs_8[7:0](所请求的带宽)<=请求带宽更新;

[0153]

将adp_dp_cs_8[31](请求)设置为1b;

[0154]

将adp_dp_cs_2[10](确认)设置为0b;

[0155]

向usb4驱动程序发送通知分组(带有用于带宽分配流程的新的事件代码);

[0156]

轮询adp_dp_cs_2[10](确认),直到其被设置为1b为止;

[0157]

读取dp_status[31:24](被准予的带宽);

[0158]

设置e0024h<=dp_status[31:24](被准予的带宽);

[0159]

如果被准予的带宽>=所请求的带宽请求是成功的,则

[0160]

a.将e0025h位1设置为1b(成功);

[0161]

否则

[0162]

a.设置e0024h<=dp_status[31:24](被准予的带宽);

[0163]

b.将e0025h位0设置为1b(失败);

[0164]

c.将e0025h位2设置为1b(估计的带宽已改变);

[0165]

发送irq。

[0166]

过程结束。

[0167]

通知估计的带宽改变

[0168]

当usb4驱动程序改变adp_dp_cs_2[31:24](估计的带宽)时,dp_in适配器进行以下操作:

[0169]

将e0025h位2设置为1b(估计的带宽已改变);

[0170]

发送irq;

[0171]

过程结束。

[0172]

usb4驱动程序[cm]行为

[0173]

cm使用表3定义的寄存器。

[0174]

displayport隧穿设置

[0175]

当cm配置displayport隧穿时,它针对dp_in适配器行为设置上面描述的寄存器:配置。另外,cm将dp流的估计的带宽写入到adp_dp_cs_2[31:24](估计的带宽)中。

[0176]

分配带宽

[0177]

当cm接收到包含用于带宽分配的新的事件代码的通知分组时,cm将执行以下步骤:

[0178]

1.cm计算针对该dp_in适配器的总可用的带宽(包括任何已经被分配的带宽),并将其分配给dp_in适配器;

[0179]

2.cm将被分配的带宽写入dp_status[31:24](被准予的带宽);以及

[0180]

3.cm将adp_dp_cs_2[10](确认)设置为1b。

[0181]

估计的带宽维护

[0182]

每当cm处理usb4端口上的带宽时,cm都会尽快更新adp_dp_cs_2[31:24](估计的带宽)。

[0183]

参考图7,示出了由将一组组件互连的点对点链路组成的结构的实施例。系统700包括处理器705和系统存储器710,处理器705和系统存储器710耦合到控制器集线器715。处理器705包括任何处理元件(例如,微处理器、主机处理器、嵌入式处理器、协处理器或其他处理器)。处理器705通过前端总线(fsb)706耦合到控制器集线器715。在一个实施例中,fsb 706是如下面描述的串行点对点互连。在另一个实施例中,链路706包括符合不同的互连标准的串行差分互连架构。

[0184]

系统存储器710包括任何存储器设备(例如,随机存取存储器(ram)、非易失性(nv)存储器或由系统700中的设备可访问的其他存储器)。系统存储器710通过存储器接口716耦合到控制器集线器715。存储器接口的示例包括双倍数据速率(ddr)存储器接口、双通道ddr存储器接口和动态ram(dram)存储器接口。

[0185]

在一个实施例中,控制器集线器715是外围组件快速互连(pcie或pcie)互连层次结构中的根集线器、根复合体或根控制器。控制器集线器715的示例包括芯片组、存储器控制器集线器(mch)、北桥、互连控制器集线器(ich)、南桥和根端口控制器/集线器。术语芯片组通常指代两个物理上独立的控制器集线器(即,耦合到互连控制器集线器(ich)的存储器控制器集线器(mch))。注意,当前的系统通常包括与处理器705集成的mch,而控制器715用于以如下面描述的类似的方式与i/o设备通信。在一些实施例中,对等路由是通过根复合体715来可选地支持的。

[0186]

这里,控制器集线器715通过串行链路719耦合到交换机/桥接器720。输入/输出模块717和721(其也可以被称为接口/端口717和721)包括/实现分层协议栈以提供控制器集线器715和交换机720之间的通信。在一个实施例中,多个设备能够被耦合到交换机720。

[0187]

交换机/桥接器720将来自设备725的分组/消息向上游(即,朝着根复合体沿层次结构向上)路由到控制器集线器715,以及从处理器705或系统存储器710向下游(即,远离根端口控制器沿层次结构向下)路由到设备725。在一个实施例中,交换机720被称为多个虚拟的pci到pci桥接设备的逻辑组装件。设备725包括要耦合到电子系统的任何内部或外部的设备或组件(例如,i/o设备、网络接口控制器(nic)、附加卡、音频处理器、网络处理器、硬盘驱动器、存储设备、cd/dvd rom、监视器、打印机、鼠标、键盘、路由器、便携式存储设备、火线设备、通用串行总线(usb)设备、扫描仪和其他输入/输出设备)。通常在pcie白话中,例如设备被称为端点。尽管没有被具体示出,但是设备725可以包括pcie到pci/pci

‑

x桥接器,以支持旧式或其他版本的pci设备。pcie中的端点设备通常被分类为旧式、pcie或根复合体集成端点。

[0188]

图形加速度计730还通过串行链路732耦合到控制器集线器715。在一个实施例中,图形加速度计730被耦合到mch,mch被耦合到ich。交换机720和相应地i/o设备725然后被耦合到ich。i/o模块731和718还用于实现分层协议栈以在图形加速度计730和控制器集线器715之间进行通信。类似于上面的mch讨论,图形控制器或图形加速度计730本身可以集成在处理器705中。

[0189]

转到图8,示出了分层协议栈的实施例。分层协议栈700包括任何形式的分层通信栈(例如,快速路径互连(qpi)栈、pcie栈、下一代高性能计算互连栈或其他分层栈)。尽管下面紧接的参考图7

‑

10的讨论是关于pcie栈的,但是相同的构思可以被应用于其他互连栈。在一个实施例中,协议栈800是pcie协议栈,其包括事务层805、链路层810和物理层820。接口(例如,图7中的接口717、718、721、722、726和731)可以被表示为通信协议栈800。作为通信协议栈的表示也可以被称为实现/包括协议栈的模块或接口。

[0190]

pci express使用分组以在组件之间传送信息。在事务层805和数据链路层810中形成分组以将信息从发送组件携带到接收组件。当被发送的分组流过其他层时,它们被扩展有处理那些层处的分组所必需的附加的信息。在接收侧,发生反向过程,并且分组从其物理层820表示变换到数据链路层810表示,并且最终(针对事务层分组)变换到可以由接收设

备的事务层705处理的形式。

[0191]

事务层

[0192]

在一个实施例中,事务层805用于提供设备的处理核心和互连架构(例如,数据链路层810和物理层820)之间的接口。在这方面,事务层805的主要责任是分组的组装和拆卸(即,事务层分组或tlp)。事务层805通常管理tlp的基于信用的流控制。pcie实现分离事务(即,具有由时间分隔的请求和响应的事务),以允许链路在目标设备收集响应数据的同时携带其他流量。

[0193]

另外,pcie利用基于信用的流控制。在此方案中,设备在事务层805中针对接收缓冲器的每一个通知初始的信用量。在链路的相对端处的外部设备(例如,图7中的控制器集线器715)对由每个tlp消费的信用数进行计数。如果事务未超过信用限制,则可以发送事务。在接收到响应后,恢复信用的量。信用方案的一个优点是,信用返还的延时不会影响性能,前提是没有遇到信用限制。

[0194]

在一个实施例中,四个事务地址空间包括配置地址空间、存储器地址空间、输入/输出地址空间和消息地址空间。存储器空间事务包括读取请求和写入请求中的一个或多个以往返存储器映射的位置传送数据。在一个实施例中,存储器空间事务能够使用两种不同的地址格式(例如,诸如32位地址之类的短地址格式,或诸如64位地址之类的长地址格式)。配置空间事务用于访问pcie设备的配置空间。到配置空间的事务包括读取请求和写入请求。消息空间事务(或简称为消息)被定义以支持pcie代理之间的带内通信。

[0195]

因此,在一个实施例中,事务层805组装分组报头/有效载荷706。当前的分组报头/有效载荷的格式可以在pcie规范网站处的pcie规范中找到。

[0196]

快速参考图9,示出了pcie事务描述符的实施例。在一个实施例中,事务描述符900是用于携带事务信息的机制。在这方面,事务描述符900支持系统中的事务的标识。其他潜在的用途包括跟踪默认事务排序的修改以及事务与信道的关联。

[0197]

事务描述符900包括全局标识符字段902、属性字段904和信道标识符字段906。在所示的示例中,全局标识符字段902被描绘为包括本地的事务标识符字段908和源标识符字段910。在一个实施例中,全局事务标识符902对于所有未完成的请求是唯一的。

[0198]

根据一种实施方式,本地的事务标识符字段908是由请求代理生成的字段,并且它对于需要完成该请求代理的所有未完成的请求是唯一的。此外,在此示例中,源标识符910唯一地标识pcie层次结构内的请求者代理。因此,与源id 910一起,本地的事务标识符908字段提供层次结构域内的事务的全局标识。

[0199]

属性字段904指定事务的特性和关系。在这方面,属性字段904潜在地用于提供允许事务的默认处理的修改的附加信息。在一个实施例中,属性字段904包括优先级字段912、被保留的字段914、排序字段916和无探听字段918。这里,优先级子字段912可以由发起者修改以向事务指派优先级。被保留的属性字段914被保留用于将来或供应商定义的用途。可以使用被保留的属性字段来实现使用优先级或安全性属性的可能的使用模型。

[0200]

在此示例中,排序属性字段916用于供应传达可以修改默认排序规则的排序的类型的可选信息。根据一个示例实施方式,排序属性“0”表示默认排序规则要应用,其中,排序属性“1”表示宽松的排序,其中,写入可以在相同的方向上传递写入,并且读取完成可以在相同的方向上传递写入。利用探听属性字段918以确定是否探听了事务。如图所示,信道id

字段906标识事务与之相关联的信道。

[0201]

链路层

[0202]

链路层810(也被称为数据链路层810)充当事务层805和物理层820之间的中间级。在一个实施例中,数据链路层810的责任是提供用于在链路的两个组件之间交换事务层分组(tlp)的可靠的机制。数据链路层810的一侧接受由事务层805组装的tlp,应用分组序列标识符811(即,标识号或分组号),计算并应用错误检测码(即,crc 812),并将所修改的tlp提交给物理层820以用于跨物理设备到外部设备的传输。

[0203]

物理层

[0204]

在一个实施例中,物理层820包括逻辑子块821和电气子块822,以物理地将分组发送到外部的设备。这里,逻辑子块821负责物理层821的“数字”功能。在这方面,逻辑子块包括用于准备由物理子块822发送的传出信息的发送部分,以及用于在将所接收的信息传递到链路层810之前识别和准备所接收的信息的接收器部分。

[0205]

物理块822包括发送器和接收器。发送器由逻辑子块821供应符号,发送器将符号序列化并发送到外部设备上。接收器被供应有来自外部设备的序列化符号,并将所接收的信号变换为位流。位流被反序列化并供应给逻辑子块821。在一个实施例中,采用8b/10b发送码,其中,发送/接收十位符号。这里,特殊符号用于利用帧823对分组进行成帧。另外,在一个示例中,接收器还提供从传入串行流中恢复的符号时钟。

[0206]

如上所述,尽管参考pcie协议栈的特定实施例讨论了事务层805、链路层810和物理层820,但是分层协议栈不限于此。事实上,可以包括/实现任何分层协议。作为示例,表示为分层协议的端口/接口包括:(1)用于组装分组的第一层,即,事务层;用于对分组进行排序的第二层,即,链路层;以及发送分组的第三层,即,物理层。作为特定示例,利用了公共标准接口(csi)分层协议。

[0207]

接下来参考图10,示出了pcie串行点对点结构的实施例。尽管示出了pcie串行点对点链路的实施例,但是串行点对点链路不限于此,这是由于它包括用于发送串行数据的任何发送路径。在所示的实施例中,基本pcie链路包括两个低压差分驱动的信号对:发送对106/1011和接收对1012/1007。因此,设备1005包括用于将数据发送到设备1010的发送逻辑1006以及用于从设备1010接收数据的接收逻辑1007。换言之,在pcie链路中包括两个发送路径(即,路径1016和1017),以及两个接收路径(即,路径1018和1019)。

[0208]

发送路径指代用于发送数据的任何路径(例如,发送线、铜线、光学线路、无线通信信道、红外通信链路或其他通信路径)。两个设备(例如,设备1005和设备1010)之间的连接被称为链路(例如,链路1015)。链路可以支持一个通道——每个通道表示一组差分信号对(一对用于发送,一对用于接收)。为了扩展带宽,链路可以聚合由xn表示的多个通道(其中,n是任何支持的链路宽度,例如1、2、4、8、12、16、32、64或更宽)。

[0209]

差分对指代两个发送路径(例如,线路1016和1017),以用于发送差分信号。作为示例,当线路1016从低电压电平切换到高电压电平(即,上升沿)时,线路1017从高逻辑电平驱动到低逻辑电平(即,下降沿)。差分信号潜在地展示更好的电气特性(例如,更好的信号完整性,即,交叉耦合、电压过冲/下冲、振铃等)。这允许更好的定时窗口,其实现更快的发送频率。

[0210]

注意,上面描述的装置、方法和系统可以在如上所述的任何电子设备或系统中实

现。作为特定说明,以下附图提供了用于利用如本文所描述的公开的示例性系统。随着下面的系统被更详细地描述,从上面的讨论中公开、描述和重新讨论了多个不同的互连。并且显而易见的是,上面描述的进展可以应用于那些互连、结构或架构中的任一个。

[0211]

转向图11,示出了利用处理器形成的示例性计算机系统的框图,该处理器包括用于执行指令的执行单元,其中,互连的一个或多个实现根据本公开的一个实施例的一个或多个特征。系统1100包括诸如处理器1102之类的组件,其例如在本文所描述的实施例中,采用根据本公开的包括逻辑的执行单元来执行用于过程数据的算法。系统1100代表可从加利福尼亚州圣克拉拉的英特尔公司获得的基于pentium iii

tm

、pentium 4

tm

、xeoni、itanium、xscalem和/或strongarm州微处理器的处理系统,但也可以使用其他系统(包括具有其他微处理器的pc、工程工作站、机顶盒等)。在一个实施例中,样本系统1000执行可从华盛顿州雷德蒙德的微软公司获得的windows

tm

操作系统的版本,但也可以使用其他操作系统(例如,unix和linux)、嵌入式软件和/或图形用户界面。因此,本公开的实施例不限于硬件电路和软件的任何特定组合。

[0212]

实施例不限于计算机系统。本公开的替代实施例可以在诸如手持设备和嵌入式应用之类的其他设备中使用。手持设备的一些示例包括蜂窝电话、互联网协议设备、数码相机、个人数字助理(pda)和手持pc。嵌入式应用可以包括微控制器、数字信号处理器(dsp)、片上系统、网络计算机(netpc)、机顶盒、网络集线器、广域网(wan)交换机或可以执行根据至少一个实施例的一个或多个指令的任何其他系统。

[0213]

在此示出的实施例中,处理器1102包括一个或多个执行单元1008,以实现用于执行至少一个指令的算法。可以在单处理器台式机或服务器系统的上下文中描述一个实施例,但是替代实施例可以被包括在多处理器系统中。系统1100是“集线器”系统架构的示例。计算机系统1100包括用于处理数据信号的处理器1102。作为一个说明性的示例,处理器1102包括例如复杂指令集计算机(cisc)微处理器、精简指令集计算(risc)微处理器、超长指令字(vliw)微处理器、实现指令集的组合的处理器、或者诸如数字信号处理器之类的任何其他处理器设备,作为示例。处理器1102耦合到处理器总线1110,该处理器总线1110在处理器1102与系统1100中的其他组件之间发送数据信号。系统1100的元件(例如,图形加速度计1112、存储器控制器集线器1116、存储器1120、i/o控制器集线器1124、无线收发器1126、快闪bios 1028、网络控制器1134、音频控制器1136、串行扩展端口1138、i/o控制器1140等)执行其常规的功能,这些功能对于本领域技术人员来说是众所周知的。

[0214]

在一个实施例中,处理器1102包括1级(l1)内部高速缓冲存储器1104。取决于架构,处理器1102可以具有单个内部高速缓存或多级内部高速缓存。其他实施例包括取决于特定的实施方式和需求的内部和外部高速缓存二者的组合。寄存器文件1106用于将各种类型的数据存储在各种寄存器中,包括整数寄存器、浮点寄存器、向量寄存器、分组寄存器(banked register)、影子寄存器、检查点寄存器、状态寄存器和指令指针寄存器。

[0215]

执行单元1108(包括用于执行整数和浮点运算的逻辑)还驻留在处理器1102中。在一个实施例中,处理器1102包括用于存储微码的微码(ucode)rom,微码当被执行时,用于针对某些宏指令执行算法或处理复杂的场景。这里,微码是潜在地可更新的,以处理处理器1102的逻辑错误/修复。针对一个实施例,执行单元1108包括用于处理打包指令集合1109的逻辑。通过将打包指令集合1109与执行指令的相关联的电路一起包括在通用处理器1102的

指令集合中,可以使用通用处理器1102中的打包数据来执行由许多多媒体应用使用的操作。因此,许多多媒体应用通过将处理器的数据总线的全宽度用于对打包数据执行操作来更高效地被加速和执行。这潜在地消除了跨处理器的数据总线传送更小的数据单元来执行一个或多个操作(一次一个数据元素)的需要。

[0216]

执行单元1108的替代实施例也可以在微控制器、嵌入式处理器、图形设备、dsp和其他类型的逻辑电路中使用。系统1100包括存储器1120。存储器1020包括动态随机存取存储器(dram)设备、静态随机存取存储器(sram)设备、闪速存储器设备或其他存储器设备。存储器1120存储由数据信号表示的指令和/或数据,数据信号要由处理器1102执行。

[0217]

注意,可以在图11所示的一个或多个互连上利用本公开的前述特征或方面中的任一个。例如,用于耦合处理器1102的内部单元的未示出的管芯上互连(odi)实现了上面描述的本公开的一个或多个方面。或者,本公开与以下各项相关联:处理器总线1110(例如,英特尔快速路径互连(qpi)或其他已知的高性能计算互连)、到存储器1120的高带宽存储器路径1118、到图形加速度计1112的点对点链路(例如,外围组件快速互连(pcie)兼容的结构)、控制器集线器互连1122、i/o或用于耦合其他所示的组件的其他互连(例如,usb、pci、pcie)。这样的组件的一些示例包括音频控制器1136、固件集线器(闪存bios)1128、无线收发器1126、数据存储装置1124、包含用户输入和键盘接口1142的旧式i/o控制器1110、串行扩展端口1138(例如,通用串行总线(usb))和网络控制器1134。数据存储设备1124可以包括硬盘驱动器、软盘驱动器、cd

‑

rom设备、闪速存储器设备或其他大容量存储设备。

[0218]

现在参考图12,示出的是根据本公开的实施例的第二系统1200的框图。如图12所示,多处理器系统1200是点对点互连系统,并且包括经由点对点互连1250耦合的第一处理器1270和第二处理器1280。处理器1270和1280中的每一个可以是处理器的某个版本。在一个实施例中,1252和1254是串行点对点一致性互连结构(例如,英特尔的快速路径互连(qpi)架构)的一部分。因此,本公开可以在qpi架构内实现。

[0219]

尽管仅用两个处理器1270、1280示出,但是应当理解的是,本公开的范围不限于此。在其他实施例中,一个或多个附加的处理器可以存在于给定的处理器中。

[0220]

处理器1270和1280被示出分别包括集成存储器控制器单元1272和1282。处理器1270还包括作为其总线控制器单元的一部分的点对点(p

‑

p)接口1276和1278;类似地,第二处理器1280包括p

‑

p接口1286和1288。处理器1270、1280可以使用p

‑

p接口电路1278、1288经由点对点(p

‑

p)接口1250交换信息。如图12所示,imc 1272和1282将处理器耦合到相应的存储器,即,存储器1232和存储器1234,其可以是本地附接到相应的处理器的主存储器的部分。

[0221]

处理器1270、1280各自使用点对点接口电路1276、1294、1286、1298经由个体的p

‑

p接口1252、1254与芯片组1290交换信息。芯片组1290还沿着高性能图形互连1239经由接口电路1292与高性能图形电路1238交换信息。

[0222]

共享高速缓存(未示出)可以被包括在任一处理器中或在两个处理器的外部;还经由p

‑

p互连与处理器连接,使得如果处理器被置于低功率模式下,则处理器中的任一个或二者的本地高速缓存信息可以存储在共享高速缓存中。

[0223]

芯片组1290可以经由接口1296耦合到第一总线1216。在一个实施例中,第一总线1216可以是外围组件互连(pci)总线,或者诸如pci express总线或另一个第三代i/o互连

总线之类的总线,但本公开的范围不限于此。

[0224]

如图12所示,各种i/o设备1214耦合到第一总线1216以及将第一总线1216耦合到第二总线1220的总线桥接器1218。在一个实施例中,第二总线1220包括低引脚数(lpc)总线。在一个实施例中,各种设备耦合到第二总线1220,包括例如键盘和/或鼠标1222、通信设备1227和存储单元1228(例如,磁盘驱动器或其他大容量存储设备,其通常包括指令/代码和数据1230)。此外,音频i/o 1224被示出耦合到第二总线1220。注意,其他架构是可能的,其中,被包括的组件和互连架构变化。例如,代替图12的点对点架构,系统可以实现多点总线或其他这种架构。

[0225]

使用平台中存在的各种惯性和环境传感器,可以实现许多不同的用例。这些用例实现包括感知计算的高级计算操作,并且还允许关于电源管理/电池寿命、安全性和系统响应性的增强。

[0226]

例如,关于电源管理/电池寿命问题,至少部分地基于来自环境光传感器的信息,确定平台的位置中的环境光条件,并相应地控制显示器的强度。因此,在某些光照条件下减少了操作显示器的功耗。

[0227]

至于安全性操作,基于从传感器获得的上下文信息(例如,位置信息),可以确定是否允许用户访问某些安全文档。例如,可以允许用户在工作场所或家庭位置处访问这样的文档。然而,当平台位于公共位置时,将阻止用户访问这样的文档。在一个实施例中,此确定是基于位置信息的,例如经由gps传感器或相机对地标的识别所确定的位置信息。其他安全性操作可以包括提供在彼此的近距离内的设备的配对(例如,如本文所描述的便携式平台和用户的台式计算机、移动电话等)。某些共享在一些实施方式中是经由近场通信实现的(当这些设备如此配对时)。然而,当设备超出某个范围时,可能会禁用这种共享。此外,当将如本文所描述的平台与智能手机配对时,警报可以被配置为当设备在公共场所中移动超过距彼此预定距离时被触发。作为对比,当这些配对的设备处于安全位置(例如,工作场所或家庭位置)时,这些设备可以超过此预定限制而不会触发这种警报。

[0228]

也可以使用传感器信息来增强响应性。例如,即使当平台处于低功率状态时,仍然可以启用传感器以相对低的频率运行。因此,确定了平台的位置的任何变化,例如,如由惯性传感器、gps传感器等确定的。如果尚未注册这样的改变,则会发生与先前的无线集线器(例如,wi

‑

fitm接入点或类似的无线使能器(wireless enabler))的更快的连接,这是因为在这种情况下无需扫描可用的无线网络资源。因此,实现了当从低功率状态唤醒时的更高级别的响应性。

[0229]

应当理解的是,如本文所描述的,可以使用经由平台内的集成传感器获得的传感器信息来实现许多其他用例,并且以上示例仅出于说明的目的。使用本文所描述的系统,感知计算系统可以允许包括手势识别的替代输入形态的添加,并且使得系统能够感测用户的操作和意图。

[0230]

在一些实施例中,可以存在一个或多个红外或其他热感测元件,或用于感测用户的存在或移动的任何其他元件。这样的感测元件可以包括一起工作、顺序工作或二者的多个不同的元件。例如,感测元件包括提供初始感测(例如,光或声音投射)之后通过例如超声飞行时间相机或图案光相机来针对手势检测进行感测的元件。

[0231]

同样在一些实施例中,该系统包括光发生器以产生照明线。在一些实施例中,此线

提供了关于虚拟边界的视觉提示,即,空间中的虚构或虚拟位置,其中,用户通过或突破虚拟边界或平面的动作被解释为与计算系统接合的意图。在一些实施例中,当计算系统转变为关于用户的不同的状态时,照明线可以改变颜色。照明线可以用于为空间中的虚拟边界的用户提供视觉提示,并且可以由系统用于确定计算机关于用户的状态转变,包括确定用户何时希望与计算机接合。

[0232]

在一些实施例中,计算机感测用户的位置并且操作以将通过虚拟边界的用户的手的移动解释为指示用户与计算机接合的意图的手势。在一些实施例中,在用户通过虚拟线或平面时,由光发生器生成的光可以改变,从而向用户提供视觉反馈,即用户已经进入了用于提供手势以向计算机提供输入的区域。

[0233]

显示屏可以提供关于用户的计算系统的状态转变的视觉指示。在一些实施例中,以第一状态提供第一屏幕,其中,用户的存在例如通过使用感测元件中的一个或多个来由系统感测。

[0234]

在一些实施方式中,该系统例如通过面部识别来感测用户身份。这里,可以在第二状态下提供到第二屏幕的转变,其中,计算系统已经识别出用户身份,其中,屏幕向用户提供了用户已经转变到新状态的视觉反馈。到第三屏幕的转变可以在用户已经确认对用户的识别的第三状态下发生。

[0235]

在一些实施例中,计算系统可以使用转变机制来针对用户确定虚拟边界的位置,其中,虚拟边界的位置可以随着用户和上下文而变化。计算系统可以生成光(例如,照明线),以指示用于与系统接合的虚拟边界。在一些实施例中,计算系统可以处于等待状态,并且可以以第一颜色产生光。计算系统可以例如通过使用感测元件感测用户的存在和移动来检测用户是否已经到达超过虚拟边界。

[0236]

在一些实施例中,如果已经检测到用户已经越过虚拟边界(例如,用户的手比虚拟边界线更靠近计算系统),则计算系统可以转变到用于接收来自用户的手势输入的状态,其中,用于指示转变的机制可以包括指示虚拟边界改变为第二颜色的光。

[0237]

在一些实施例中,计算系统然后可以确定是否检测到手势移动。如果检测到手势移动,则计算系统可以继续进行手势识别过程,该过程可以包括使用来自手势数据库的数据,该手势数据库可以驻留在计算设备的存储器中,或者可以由计算设备以其他方式访问。

[0238]

如果识别出用户的手势,则计算系统可以响应于输入而执行功能,并且如果用户在虚拟边界内,则返回以接收附加的手势。在一些实施例中,如果手势未被识别,则计算系统可以转变为错误状态,其中,用于指示错误状态的机制可以包括指示虚拟边界改变为第三颜色的光,并且如果用户在虚拟边界内用于与计算系统接合,则系统返回以接收附加的手势。

[0239]

如上所述,在其他实施例中,系统可以被配置为可以在至少两种不同的模式(平板电脑模式和笔记本电脑模式)下使用的可转换的平板电脑系统。可转换的系统可以具有两个面板(即,显示面板和基本面板),以使得在平板电脑模式下,两个面板在彼此之上堆叠布置。在平板电脑模式下,显示面板朝外,并且可以提供如常规的平板电脑中找到的触摸屏功能。在笔记本电脑模式下,两个面板可以以打开的翻盖配置来布置。

[0240]

在各种实施例中,加速度计可以是具有至少50hz的数据速率的3轴加速度计。还可以包括陀螺仪,其可以是三轴陀螺仪。另外,可能存在电子罗盘/磁力计。而且,可以提供一

个或多个接近传感器(例如,用于打开以感测人何时接近(或不接近)系统并调整功率/性能以延长电池寿命的盖子)。针对一些os的传感器融合能力(包括加速度计、陀螺仪和罗盘)可以提供增强的特征。另外,经由具有实时时钟(rtc)的传感器集线器,当系统的其余部分处于低功率状态时,可以实现来自传感器机制的唤醒以接收传感器输入。

[0241]

在一些实施例中,内部盖子/显示器打开开关或传感器用于指示盖子何时关闭/打开,并且可以用于将系统置于已连接的待机状态(connected standby)下或自动从已连接的待机状态唤醒。其他系统传感器可以包括用于内部处理器、存储器和皮肤温度监视的acpi传感器,以基于感测到的参数来实现对处理器和系统操作状态的改变。

[0242]

在实施例中,os可以是实现已连接的待机的8os(在本文中也被称为win8 cs)。windows 8已连接的待机或具有类似的状态的另一个os可以经由如本文所描述的平台提供非常低的超闲置电源,以使得应用能够以非常低的功耗保持连接,例如,连接到基于云的位置。该平台可以支持3种电源状态,即,屏幕打开(正常);已连接的待机(默认为“关闭”状态);和关机(功耗为零瓦)。因此,在已连接的待机状态下,即使屏幕是关闭的,平台在逻辑上是打开的(在最低功率电平处)。在这种平台中,可以使电源管理对应用透明并保持恒定的连接性,部分原因是卸载技术使得功率最低的组件能够执行操作。

[0243]

贯穿此说明书引用“一个实施例”或“实施例”意指结合实施例描述的特定的特征、结构或特性被包括在本公开的至少一个实施例中。因此,贯穿本说明书各处出现的短语“在一个实施例中”或“在实施例中”不一定都指代相同的实施例。此外,可以以任何适合的方式在一个或多个实施例中组合特定的特征、结构或特性。

[0244]

在前述说明书中,已经参考特定示例性实施例给出了详细描述。然而,将显而易见的是,可以对其进行各种修改和改变,而不偏离如所附权利要求中阐述的本公开的更广泛的精神和范围。说明书和附图因此应被视为说明性的意义而非限制性的意义。此外,实施例和其他示例性语言的前述使用不一定指代相同的实施例或相同的示例,而是可以指代不同和独特的实施例以及潜在地指代相同的实施例。

[0245]

以上描述了实施例的各个方面和组合,其中的一些由以下示例表示:

[0246]

示例1是一种装置,其包括显示端口输入(dp_in)适配器,该dp_in适配器包括dp_in适配器寄存器;以及连接管理器逻辑,其用于:接收通知消息,该通知消息用于请求针对dp_in适配器的带宽分配,确定带宽可用于dp_in适配器,以及将新的带宽分配写入到dp_in适配器寄存器中的被保留用于被准予的带宽的指示的寄存器中。

[0247]

示例2可以包括示例1的主题,dp_in适配器用于:从dp_in适配器寄存器中读取所请求的带宽寄存器值;以及向连接管理器发送通知消息以请求带宽分配。

[0248]

示例3可以包括示例1

‑

2中的任一个的主题,dp_in适配器用于根据对应的显示端口配置数据(dpdp)寄存器值来填充dp_in适配器寄存器值。

[0249]

示例4可以包括示例1

‑

3中的任一个的主题,连接管理器用于:将显示端口隧穿带宽管理支持位写入dp_in适配器寄存器的连接管理器带宽管理模式支持字段;以及将估计的带宽值写入到dp_in适配器寄存器的估计带宽寄存器字段中。

[0250]

示例5可以包括示例4的主题,连接管理器用于估计dp_in适配器的带宽分配,并且将估计的带宽分配写入到估计带宽寄存器字段中。

[0251]

示例6可以包括示例1

‑

5中的任一个的主题,连接管理器用于:确定针对dp_in适配

器分配的总带宽;以及将针对dp_in适配器分配的总带宽写入到dp_in适配器寄存器中的被保留用于对被准予的带宽的指示的寄存器中。

[0252]

示例7可以包括示例1

‑

6中的任一个的主题,进一步包括:通用串行总线(usb)主机设备;以及包括dp_in适配器的usb主机路由器。

[0253]

示例8可以包括示例1

‑

7中的任一个的主题,其中,连接管理器包括通用串行总线(usb)驱动程序。

[0254]

示例9是一种装置,其包括:显示端口发送器(dptx),其包括显示端口配置数据(dpcd)寄存器集合,dptx用于:读取来自dpcd寄存器集合的估计的带宽分配;向控制器逻辑发送估计的带宽分配;接收来自控制器逻辑的用于增加dptx的带宽的指示;以及将所请求的带宽写入到dpcd寄存器集合的请求带宽更新字段中。

[0255]

示例10可以包括示例9的主题,dptx用于读取带宽分配管理模式位以确定连接设备支持带宽分配管理;写入dpcd寄存器集合的dptx带宽管理支持字段。

[0256]

示例11可以包括示例9

‑

10中的任一个的主题,dptx用于:接收与所请求的带宽相关联的中断;读取dpcd寄存器集合中的状态寄存器;基于状态寄存器的带宽请求成功字段来确定所请求的带宽被准予。

[0257]

示例12可以包括示例9

‑

11中的任一个的主题,dptx用于使用被准予的所请求的带宽来发送数据。

[0258]

示例13可以包括示例9

‑

12中的任一个的主题,其中,控制器逻辑包括操作系统。

[0259]

示例14是一种包括主机路由器的系统,主机路由器包括连接管理器逻辑、显示端口适配器、以及显示端口适配器寄存器,显示端口适配器寄存器包括显示端口适配器寄存器值。显示端口源设备包括:连接到显示端口适配器的显示端口发送器;显示端口配置数据(dpcd)寄存器,其包括用于显示端口的显示端口配置寄存器值,显示端口发送器用于写入dpcd寄存器。显示端口适配器用于将dpcd寄存器值映射到显示端口适配器寄存器。连接管理器逻辑用于:接收请求针对显示端口发送器的带宽分配的通知消息,确定针对显示端口发送器的被分配的带宽,以及将被分配的带宽写入到显示端口适配器寄存器中。

[0260]

示例15可以包括示例14的主题,显示端口适配器用于:读取来自显示端口适配器寄存器的所请求的带宽寄存器值;以及向连接管理器逻辑发送通知消息,以请求带宽分配。

[0261]

示例16可以包括示例14

‑

15中的任一个的主题,显示端口适配器用于根据对应的dpcd寄存器值来填充显示端口适配器寄存器值。

[0262]

示例17可以包括示例14

‑

16中的任一个的主题,连接管理器逻辑用于:将显示端口隧穿带宽管理支持位写入显示端口适配器寄存器的连接管理器带宽管理模式支持字段;以及将估计的带宽值写入到显示端口适配器寄存器的估计带宽寄存器字段中。

[0263]

示例18可以包括示例17的主题,连接管理器逻辑用于估计针对显示端口适配器的带宽分配并且将估计的带宽分配写入到估计带宽寄存器字段中。

[0264]

示例19可以包括示例14

‑

18中的任一个的主题,连接管理器逻辑用于:确定针对显示端口适配器分配的总带宽;以及将针对显示端口适配器分配的总带宽写入到显示端口适配器寄存器中的被保留用于对被准予的带宽的指示的寄存器中。

[0265]

示例20可以包括示例14

‑

19中的任一个的主题,进一步包括通用串行总线(usb)主机设备,该通用串行总线(usb)主机设备包括主机路由器。

[0266]

示例21可以包括示例14

‑

20中的任一个的主题,显示端口源设备用于:读取带宽分配管理模式位,以确定连接设备支持带宽分配管理;写入dpcd寄存器集合的显示端口源设备带宽管理支持字段。

[0267]

示例22可以包括示例14

‑

21中的任一个的主题,显示端口源设备用于接收与所请求的带宽相关联的中断;读取dpcd寄存器集合中的状态寄存器;基于状态寄存器的带宽请求成功字段来确定所请求的带宽被准予。

[0268]

示例23可以包括示例14

‑

22中的任一个的主题,显示端口源设备用于使用被准予的所请求的带宽来发送数据。

[0269]

示例24可以包括示例14

‑

23中的任一个的主题,其中,控制器逻辑包括操作系统。

[0270]

示例25是用于管理显示端口发送器的带宽的方法,该方法可以包括:读取指示显示端口发送器正在请求带宽分配的改变的显示端口适配器寄存器值;确定可以针对显示端口适配器准予带宽分配的改变;以及设置显示端口寄存器信息以指示所请求的带宽被准予。

[0271]

示例26可以包括示例25的主题,并且还可以包括向显示端口发送器发送中断以警告显示端口发送器已经解决了针对带宽分配的改变的请求。

[0272]

示例27可以包括示例25

‑

26中的任一个的主题,并且还可以包括在显示端口发送器处接收来自操作系统的请求带宽的改变的指示。显示端口发送器可以将改变带宽的请求写入到显示端口配置数据(dpcd)寄存器中。dpcd寄存器由显示端口适配器寄存器进行镜像。显示端口适配器可以读取显示端口适配器寄存器中的对应的字段,该字段指示显示端口发送器正在请求带宽的改变。显示端口适配器然后将通知消息发送到连接管理器以改变带宽。

[0273]

示例28可以包括示例27的主题,连接管理器可以写入显示端口适配器寄存器,以指示带宽已经被改变。连接管理器可以将中断发送到显示端口发送器。

[0274]

显示端口发送器可以读取对应的寄存器字段,以读取带宽已经被改变。显示端口发送器可以使用新的被分配的带宽来发送数据。

[0275]

在示例中,一种装置包括usb连接管理器,其用于接收(例如,通过读取dp_in适配器寄存器)来自显示端口驱动程序的请求以改变针对显示端口的带宽分配。连接管理器可以确定是否准予针对带宽分配的改变的请求。连接管理器然后可以将对带宽分配的改变的确认连同用于显示端口的新带宽写入到dp_in适配器寄存器。连接管理器可以然后将中断发送到显示端口驱动程序。带宽分配值和指示已经准予所请求的带宽的成功位也可以被写入到dp_in适配器寄存器中。

[0276]

被分配(或被准予)的带宽和成功位由dpcd寄存器进行镜像。在接收到来自连接管理器的中断之后,显示驱动程序可以检查dpcd寄存器以查看请求是否成功,并且可以检查被分配的带宽。

[0277]

在另一个示例中,连接管理器可以将估计的带宽值设置到dp_in适配器寄存器中。显示端口驱动程序可以将估计的带宽报告给操作系统。操作系统可以确定估计的带宽过高或过低,并且请求改变用于显示端口的带宽。显示端口驱动程序可以在dpcd寄存器中写入带宽更新。连接管理器可以将该带宽更新读取为来自显示端口驱动程序的用于改变针对显示端口的被分配的带宽的请求。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。