1.本发明涉及一种信号延迟技术,尤其涉及一种适用于延迟锁定回路(delay

‑

locked loop,dll)电路的延迟控制电路(latency control circuit)及方法。

背景技术:

2.在一般的计算机系统中,在内存装置外部的信号时序和装置操作是受系统时钟的控制,而在内存装置内部的信号时序和装置操作是受内部时钟的控制。为了确保在内存装置与外部装置之间传输的信号的完整性,需要使内部时钟与系统时钟能够同步。通常,在同步动态随机存取内存(synchronous dynamic random

‑

access memory,sdram)等内存装置中可包含延迟锁定回路(dll)电路来基于系统时钟提供用于读取操作以及晶粒上终端(on

‑

die termination,odt)操作的内部时钟,以解决时钟信号不同步的问题。

3.然而,在现有技术中,dll电路在读取操作以及odt操作的期间是动作的,并且在断电模式以外的大部分待机状态下也处于动作状态,以调整信号的同步。随着内存装置的速度提升,将造成dll电路的功耗大幅增加,从而对使用效率造成影响。

技术实现要素:

4.本发明提供一种延迟控制电路及方法,可使dll电路在读取操作、odt操作、或者是断电模式以外的大部分待机状态下的一段时间处于非动作状态(inactive state),同时在这一段时间内还能够维持信号的同步,以达到降低功耗的效果。

5.本发明的延迟控制电路包括dll电路、延迟计数器电路、同步电路及延迟线电路。dll电路接收用以进入动作状态的第一时钟信号及参考时钟,由此锁定用以延迟第一时钟信号的延迟时间,并且在对延迟时间进行锁定的期间提供在使能状态下的动作信号。dll电路在延迟时间被锁定后进入非动作状态,并在非动作状态的期间提供在禁能状态下的动作信号、延迟锁定信息及回路延迟信息。同步电路接收参考时钟及操作信号,且根据参考时钟及在使能状态下的动作信号来提供第一时钟信号至dll电路。同步电路根据在禁能状态下的动作信号停止提供第一时钟信号,接着响应于操作信号的使能而同步地输出操作使能信号及第二时钟信号。延迟线电路接收延迟锁定信息、操作使能信号及第二时钟信号,并在延迟时间之后同步地输出操作延迟信号及输出时钟信号。

6.本发明的延迟控制方法包括:根据参考时钟及在使能状态下的动作信号来提供第一时钟信号至dll电路;响应于接收到第一时钟信号及参考信号来激活dll电路,以锁定用以延迟第一时钟信号的延迟时间,其中在对延迟时间进行锁定的期间,动作信号保持在使能状态下;在延迟时间被锁定后,使dll电路去激活,并且通过非激活的dll电路提供在禁能状态下的动作信号、延迟锁定信息以及回路延迟信息;根据在禁能状态下的动作信号停止提供第一时钟信号,接着响应于操作信号的使能而同步输出操作使能信号以及第二时钟信号;以及,通过延迟线电路接收延迟锁定信息、操作使能信号及第二时钟信号,并且根据延迟锁定信息而在延迟时间之后同步地输出操作延迟信号以及输出时钟信号。

7.基于上述,本发明的延迟控制电路及方法能够使dll电路在将信号的延迟时间进行锁定后进入非动作状态。同时,利用dll电路以外的延迟线电路以所锁定的延迟时间对信号进行延迟。由此,能够在执行读取操作以及odt操作时使dll电路处于非动作状态,以达到降低功耗的效果。

附图说明

8.图1是依照本发明一实施例的延迟控制电路的电路示意图;

9.图2a是依照本发明一实施例的dll电路的电路示意图;

10.图2b是依照本发明一实施例的延迟锁定控制电路的电路示意图;

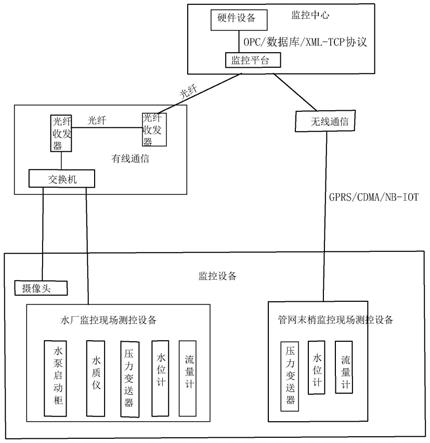

11.图2c是依照本发明一实施例的延迟计数器电路的电路示意图;

12.图2d是依照本发明一实施例的同步电路的电路示意图;

13.图3是依照本发明一实施例的延迟锁定的信号波形示意图;

14.图4是依照本发明一实施例的读取操作的信号波形示意图;

15.图5是依照本发明一实施例的odt操作的信号波形示意图;

16.图6是依照本发明一实施例的延迟锁定与更新的信号波形示意图;

17.图7是依照本发明一实施例说明延迟控制方法的流程图。

具体实施方式

18.于本发明的附图和描述中,相同元件符号用来表示相同或相似部分,因而针对相同元件符号,可能省略重复的详细说明。

19.请参照图1,本发明的一实施例的延迟控制电路100包括dll电路110、延迟计数器电路120、同步电路130以及延迟线电路140。延迟控制电路100例如内建在sdram等同步半导体内存中,以根据电路配置与操作方式对信号进行所需的延迟与同步。

20.同步电路130耦接dll电路110、延迟计数器电路120以及延迟线电路140。同步电路130接收由延迟计数器电路120所提供的操作信号(读取操作信号srd或odt操作信号sodt)以及参考时钟rclk。参考时钟rclk例如是用于内存装置内部的时钟信号,可由时钟产生电路150根据所接收到的系统时钟ck_t来提供。为了执行dll锁定操作,同步电路130可响应于参考时钟rclk以及由dll电路110所提供的在使能状态下(例如,处于高逻辑电平)的动作信号en,将第一时钟信号dclk提供至dll电路110。在dll锁定操作完成之后,由dll电路110所提供的动作信号en被改变成禁能状态(例如,动作信号en被下拉至低逻辑电平),使得同步电路130可以根据在禁能状态下的动作信号en停止提供第一时钟信号dclk,从而让dll电路110进入非动作状态。

21.在dll锁定操作的期间,由dll电路110决定用于延迟第一时钟信号dclk的延迟时间,接着将延迟锁定信息sel以及回路延迟信息cnt_lp储存在dll电路110中。在dll锁定操作完成之后,将dll电路110中所储存的延迟锁定信息sel以及回路延迟信息cnt_lp分别提供至延迟线电路140以及延迟计数器电路120。因此,用于延迟同步电路130的输出的延迟时间会根据延迟锁定信息sel而被决定。

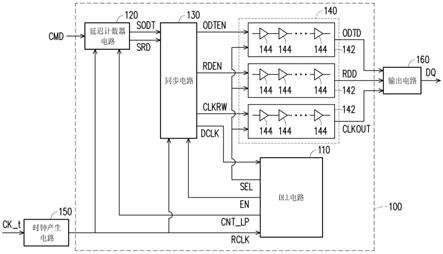

22.举例来说,如图2a所示,本发明的一实施例的dll电路110包括延迟时间决定电路210、复制电路220、比较电路230以及延迟锁定控制电路240。

23.延迟时间决定电路210例如包括多个延迟单元212。延迟单元212可以相互串接或者以任意方式连接,并且每一个延迟单元212可以是一个正向延迟组件或一个反向(inverse)延迟组件。

24.延迟时间决定电路210可接收第一时钟信号dclk及延迟锁定信息sel,并且在由多个延迟单元212所产生的延迟时间之后输出延迟时钟信号oclk。具体来说,延迟时间决定电路210接收第一时钟信号dclk与延迟时间决定电路210输出延迟时钟信号oclk之间的时间间隔,等于根据延迟锁定信息sel所选择的延迟单元212所构成的延迟线所决定的延迟时间。因此,延迟时间决定电路210可根据延迟锁定信息sel来调整所具有的延迟级数(也就是所选择的延迟单元212的级数),以决定延迟时间。

25.复制电路220耦接延迟时间决定电路210。复制电路220接收延迟时钟信号oclk,以提供反馈时钟信号fclk,由此可补偿由延迟控制电路100的输出端所造成的延迟。在一实施例中,复制电路220是耦接延迟线电路140的输出的输出电路160的复制结构。

26.比较电路230耦接复制电路220。比较电路230接收参考时钟rclk,并且比较参考时钟rclk与反馈时钟信号fclk的相位差,并且将比较结果up_dn提供到延迟锁定控制电路240。在一实施例中,当反馈时钟信号fclk的上升缘在参考时钟rclk的上升缘之前时,比较结果up_dn处于高逻辑电平以增加其后的延迟时间,当反馈时钟信号fclk的上升缘在参考时钟rclk的上升缘之后时,比较结果up_dn处于低逻辑电平以减小其后的延迟时间。因此,基于比较结果up_dn,通过由延迟锁定控制电路240所更新的延迟锁定信息sel,反馈时钟信号fclk的相位可以向前或向后移位以与参考时钟rclk的相位相对应。此外,比较电路230还将与参考时钟rclk具有相同相位的延迟参考时钟rclk_1以及与反馈时钟信号fclk具有相同相位的延迟反馈时钟信号fclk_1提供至延迟锁定控制电路240。

27.延迟锁定控制电路240耦接延迟时间决定电路210以及比较电路230。延迟锁定控制电路240可根据延迟参考时钟rclk_1、延迟反馈时钟信号fclk_1以及比较结果up_dn来输出延迟锁定信息sel以及回路延迟信息cnt_lp。具体来说,延迟锁定控制电路240可根据比较结果up_dn传送延迟锁定信息sel至延迟时间决定电路210,以调整用于延迟第一时钟信号dclk的延迟时间。接着,延迟锁定控制电路240可通过将相应的延迟锁定信息sel锁存到延迟锁定控制电路240中,来锁定调整后的延迟时间(即固定住延迟时间),并且可将对应的延迟锁定信息sel以及回路延迟信息cnt_lp分别输出至延迟线电路140以及延迟锁定控制电路240。回路延迟信息cnt_lp用以指出由dll锁定操作所提供的回路延迟的周期数量。在一实施例中,在dll锁定操作完毕之前,回路延迟信息cnt_lp是等于“0000”的四位数字;在dll锁定操作完毕之后,回路延迟信息cnt_lp适当地变为与“0000”不同的另一值。

28.如图2b所示,本发明的一实施例的延迟锁定控制电路240包括延迟选择电路242、回路延迟控制电路244以及回路延迟计数器246。延迟选择电路242接收延迟参考时钟rclk_1以及比较结果up_dn以执行dll锁定演算。延迟选择电路242可根据比较结果up_dn提供延迟锁定信息sel至延迟时间决定电路210。在dll锁定演算完成之后,延迟选择电路242可在内部产生用于指示dll锁定操作完毕的处于高逻辑电平的锁定信号lock

‑

in。另一方面,当正在进行dll锁定操作时,锁定信号lock

‑

in是处于低逻辑电平。

29.回路延迟控制电路244耦接延迟选择电路242。在接收到锁定信号lock

‑

in之后,回路延迟控制电路244将动作信号en改变成禁能状态,并输出在禁能状态下的动作信号en至

同步电路130,以通过停止提供第一时钟信号dclk来使dll电路110进入非动作状态,并且延迟反馈时钟信号fclk_1会被相应地中断。回路延迟控制电路244也接收延迟参考时钟rclk_1,接着传送延迟参考时钟rclk_1至回路延迟计数器246。

30.回路延迟计数器246耦接回路延迟控制电路244,并且根据延迟反馈时钟信号fclk_1以及延迟参考时钟rclk_1产生回路延迟信息cnt_lp。具体来说,回路延迟计数器246可响应于延迟参考时钟rclk_1来计数从接收延迟反馈时钟信号fclk_1直到延迟反馈时钟信号fclk_1中断为止的时钟计数值,据以产生回路延迟信息cnt_lp。

31.如图1所示,延迟计数器电路120耦接dll电路110以及同步电路130。延迟计数器电路120可根据操作命令cmd、参考时钟rclk以及回路延迟信息cnt_lp延迟操作信号的使能。其中,操作命令cmd例如是由命令译码电路所提供,可通知sdram进行读取操作或odt操作。并且,操作命令cmd包括附加延迟信息,例如附加延迟al、列地址选通(column address strobe,cas)脉冲延迟cl以及cas写入延迟cwl等。此外,延迟时间决定电路210可根据从附加延迟信息减去回路延迟信息cnt_lp的计算结果来控制延迟计数器电路120延迟使能操作信号。在本发明实施例中,操作信号可包括读取操作信号srd或odt操作信号sodt。

32.如图2c所示,本发明一实施例的延迟计数器电路120包括译码器122、命令控制电路124及移位寄存器126。译码器122、命令控制电路124及移位寄存器126接收参考时钟rclk以进行操作。译码器122对回路延迟信息cnt_lp及cas脉冲延迟cl或cas写入延迟cwl进行译码,以传送译码结果dr(例如表示cl

‑

cnt_lp或cwl

‑

cnt_lp的时间期间)至移位寄存器126。

33.操作命令cmd还包括丛发信息b以及命令信号read、write及pin odt。命令控制电路124根据附加延迟al以及丛发信息b,对命令信号read、write及pin odt进行操作,以产生命令脉冲(其用于命令信号read)或者第一命令脉冲与最后命令脉冲的组合(其用于命令信号write或pin odt)。当命令控制电路124接收到命令信号read时,命令控制电路124可以决定针对命令信号read的命令脉冲的脉冲宽度。当命令控制电路124接收到命令信号write或pin odt时,命令控制电路124可以决定针对命令信号write或pin odt的第一脉冲与最后脉冲的时序。接着,命令控制电路124根据命令信号read、write或pin odt将对应的命令控制信号cctl传送至移位寄存器126。

34.移位寄存器126耦接译码器122以及命令控制电路124。移位寄存器126可根据解码结果dr及命令控制信号cctl,而在延迟al cl

‑

cnt_lp

‑

b或al cwl

‑

cnt_lp

‑

b所定义的时间期间之后,使能odt操作信号sodt或读取操作信号srd。

35.此外,同步电路130可响应于操作信号的使能而同步输出操作使能信号及第二时钟信号clkrw。在本发明实施例中,操作使能信号可包括读取操作使能信号rden或odt操作使能信号odten。具体来说,同步电路130可响应于读取操作信号srd的使能而同步输出读取操作使能信号rden及第二时钟信号clkrw,或者响应于odt操作信号sodt的使能而同步输出odt操作使能信号odten及第二时钟信号clkrw。

36.如图2d所示,本发明一实施例的同步电路130包括同步控制电路131、延迟控制电路132及多个控制单元133~136。同步控制电路131接收读取操作信号srd或odt操作信号sodt,并且将参考时钟rclk与读取操作信号srd或odt操作信号sodt结合,以产生子读取操作信号srd_1或子odt操作信号sodt_1。子读取操作信号srd_1被传送至控制单元134。子odt操作信号sodt_1被传送至控制单元133。此外,在接收到读取操作信号srd或odt操作信号

sodt的期间,同步控制电路131输出子参考时钟rclk_2至控制单元135。延迟控制电路132可包括延迟单元,其用于延迟参考时钟rclk以将控制信号cs传送至控制单元133~136,从而确保有足够的时间来产生子读取操作信号srd_1、子odt操作信号sodt_1及子参考时钟rclk_2。

37.控制单元133~136耦接同步控制电路131以及延迟控制电路122。每个控制单元133~136可包括以锁存结构或正反器结构实现的时钟闸控电路。控制单元133~136分别根据控制信号cs来控制时钟闸控电路,以控制读取操作使能信号rden、odt操作使能信号odten、第二时钟信号clkrw及第一时钟信号dclk之间的相关时序。

38.延迟线电路140耦接dll电路110以及同步电路130。据此,延迟线电路140可接收延迟锁定信息sel、操作使能信号(读取操作使能信号rden或odt操作使能信号odten)以及第二时钟信号clkrw,并且在由dll电路110锁定的延迟时间之后,延迟线电路140可同步输出操作延迟信号以及输出时钟信号clkout。在本发明实施例中,操作延迟信号可包括读取操作延迟信号rdd或odt操作延迟信号odtd。

39.具体来说,延迟线电路140例如包括多个延迟时间决定电路复制结构142。每个延迟时间决定电路复制结构142由延迟单元144所构成,且是延迟时间决定电路210的复制结构。如图1所示,在本发明实施例的延迟线电路140中,第一个延迟时间决定电路复制结构142用以延迟odt操作使能信号odten,第二个延迟时间决定电路复制结构142用以延迟读取操作使能信号rden,并且第三个延迟时间决定电路复制结构142用以延迟第二时钟信号clkrw。三个延迟时间决定电路复制结构142在同步电路130与输出电路160之间并联连接。

40.观察图1以及图2a可知,本发明实施例的延迟线电路140以及延迟时间决定电路210是使用同一个延迟锁定信息sel来调整延迟线所具有的延迟级数。因此,延迟线电路140可根据延迟锁定信息sel来调整各延迟时间决定电路复制结构142上延迟单元144的所选级数,以使其由延迟线电路140所产生的延迟时间完全相等于dll电路110所锁定的延迟时间。

41.基于本发明的电路配置,在本发明实施例的延迟控制电路100中,dll电路110可在用以延迟第一时钟信号dclk的延迟时间被锁定后进入非动作状态。并且,在dll电路110处于非动作状态的期间,延迟线电路140可根据相同的延迟锁定信息sel,使操作使能信号(读取操作使能信号rden或odt操作使能信号odten)以及第二时钟信号clkrw的延迟时间等于dll电路110所锁定的延迟时间,以输出操作延迟信号(读取操作延迟信号rdd或odt操作延迟信号odtd)及输出时钟信号clkout,从而控制输出电路160对数据dq进行输出。由此,可使dll电路110可在读取操作、odt操作、或者是断电模式以外的大部分待机状态下的一段时间内处于非动作状态,以降低功耗。

42.以下对本发明实施例中延迟控制电路100进行延迟锁定的方式进行说明,请同时参照图1、图2a及图3。在图3中,在时间点t31时,dll电路110接收到重置命令drst,并且开始对延迟线进行调整,以重新锁定用以延迟第一时钟信号dclk的延迟时间。当dll电路110决定了延迟时间时(即时间点t32),dll电路110可锁定延迟时间,并且据以分别提供延迟锁定信息sel及回路延迟信息cnt_lp至延迟线电路140及延迟计数器电路120。接着,在时间点t33时,dll电路110的延迟锁定控制电路240禁能动作信号en,例如将动作信号en拉低至低逻辑电平,使得同步电路130可根据动作信号en的禁能而停止提供第一时钟信号dclk(或者将第一时钟信号dclk固定在低逻辑电平),以使dll电路110进入非动作状态。其中,重置命

令drst可例如在内存装置启动时、进行模式缓存器设定(mrs)时、退出idd6、idd8模式时或者是其他任何重置脚位被触发时产生。

43.在dll操作完成之后,本发明实施例的dll电路110会处于非动作状态,因此在进行读取操作时,第一时钟信号dclk及动作信号en将保持在表示为禁能的低逻辑电平。以下对本发明实施例中延迟控制电路100进行读取操作的方式进行说明,请同时参照图1、图2a及图4。

44.在图4中,将读取操作分为8位以及16位来举例进行说明。在时间点t41时,延迟计数器电路120接到的操作命令cmd是要进行读取操作的读取命令rd。延迟计数器电路120可根据读取命令rd以及回路延迟信息cnt_lp,在延迟一段时间ts1后才使能读取操作信号srd。读取操作信号srd在参考时钟rclk的下降缘被激活。时间ts1例如为al cl

‑

cnt_lp

‑

ac。其中,ac为用于匹配电路设计的参考时钟rclk的任意周期数。

45.当延迟计数器电路120使能读取操作信号srd时(即时间点t42),同步电路130可响应于读取操作信号srd的使能,而接着在时间点t43同步地输出读取操作使能信号rden及第二时钟信号clkrw。在本发明实施例中,被激活的读取操作信号srd以及被激活的读取操作使能信号rden例如是在特定时间期间内保持在高逻辑电平的静态信号。

46.当进行8位的读取操作时,延迟计数器电路120可在时间点t44禁能读取操作信号srd。同步电路130可响应于读取操作信号srd的禁能而在时间点t45停止输出读取操作使能信号rden以及第二时钟信号clkrw。

47.当进行16位的读取操作时,延迟计数器电路120可在时间点t46禁能读取操作信号srd。同步电路130可响应于读取操作信号srd的禁能而在时间点t47停止输出读取操作使能信号rden以及第二时钟信号clkrw。

48.类似地,在dll操作完成之后,当进行odt操作时,本发明实施例的dll电路110会处于非动作状态,因此第一时钟信号dclk以及动作信号en保持在表示为禁能的低逻辑电平。以下对本发明实施例中延迟控制电路100进行odt操作的方式进行说明,请同时参照图1、图2a及图5。

49.在图5中,也将odt操作分为8位以及16位来举例进行说明。在时间点t51时,延迟计数器电路120接到的操作命令cmd是要进行写入或odt操作的命令odt。延迟计数器电路120可根据命令odt及回路延迟信息cnt_lp,在延迟一段时间ts2后才使能odt操作信号sodt。odt操作信号sodt在参考时钟rclk的下降缘被激活。时间ts2例如为al cwl

‑

cnt_lp

‑

ac。

50.当延迟计数器电路120使能odt操作信号sodt时(即时间点t52),同步电路130可响应于odt操作信号sodt的使能,而接着在时间点t53同步输出odt操作使能信号odten及第二时钟信号clkrw。在本发明实施例中,被激活的odt操作信号sodt以及odt操作使能信号odten分别例如为脉冲信号。

51.当进行8位的odt操作时,延迟计数器电路120可在时间点t54再度使能odt操作信号sodt。同步电路130可响应于odt操作信号sodt的使能,而接着在时间点t55同步地输出odt操作使能信号odten及第二时钟信号clkrw。

52.当进行16位的odt操作时,延迟计数器电路120可在时间点t56再度使能odt操作信号sodt。同步电路130可响应于odt操作信号sodt的使能,而接着在时间点t57同步地输出odt操作使能信号odten及第二时钟信号clkrw。

53.以下对本发明实施例中延迟控制电路100进行延迟锁定与更新的方式进行说明,请同时参照图1、图2a及图6。

54.在图6中,在时间点t61时,dll电路110接到重置命令drst,并且开始对延迟线进行调整,以重新锁定用以延迟第一时钟信号dclk的延迟时间。当dll电路110决定了延迟时间时(即时间点t62),dll电路110可锁定延迟时间,并且据以提供延迟锁定信息sel以及回路延迟信息cnt_lp。接着,在时间点t63时,dll电路110的延迟锁定控制电路240会禁能动作信号en,例如将动作信号en拉低至低逻辑电平。并且,同步电路130可根据动作信号en的禁能而停止提供第一时钟信号dclk,以使dll电路110进入非动作状态。

55.在时间点t63之后,当dll电路110在特定时间期间ts3之后接收到命令(例如,自动刷新命令ar)时,dll电路110可在时间点t64时被触发回到动作状态,以重新锁定用以延迟第一时钟信号dclk的延迟时间,并且相应地更新延迟锁定信息sel及回路延迟信息cnt_lp。此后,dll电路110可在时间点t65再次进入非动作状态。在另一实施例中,当dll电路110进入非动作状态后,可间隔特定时间期间(例如70微秒)而在没有命令的情况下经触发回到动作状态,以定期适当地更新延迟锁定信息sel以及回路延迟信息cnt_lp。

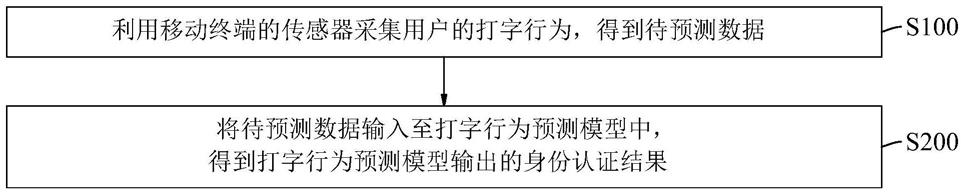

56.请参照图7,在本实施例中信号的延迟控制方法包括下列步骤。根据参考时钟以及在使能状态下的动作信号来提供第一时钟信号至dll电路(步骤s710)。在接收到第一时钟信号以及参考信号之后,激活dll电路以锁定对第一时钟信号进行延迟的延迟时间,其中在对延迟时间进行锁定的期间,动作信号保持在使能状态下(步骤s720)。在延迟时间被锁定后,dll电路被去激活以进入非动作状态,并且提供在禁能状态下的动作信号、延迟锁定信息以及回路延迟信息(步骤s730)。根据在禁能状态下的动作信号停止提供第一时钟信号,接着响应于操作信号的使能而同步输出操作使能信号以及第二时钟信号(步骤s740)。接着,通过延迟线电路接收延迟锁定信息、操作使能信号以及第二时钟信号,并且通过延迟线电路在延迟时间之后根据延迟锁定信息同步输出操作延迟信号以及输出时钟信号(步骤s750)。上述步骤s710、s720、s730、s740及s750的实施细节在前述的实施例及实施方式都有详尽的说明,在此则不再赘述。

57.综上所述,通过本发明的延迟控制装置,能够在dll电路进入非动作状态时,利用dll电路以外的延迟线电路以所锁定的延迟时间对信号进行延迟。由此,能够在执行读取操作以及odt操作时使dll电路处于非动作状态,以达到降低功耗的效果。

58.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。