防止buck电路上电穿通的高边管控制信号电位平移改进电路

技术领域

1.本发明涉及buck降压电路技术,特别是一种防止buck电路上电穿通的高边管控制信号电位平移改进电路,通过在电位平移节点va的接地控制nmos管m2栅端设置基于输入电压vin的耦合电容c1与第一电流源的并联电路和基于接地端的第一齐纳二极管d1与栅端由buck电路使能信号en所控制的第九nmos管的并联电路,能够避免电位平移节点va在vin快速上升时造成的电压浮空现象,防止buck电路上电穿通,从而有利于保护负载器件和保持输出信号的正常逻辑。

背景技术:

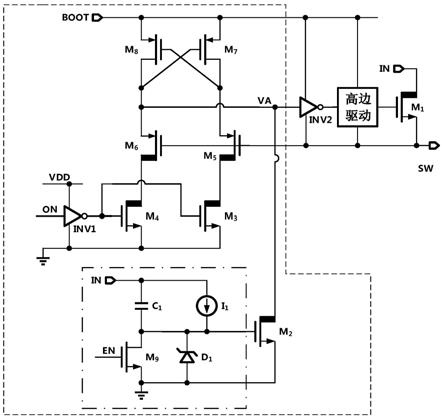

2.buck降压电路(又称buck电路,或简称为buck)在应用中有可能出现上电穿通现象。图1是现有技术中buck降压电路的外接电路结构示意图。如图1所示,buck电路输入端连接输入电压端in,buck电路地端接地,buck电路升压端boot通过外置电容cbt连接开关节点sw,buck电路输出端连接开关节点sw,开关节点sw通过电感l连接输出电压端out,输出电压端out通过输出电容cout接地。图1中所述buck降压电路为自举型buck电路,通过外置电容cbt将升压端boot的电压自举升压以驱动buck电路内部的高边nmos管的栅端,例如,将boot电压自举到比输入电压vin更高。但是,在输入电压vin上电的应用中,上电过程中的buck内部电平可能没有建立好而导致逻辑混乱,存在上电瞬间vsw会被拉升到vin或接近vin的电平,这种情况称为上电穿通。即使经过l和cout组成的lc电路会平抑,但vout仍会跟随vin上升。这导致vout在上游电源上电瞬间过高,甚至超过负载器件的耐压值,导致负载器件失效。针对上电穿通现象,需要采用高边控制信号的电位平移解决方案,如图2所示。图2是针对图1中输出电压端out在buck电路上电时可能出现上电穿通(开关节点sw电压vsw接近输入电压端in电压vin)而采用的高边nmos管m1控制信号电位平移电路结构示意图。图2中的虚框是电位平移模块,所述电位平移模块中的电位平移节点va向外连接第二反相器inv2的输入端,inv2的输出端连接高边驱动逻辑电路的输入端,所述高边驱动逻辑电路的输出端连接高边nmos管m1的栅端,m1的漏端连接输入电压端in,m1的源端连接开关节点sw,所述高边驱动逻辑电路的电源轨和inv2的电源轨均连接升压端boot,所述高边驱动逻辑电路的地轨和inv2的地轨均连接所述开关节点sw。所述电位平移节点va向内分为两路,第一路分别连接第七pmos管m7的栅端、第八pmos管m8的漏端和第六pmos管m6的源端,第二路连接接地控制nmos管m2的漏端,m2的源端接地,m2的栅端连接第三反相器inv3的输出端,inv3的输入端连接buck电路使能信号端,inv3的电源轨连接电源电压端vdd(内部电源或内部偏置电源),inv3的地轨接地。m7的源端和m8的源端均连接升压端boot,m7的漏端分别连接m8的栅端和第五pmos管m5的源端,m5的栅端和m6的栅端均连接所述开关节点sw。m5的漏端连接第三nmos管m3的漏端,m6的漏端连接第四nmos管m4的漏端,m3的源端和m4的源端均接地,m3的栅端和m4的栅端均连接第一反相器inv1的输出端,inv1的电源轨连接电源电压端vdd,inv1的地轨接地,inv1的输入端连接高边控制信号on。如图2示,在输入电压vin快速上升时,boot端和sw端电压不确定,而内部电源vdd不能及时跟随vin上升导致m2处于关断状态,这

些都是造成va节点电压浮空的原因。当sw端被vin电压耦合上升后,因外置电容缘故boot也会跟随上升。va节点寄生电容比m7漏端更多,所以更容易跟随boot上升,因此m7和m8组成的电路很容易锁住这个状态,即va节点电压为高,m7漏端电压为低。va节点为高表示要开启高边nmos管m1,此信号经反相器inv2送到高边驱动模块(其电源轨接boot电压,地轨接sw电压)。此时当被耦合上升的boot电压一旦超过m1的栅源电压后将开启m1,如此便将in端与sw端连接,并加速了sw和boot上升,最终导致in端与sw穿通。本发明人认为,如果将电位平移节点va向内分为两路中的第二路接地控制nmos管m2栅端设置基于输入电压vin的耦合电容与第一电流源的并联电路和基于接地端的第一齐纳二极管d1与栅端由buck电路使能信号en所控制的第九nmos管的并联电路,则能够避免电位平移节点va在vin快速上升时造成的电压浮空现象,防止buck电路上电穿通,从而有利于保护负载器件和保持输出信号的正常逻辑。有鉴于此,本发明人完成了本发明。

技术实现要素:

3.本发明针对现有技术中存在的缺陷或不足,提供一种防止buck电路上电穿通的高边管控制信号电位平移改进电路,通过在电位平移节点va的接地控制nmos管m2栅端设置基于输入电压vin的耦合电容c1与第一电流源i1的并联电路和基于接地端的第一齐纳二极管d1与栅端由buck电路使能信号en所控制的第九nmos管的并联电路,能够避免电位平移节点va在vin快速上升时造成的电压浮空现象,防止buck电路上电穿通,从而有利于保护负载器件和保持输出信号的正常逻辑。

4.本发明的技术方案如下:

5.防止buck电路上电穿通的高边管控制信号电位平移改进电路,其特征在于,包括在电位平移节点va的接地控制nmos管m2栅端设置基于输入电压vin的耦合电容c1与第一电流源i1的第一并联电路和基于接地端的第一齐纳二极管d1与栅端由buck电路使能信号en所控制的第九nmos管m9的第二并联电路。

6.所述第一并联电路中的所述第一电流源i1的出端连接所述接地控制nmos管m2的栅端,所述第一电流源i1的入端连接输入电压端in,所述耦合电容c1的一端连接所述输入电压端in,另一端连接所述接地控制nmos管m2的栅端,所述接地控制nmos管m2的漏端连接所述电位平移节点va,所述接地控制nmos管m2的源端接地。

7.所述第二并联电路中的所述第一齐纳二极管d1的负端和所述第九nmos管的漏端均连接所述接地控制nmos管m2的栅端,所述接地控制nmos管m2的源端和所述第一齐纳二极管d1的正端均接地,所述接地控制nmos管m2的漏端连接所述电位平移节点va,所述接地控制nmos管m2的源端接地。

8.电位平移节点va向外连接第二反相器inv2的输入端,所述第二反相器inv2的输出端连接高边驱动逻辑电路的输入端,所述高边驱动逻辑电路的输出端连接高边nmos管m1的栅端,所述高边nmos管m1的漏端连接输入电压端in,所述高边nmos管m1的源端连接开关节点sw,所述高边驱动逻辑电路的电源轨和所述第二反相器inv2的电源轨均连接升压端boot,所述高边驱动逻辑电路的地轨和所述第二反相器inv2的地轨均连接所述开关节点sw。

9.电位平移节点va向内分别连接第七pmos管m7的栅端、第八pmos管m8的漏端和第六

电感;cout-输出电容;m1-第一nmos管或高边nmos管;m2-第二nmos管或接地控制nmos管;m3~m4-第三至第四nmos管;m5~m8-第五至第八pmos管;m9-第九nmos管;inv1~inv3-第一至第三反相器;

具体实施方式

21.下面结合附图(图3)对本发明进行说明。

22.图3是实施本发明防止buck电路上电穿通的高边管控制信号电位平移改进电路结构示意图。如图3所示,防止buck电路上电穿通的高边管控制信号电位平移改进电路,其特征在于,包括在电位平移节点va的接地控制nmos管m2栅端设置基于输入电压vin的耦合电容c1与第一电流源i1的第一并联电路和基于接地端的第一齐纳二极管d1与栅端由buck电路使能信号en所控制的第九nmos管m9的第二并联电路。所述第一并联电路中的所述第一电流源i1的出端连接所述接地控制nmos管m2的栅端,所述第一电流源i1的入端连接输入电压端in,所述耦合电容c1的一端连接所述输入电压端in,另一端连接所述接地控制nmos管m2的栅端,所述接地控制nmos管m2的漏端连接所述电位平移节点va,所述接地控制nmos管m2的源端接地。所述第二并联电路中的所述第一齐纳二极管d1的负端和所述第九nmos管的漏端均连接所述接地控制nmos管m2的栅端,所述接地控制nmos管m2的源端和所述第一齐纳二极管d1的正端均接地,所述接地控制nmos管m2的漏端连接所述电位平移节点va,所述接地控制nmos管m2的源端接地。

23.电位平移节点va向外连接第二反相器inv2的输入端,所述第二反相器inv2的输出端连接高边驱动逻辑电路的输入端,所述高边驱动逻辑电路的输出端连接高边nmos管m1的栅端,所述高边nmos管m1的漏端连接输入电压端in,所述高边nmos管m1的源端连接开关节点sw,所述高边驱动逻辑电路的电源轨和所述第二反相器inv2的电源轨均连接升压端boot,所述高边驱动逻辑电路的地轨和所述第二反相器inv2的地轨均连接所述开关节点sw。电位平移节点va向内分别连接第七pmos管m7的栅端、第八pmos管m8的漏端和第六pmos管m6的源端,第七pmos管m7的源端和第八pmos管m8的源端均连接升压端boot,第七pmos管m7的漏端分别连接第八pmos管m8的栅端和第五pmos管m5的源端,第五pmos管m5的栅端和第六pmos管m6的栅端均连接开关节点sw。第五pmos管m5的漏端连接第三nmos管m3的漏端,第六pmos管m6的漏端连接第四nmos管m4的漏端,第三nmos管m3的源端和第四nmos管m4的源端均接地,第三nmos管m3的栅端和第四nmos管m4的栅端均连接第一反相器inv1的输出端,第一反相器inv1的电源轨连接电源电压端vdd,第一反相器inv1的地轨接地,第一反相器inv1的输入端连接高边控制信号on。所述高边控制信号on在其逻辑高时,高边nmos管m1开启,所述高边控制信号on在其逻辑低时,高边nmos管m1断开。所述buck电路使能信号en在其逻辑高时,buck电路使能,所述buck电路使能信号en在其逻辑低时,buck电路关断。

24.所述耦合电容c1利用第九nmos管m9上电期间断开时的等效阻抗直接将输入电压vin耦合至所述接地控制nmos管m2的栅端,使所述接地控制nmos管m2导通,所述电位平移节点va的电压被拉至地。所述第一齐纳二极管d1反向稳压阈值不大于6v,能够保护所述接地控制nmos管m2的栅源电压以防止其被上升的耦合电压击穿。

25.参考图3所示,对本发明的具体工作原理做出如下进一步说明。

26.1.m1为大尺寸高边高压nmos,其栅端接高边驱动输出,其漏端接in端,其源端接sw

端。2.m3和m4为高压nmos,其连接如图3所示,受反相器inv1的输出信号控制。3.on信号为高边控制信号,其逻辑高表示开启高边mos管,其逻辑低代表断开高边mos。4.反相器inv1的电源轨接vdd(内部偏置电源),地轨仍接地。5.m5和m6为高压pmos,二者栅端均连接sw端,其它连接如图3所示。

27.6.m7和m8为pmos,二者源端均接boot端,其它连接如图3所示。7.m3、m4、m5、m6、m7和m8实现电位平移功能,m6的源端、m7的栅端和m8的漏端均接va。8.m2是高压nmos,其漏端接va,其它连接如图3所示。9.d1为齐纳二极管,其反向稳压阈值一般小于6v,而负端接m2的栅端。10.i1为电流源,其正端接in端,而负端接m2的栅端,在电源上电(vin从0快速上升)时它往往不能及时产生电流。

28.11.c1为电容,一端接in端,另一端接m2的栅端。12.m9为nmos管,其漏端接m2栅端,其栅端接en信号。13.en为逻辑高时代表buck使能,反之关断buck。14.电源上电时,因为内部偏置vdd从0v起来所以en此时为0,所以m9关闭,而m2栅极通过电容c1被耦合到vin(in端电压),所以m2开启,同时由于d1的存在所以m2的栅源电压不会超过齐纳二极管的反向稳压阈值,这就保证了m2栅端不会随vin上升而超过自身击穿电压。15.通过14描述,发现电源上电时m2被vin耦合到高电平,所以m2是导通的。

29.16.因为电源上电时m2导通,所以va在此过程中是存在明确低电平。17.高边驱动是由逻辑电路组成,在in端上电过程中即使m1栅端被其耦合超过1v,通过高边驱动模块内部逻辑的pmos寄生二极管就会传递到boot端,进而开启整个高边驱动模块,但因va是低电平,所以m1仍然不会开启。18.当内部偏置电压vdd建立好后,电流源i1也建立好,因此正常工作时c1、i1、d1、m9和m2完全由en信号控制,即en为逻辑高时(代表buck使能)m2处于关断状态且不干涉va电压,而en为逻辑低时(代表buck关断)m2处于导通状态,将va电压拉至地。

30.在此指明,以上叙述有助于本领域技术人员理解本发明创造,但并非限制本发明创造的保护范围。任何没有脱离本发明创造实质内容的对以上叙述的等同替换、修饰改进和/或删繁从简而进行的实施,均落入本发明创造的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。