1.本发明属于数据计算技术领域,特别是涉及一种基于光子神经网络芯片的智能信号处理系统。

背景技术:

2.利用光子学超高带宽优势,能够对现有的信号处理速度进行数个数量级的提升。在2017年,麻省理工学院的研究人员提出了一种典型的光子神经网络芯片,此芯片利用光学酉阵变换实现了全光任意矩阵相乘计算,为全连接神经网络的计算加速提供了一种光子学的解决思路。然而,其全光架构依赖于超大规模的光子集成技术,在现有的技术水平下,一个理想智能功能的神经网络很难用全光的方法在光子芯片中实现。若适当利用电子学技术的存储优势和任意数据处理优势将避免全光架构的实现困难性。为光子神经网络芯片的发展提供一条现实的发展道路。

技术实现要素:

3.本发明主要解决的技术问题是提供一种基于光子神经网络芯片的智能信号处理系统,利用光子神经网络芯片大幅加速神经网络计算速度,相较传统电子芯片的计算速度提升数个数量级;同时,该系统结合电子技术的存储功能和任意信号处理功能,避免了光路中无法存储和无法优质处理信号的劣势。

4.为解决上述技术问题,本发明采用的一个技术方案是:一种基于光子神经网络芯片的智能信号处理系统,包括光芯片和光子神经网络芯片;

5.待计算的数据通过所述光芯片发送至所述光子神经网络芯片;所述光子神经网络芯片对所述待计算的数据进行卷积层计算,生成中间数据,并发送所述中间数据至所述光芯片;所述光芯片对所述中间数据进行卷积层计算,生成目标数据。

6.进一步地说,所述光芯片将所述目标数据以及下一计算周期输入的待计算的数据发送至所述光子神经网络芯片,以使所述光子神经网络芯片对所述目标数据以及所述下一计算周期输入的待计算的数据进行卷积层计算。

7.进一步地说,对所述光子神经网络芯片进行训练,所述训练包括:

8.基于所述待计算的数据,确定出所述光子神经网络芯片的网络运算架构;

9.基于所述网络运算架构,确定出待求解的目标相位参数;

10.基于所述目标相位参数以及斐索干涉仪的预设参数值,确定出所述斐索干涉仪的目标参数值。

11.进一步地说,基于所述网络运算架构,确定出待求解的目标相位参数,包括:

12.基于所述网络运算架构,确定出三维矩阵和二维矩阵;

13.基于所述三维矩阵以及所述二维矩阵,确定出所述待求解的目标相位参数。

14.进一步地说,所述光芯片包括fpga、arm、dsp、cpu、gpu中的任意一个。

15.进一步地说,所述光子神经网络芯片包括控制单元、i/o接口、缓冲单元以及运算

单元;

16.所述i/o接口用于接收输入所述光子神经网络芯片的输入信号,并将所述输入信号发送至所述缓冲单元以及所述运算单元;

17.所述运算单元用于接收所述输入信号,并对所述输入信号进行计算,生成输出信号;

18.所述缓冲单元用于存储所述输入信号以及所述输出信号;

19.所述控制单元用于基于芯片控制指令,执行与所述芯片控制指令相对应的执行动作。

20.本发明的有益效果:利用光子神经网络芯片大幅加速神经网络计算速度,相较传统电子芯片的计算速度提升数个数量级;同时,该系统结合电子技术的存储功能和任意信号处理功能,避免了光路中无法存储和无法优质处理信号的劣势。

附图说明

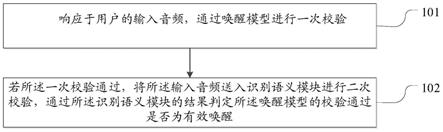

21.图1是本发明的系统处理流程示意图。

具体实施方式

22.下面结合附图对本发明的较佳实施例进行详细阐述,以使本发明的优点和特征能更易于被本领域技术人员理解,从而对本发明的保护范围做出更为清楚明确的界定。

23.实施例:一种基于光子神经网络芯片的智能信号处理系统,如图1所示,包括光芯片和光子神经网络芯片;

24.待计算的数据通过所述光芯片发送至所述光子神经网络芯片;所述光子神经网络芯片对所述待计算的数据进行卷积层计算,生成中间数据,并发送所述中间数据至所述光芯片;所述光芯片对所述中间数据进行卷积层计算,生成目标数据。

25.所述光芯片将所述目标数据以及下一计算周期输入的待计算的数据发送至所述光子神经网络芯片,以使所述光子神经网络芯片对所述目标数据以及所述下一计算周期输入的待计算的数据进行卷积层计算。

26.对所述光子神经网络芯片进行训练,所述训练包括:

27.基于所述待计算的数据,确定出所述光子神经网络芯片的网络运算架构;

28.基于所述网络运算架构,确定出待求解的目标相位参数;

29.基于所述目标相位参数以及斐索干涉仪的预设参数值,确定出所述斐索干涉仪的目标参数值。

30.基于所述网络运算架构,确定出待求解的目标相位参数,包括:

31.基于所述网络运算架构,确定出三维矩阵和二维矩阵;

32.基于所述三维矩阵以及所述二维矩阵,确定出所述待求解的目标相位参数。

33.所述光芯片包括fpga、arm、dsp、cpu、gpu中的任意一个。

34.所述光子神经网络芯片包括控制单元、i/o接口、缓冲单元以及运算单元;

35.所述i/o接口用于接收输入所述光子神经网络芯片的输入信号,并将所述输入信号发送至所述缓冲单元以及所述运算单元;

36.所述运算单元用于接收所述输入信号,并对所述输入信号进行计算,生成输出信

号;

37.所述缓冲单元用于存储所述输入信号以及所述输出信号;

38.所述控制单元用于基于芯片控制指令,执行与所述芯片控制指令相对应的执行动作。

39.本发明的工作原理如下:

40.利用光子神经网络芯片大幅加速神经网络计算速度,相较传统电子芯片的计算速度提升数个数量级;同时,该系统结合电子技术的存储功能和任意信号处理功能,避免了光路中无法存储和无法优质处理信号的劣势。

41.以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

技术特征:

1.一种基于光子神经网络芯片的智能信号处理系统,其特征在于:包括光芯片和光子神经网络芯片;待计算的数据通过所述光芯片发送至所述光子神经网络芯片;所述光子神经网络芯片对所述待计算的数据进行卷积层计算,生成中间数据,并发送所述中间数据至所述光芯片;所述光芯片对所述中间数据进行卷积层计算,生成目标数据。2.根据权利要求1所述的基于光子神经网络芯片的智能信号处理系统,其特征在于:所述光芯片将所述目标数据以及下一计算周期输入的待计算的数据发送至所述光子神经网络芯片,以使所述光子神经网络芯片对所述目标数据以及所述下一计算周期输入的待计算的数据进行卷积层计算。3.根据权利要求1所述的基于光子神经网络芯片的智能信号处理系统,其特征在于:对所述光子神经网络芯片进行训练,所述训练包括:基于所述待计算的数据,确定出所述光子神经网络芯片的网络运算架构;基于所述网络运算架构,确定出待求解的目标相位参数;基于所述目标相位参数以及斐索干涉仪的预设参数值,确定出所述斐索干涉仪的目标参数值。4.根据权利要求1所述的基于光子神经网络芯片的智能信号处理系统,其特征在于:基于所述网络运算架构,确定出待求解的目标相位参数,包括:基于所述网络运算架构,确定出三维矩阵和二维矩阵;基于所述三维矩阵以及所述二维矩阵,确定出所述待求解的目标相位参数。5.根据权利要求1所述的基于光子神经网络芯片的智能信号处理系统,其特征在于:所述光芯片包括fpga、arm、dsp、cpu、gpu中的任意一个。6.根据权利要求1所述的基于光子神经网络芯片的智能信号处理系统,其特征在于:所述光子神经网络芯片包括控制单元、i/o接口、缓冲单元以及运算单元;所述i/o接口用于接收输入所述光子神经网络芯片的输入信号,并将所述输入信号发送至所述缓冲单元以及所述运算单元;所述运算单元用于接收所述输入信号,并对所述输入信号进行计算,生成输出信号;所述缓冲单元用于存储所述输入信号以及所述输出信号;所述控制单元用于基于芯片控制指令,执行与所述芯片控制指令相对应的执行动作。

技术总结

本发明公开了一种基于光子神经网络芯片的智能信号处理系统,包括光芯片和光子神经网络芯片;待计算的数据通过所述光芯片发送至所述光子神经网络芯片;所述光子神经网络芯片对所述待计算的数据进行卷积层计算,生成中间数据,并发送所述中间数据至所述光芯片;所述光芯片对所述中间数据进行卷积层计算,生成目标数据。本发明利用光子神经网络芯片大幅加速神经网络计算速度,相较传统电子芯片的计算速度提升数个数量级;同时,该系统结合电子技术的存储功能和任意信号处理功能,避免了光路中无法存储和无法优质处理信号的劣势。法存储和无法优质处理信号的劣势。

技术研发人员:白冰

受保护的技术使用者:光子算数(苏州)智能科技有限公司

技术研发日:2020.04.30

技术公布日:2021/11/2

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。