技术特征:

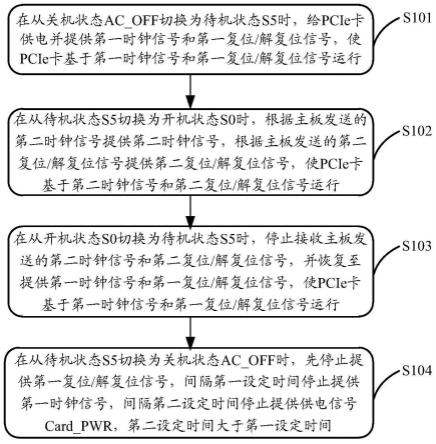

1.一种时序控制方法,其特征在于,包括:在从关机状态切换为待机状态时,给pcie卡供电并提供第一时钟信号和第一复位/解复位信号,使所述pcie卡基于所述第一时钟信号和所述第一复位/解复位信号运行;在从所述待机状态切换为开机状态时,根据主板发送的第二时钟信号提供所述第二时钟信号,根据所述主板发送的第二复位/解复位信号提供所述第二复位/解复位信号,使所述pcie卡基于所述第二时钟信号和所述第二复位/解复位信号运行;在从所述开机状态切换为所述待机状态时,停止接收所述主板发送的第二时钟信号和第二复位/解复位信号,并恢复至提供所述第一时钟信号和所述第一复位/解复位信号,使所述pcie卡基于所述第一时钟信号和所述第一复位/解复位信号运行。2.根据权利要求1所述的时序控制方法,其特征在于:所述给pcie卡供电并提供第一时钟信号和第一复位/解复位信号,包括:给所述pcie卡提供供电信号,并在所述供电信号稳定一段时间后,给所述pcie卡提供所述第一时钟信号;在所述第一时钟信号持续一段时间后,提供所述第一复位/解复位信号;和/或,所述时序控制方法还包括:在从所述待机状态切换为所述关机状态时,先停止提供所述第一复位/解复位信号,间隔第一设定时间停止提供所述第一时钟信号,间隔第二设定时间停止提供所述供电信号,所述第二设定时间大于所述第一设定时间。3.根据权利要求1或2所述的时序控制方法,其特征在于,所述根据主板发送的第二时钟信号提供所述第二时钟信号,包括:接收所述主板发送的第二时钟信号,并根据所述第二时钟信号将所述第一时钟信号调整为所述第二时钟信号后提供给所述pcie卡;或,接收所述主板发送的第二时钟信号,并将提供给所述pcie卡的时钟信号由所述第一时钟信号切换为所述主板发送的所述第二时钟信号。4.根据权利要求1-3中任一项所述的时序控制方法,其特征在于,所述时序控制方法还包括:接收所述pcie卡发送的故障信号,所述故障信号用于表示所述pcie卡是否出现故障而需要进行复位/解复位操作;所述使所述pcie卡基于所述第一时钟信号和所述第一复位/解复位信号运行,包括:根据所述第一复位/解复位信号和所述故障信号进行逻辑运算后获得复位/解复位信号,使所述pcie卡基于所述第一时钟信号和所述复位/解复位信号运行;和/或,所述使所述pcie卡基于所述第二时钟信号和所述第二复位/解复位信号运行,包括:根据所述第二复位/解复位信号和所述故障信号进行逻辑运算后获得复位/解复位信号,使所述pcie卡基于所述第二时钟信号和所述复位/解复位信号运行。5.一种时序控制电路,其特征在于,包括:振荡器,用于输出第一时钟信号;时钟电路,用于接收所述第一时钟信号和在开机状态接收主板发送的第二时钟信号;控制电路和逻辑电路,所述控制电路用于向所述逻辑电路的第一输入端发送第一复位/解复位信号,所述逻辑电路的第二输入端用于在所述开机状态接收所述主板发送的第二复位/解复位信号;其中,在待机状态,所述时钟电路用于输出所述第一时钟信号给pcie卡,所述逻辑电路

用于基于所述第一复位/解复位信号输出复位/解复位信号给所述pcie卡;在所述开机状态,所述时钟电路用于输出所述第二时钟信号给pcie卡,所述逻辑电路用于基于所述第二复位/解复位信号输出所述复位/解复位信号给所述pcie卡。6.根据权利要求5所述的时序控制电路,其特征在于:所述控制电路用于在确定接收到所述时钟电路输出的第一消息后,输出所述第一复位/解复位信号,所述第一消息用于表示所述时钟电路能够输出稳定的所述第一时钟信号或所述第二时钟信号;和/或,所述控制电路用于向所述时钟电路发送控制信号,所述控制信号用于确定所述时钟电路向所述pcie卡发送所述第一时钟信号的开始时间。7.根据权利要求5或6所述的时序控制电路,其特征在于,所述逻辑电路包括:与门,所述与门的第一输入端与所述控制电路的输出端连接,以接收所述第一复位/解复位信号,所述与门的第二输入端用于与所述主板连接,以接收所述主板发送的所述第二复位/解复位信号,所述与门的输出端用于输出所述复位/解复位信号给所述pcie卡。8.根据权利要求7所述的时序控制电路,其特征在于,所述时序控制电路还包括:下拉电路,与所述与门的第一输入端连接,并用于在所述控制电路未输出所述第一复位/解复位信号时将所述与门的第一输入端下拉为逻辑低电平;和/或,第一上拉电路,与所述与门的第二输入端连接,并用于在未接收到所述第二复位/解复位信号时将所述与门的第二输入端上拉为逻辑高电平。9.根据权利要求5-8中任一项所述的时序控制电路,其特征在于:在所述待机状态,所述逻辑电路用于输出所述第一复位/解复位信号给所述pcie卡;在所述开机状态,所述逻辑电路用于输出所述第二复位/解复位信号给所述pcie卡。10.根据权利要求5-8中任一项所述的时序控制电路,其特征在于,所述逻辑电路还用于接收所述pcie卡发送的故障信号或所述逻辑电路还用于接收所述控制电路基于所述pcie卡发送的至少一个第一故障信号判断是否需要进行复位/解复位操作后输出的故障信号,所述故障信号用于表示所述pcie卡是否出现故障而需要进行复位/解复位操作;其中,在待机状态,所述逻辑电路用于基于所述第一复位/解复位信号和所述故障信号输出所述复位/解复位信号给所述pcie卡;在所述开机状态,所述逻辑电路用于基于所述第二复位/解复位信号和所述故障信号输出所述复位/解复位信号给所述pcie卡。11.根据权利要求10所述的时序控制电路,其特征在于,所述逻辑电路的与门还包括第三输入端,所述第三输入端用于接收所述故障信号,所述时序控制电路还包括第二上拉电路,所述第二上拉电路与所述与门的第三输入端连接,并用于在未接收到所述故障信号时将所述与门的第三输入端上拉为逻辑高电平。12.一种转接卡,其特征在于,包括:电路板,具有金手指,所述金手指用于插设在主板的插槽上;根据权利要求5-11中任一项所述的时序控制电路,设置在所述电路板上。13.一种计算设备,其特征在于,包括:主板,所述主板上设置有插槽,根据权利要求12所述的转接卡,所述转接卡的金手指插设在所述插槽内;pcie卡,安装在所述转接卡上,

其中,所述主板用于在开机状态提供第二时钟信号和第二复位/解复位信号给所述转接卡的时序控制电路;在待机状态下,所述时序控制电路输出第一时钟信号和基于第一复位/解复位信号输出复位/解复位信号给所述pcie卡;在所述开机状态,所述时序控制电路输出所述第二时钟信号和基于所述第二复位/解复位信号输出所述复位/解复位信号给所述pcie卡。

技术总结

一种时序控制方法和电路、转接卡、计算设备。方法包括:从关机状态切换为待机状态,给PCIe卡供电并提供第一时钟信号和第一复位/解复位信号,使PCIe卡基于第一时钟信号和第一复位/解复位信号运行;从待机状态切换为开机状态,根据主板发送的第二时钟信号和第二复位/解复位信号分别提供第二时钟信号和第二复位/解复位信号,使PCIe卡基于第二时钟信号和第二复位/解复位信号运行;从开机状态切换为待机状态,恢复至提供第一时钟信号和第一复位/解复位信号,使PCIe卡基于第一时钟信号和第一复位/解复位信号运行。该方法使PCIe卡在待机状态运行,使开机时计算设备能够较快扫描到PCIe卡,避免识别不到PCIe卡。避免识别不到PCIe卡。避免识别不到PCIe卡。

技术研发人员:夏万祺 商赛奇 陈卓

受保护的技术使用者:超聚变数字技术有限公司

技术研发日:2022.11.16

技术公布日:2023/3/10

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。