技术特征:

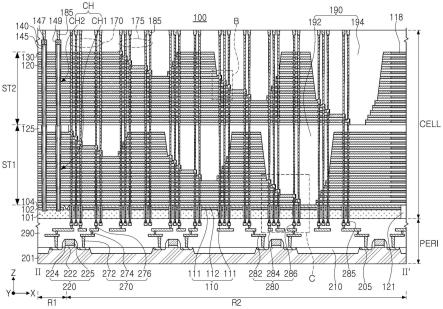

1.一种半导体器件,包括:第一半导体结构,所述第一半导体结构包括第一衬底、位于所述第一衬底上的电路元件和下互连线;以及第二半导体结构,所述第二半导体结构位于所述第一半导体结构上,其中,所述第二半导体结构包括:第二衬底,所述第二衬底具有第一区域和第二区域,栅电极,所述栅电极在第一方向上彼此间隔开地堆叠在所述第二衬底上,所述栅电极至少部分地限定第一堆叠结构和第二堆叠结构,层间绝缘层,所述层间绝缘层与所述栅电极交替堆叠,沟道结构,所述沟道结构穿透所述第一堆叠结构和所述第二堆叠结构,所述沟道结构在所述第一方向上延伸,所述沟道结构分别包括沟道层,所述沟道结构位于所述第一区域中,分隔区域,所述分隔区域穿透所述第一堆叠结构和所述第二堆叠结构并且在第二方向上延伸,第一接触插塞和第二接触插塞,所述第一接触插塞和所述第二接触插塞均穿透所述第一堆叠结构和所述第二堆叠结构并且在所述第一方向上延伸到所述第一半导体结构中,所述第一接触插塞和所述第二接触插塞位于所述第二区域中,以及接触绝缘层,所述接触绝缘层与一部分所述栅电极接触并且围绕所述第一接触插塞和所述第二接触插塞中的每一个接触插塞,所述接触绝缘层位于所述第二区域中,其中,所述第一堆叠结构在所述第二区域中具有:第一焊盘区域,在所述第一焊盘区域中每一个所述栅电极在所述第二方向上比位于其上方的栅电极延伸得更远以连接到相应的所述第一接触插塞,以及第一虚设区域,所述第一虚设区域位于每一个所述第一焊盘区域的至少一侧并且与所述第一接触插塞间隔开,其中,所述第二堆叠结构在所述第二区域中具有:第二焊盘区域,在所述第二焊盘区域中每一个所述栅电极在所述第二方向上比位于其上方的栅电极延伸得更远并且连接到相应的所述第二接触插塞,以及第二虚设区域,所述第二虚设区域位于每一个所述第二焊盘区域的至少一侧并且与所述第二接触插塞间隔开,并且其中,所述第一焊盘区域在所述第一方向上与所述第二虚设区域交叠,并且所述第二焊盘区域在所述第一方向上与所述第一虚设区域交叠。2.根据权利要求1所述的半导体器件,其中,所述第一焊盘区域和所述第二焊盘区域在所述第二方向上交替设置。3.根据权利要求1所述的半导体器件,其中,所述第一焊盘区域和所述第二焊盘区域中的每一个焊盘区域具有由所述栅电极至少部分地限定的台阶形状,并且所述第一虚设区域和所述第二虚设区域各自具有突出区域,在所述突出区域中堆叠的所述栅电极的数量与所述第一焊盘区域和所述第二焊盘区域中堆叠的所述栅电极的数量相同,或大于所述第一焊盘区域和所述第二焊盘区域中堆叠的所述栅电极的数量。

4.根据权利要求3所述的半导体器件,其中,所有所述第一虚设区域中的突出区域具有相同的最大高度,并且所有所述第二虚设区域中的突出区域具有相同的最大高度。5.根据权利要求3所述的半导体器件,其中,所述第二虚设区域各自的突出区域的最大高度在所述第二方向上依次减小。6.根据权利要求1所述的半导体器件,其中,每一个所述第一焊盘区域包括:第一子焊盘区域和第二子焊盘区域;以及至少一个平坦区域,所述至少一个平坦区域位于所述第一子焊盘区域和所述第二子焊盘区域中每一者的至少一侧。7.根据权利要求6所述的半导体器件,其中,与穿透所述第一子焊盘区域和所述第二子焊盘区域的所述第一接触插塞连接的至少一些所述下互连线在所述至少一个平坦区域下方延伸。8.根据权利要求1所述的半导体器件,其中,所述第一焊盘区域和所述第二焊盘区域以及所述第一虚设区域和所述第二虚设区域各自具有所述栅电极至少部分地限定台阶形状的区域,并且在所述第一焊盘区域和所述第二焊盘区域中,所述区域具有第一斜率,而在所述第一虚设区域和所述第二虚设区域中,所述区域具有大于所述第一斜率的第二斜率。9.根据权利要求1所述的半导体器件,其中,所述第一焊盘区域和所述第二焊盘区域具有随着距所述第一区域的距离增加而减小的高度。10.根据权利要求1所述的半导体器件,其中,在所述第一区域中,所述栅电极具有第一厚度,并且在所述第一焊盘区域和所述第二焊盘区域中,最上面的所述栅电极具有大于所述第一厚度的第二厚度。11.根据权利要求10所述的半导体器件,其中,所述第一虚设区域和所述第二虚设区域中的每一个虚设区域具有突出区域,在所述突出区域中所述栅电极以比所述第一焊盘区域和所述第二焊盘区域中堆叠的所述栅电极的数量更大的数量堆叠,并且在所述第一虚设区域和所述第二虚设区域各自的突出区域中,最上面的所述栅电极具有所述第一厚度。12.根据权利要求10所述的半导体器件,其中,所述接触绝缘层在所述第一焊盘区域和所述第二焊盘区域中位于最上面的所述栅电极下方。13.根据权利要求1所述的半导体器件,其中,所述第一焊盘区域和所述第二焊盘区域中的每一个焊盘区域在所述第二方向上具有30μm至70μm的长度。14.一种半导体器件,包括:第一衬底;电路元件,所述电路元件位于所述第一衬底上;下互连线,所述下互连线电连接到所述电路元件;第二衬底,所述第二衬底位于所述下互连线上;栅电极,所述栅电极在第一方向上彼此间隔开地堆叠在所述第二衬底上,所述栅电极

至少部分地限定第一堆叠结构和第二堆叠结构;沟道结构,所述沟道结构穿透所述栅电极,所述沟道结构在所述第一方向上延伸,所述沟道结构分别包括沟道层;以及第一接触插塞和第二接触插塞,所述第一接触插塞和所述第二接触插塞各自穿透所述第一堆叠结构和所述第二堆叠结构,所述第一接触插塞和所述第二接触插塞分别连接到所述栅电极,所述第一接触插塞和所述第二接触插塞在所述第一方向上延伸,其中,所述第一堆叠结构具有第一焊盘区域,在所述第一焊盘区域中每一个所述栅电极在第二方向上比位于其上的栅电极延伸得更远并且连接到相应的所述第一接触插塞,其中,所述第二堆叠结构具有第二焊盘区域,在所述第二焊盘区域中每一个所述栅电极在所述第二方向上比位于其上的栅电极延伸得更远并且连接到相应的所述第二接触插塞,并且其中,所述第一焊盘区域和所述第二焊盘区域相对于彼此偏移以便在所述第一方向上彼此不交叠。15.根据权利要求14所述的半导体器件,其中,所述第一焊盘区域和所述第二焊盘区域均具有由所述栅电极至少部分地限定的台阶形状。16.根据权利要求15所述的半导体器件,其中,所述第一焊盘区域和所述第二焊盘区域中的每一个焊盘区域具有台阶区域,在所述台阶区域中堆叠的所述栅电极的数量在所述第二方向上减小。17.根据权利要求14所述的半导体器件,其中,所述第一堆叠结构还包括被定位在所述第一焊盘区域的至少一侧的第一虚设区域,其中,所述第一接触插塞不延伸穿过所述第一虚设区域,并且所述第二堆叠结构还包括被定位在所述第二焊盘区域的至少一侧的第二虚设区域,其中,所述第二接触插塞不延伸穿过所述第二虚设区域。18.根据权利要求17所述的半导体器件,其中,所述第一焊盘区域在所述第一方向上与所述第二虚设区域交叠,并且所述第二焊盘区域在所述第一方向上与所述第一虚设区域交叠。19.一种数据存储系统,包括:半导体存储装置,所述半导体存储装置包括:第一衬底;位于所述第一衬底上的电路元件;电连接到所述电路元件的下互连线;位于所述下互连线上的第二衬底;在第一方向上彼此间隔开地堆叠在所述第二衬底上并且至少部分地限定第一堆叠结构和第二堆叠结构的栅电极;穿透所述栅电极并且在所述第一方向上延伸并且分别包括沟道层的沟道结构;第一接触插塞和第二接触插塞,所述第一接触插塞和所述第二接触插塞均穿透所述第一堆叠结构和所述第二堆叠结构、连接到相应的所述栅电极并且在所述第一方向上延伸;以及,电连接到所述电路元件的输入/输出焊盘;以及控制器,所述控制器通过所述输入/输出焊盘电连接到所述半导体存储装置并且被配置为控制所述半导体存储装置,其中,所述第一堆叠结构包括第一焊盘区域,在所述第一焊盘区域中每一个所述栅电极在第二方向上比位于其上的栅电极延伸得更远并且连接到相应的所述第一接触插塞,其中,所述第二堆叠结构包括第二焊盘区域,在所述第二焊盘区域中每一个所述栅电

极在所述第二方向上比位于其上的栅电极延伸得更远并且连接到相应的所述第二接触插塞,并且其中,所述第一焊盘区域和所述第二焊盘区域相对于彼此偏移以便在所述第一方向上彼此不交叠。20.根据权利要求19所述的数据存储系统,其中,所述第一焊盘区域中的所述栅电极的形状与所述第二焊盘区域中的所述栅电极的形状相对应。

技术总结

提供半导体器件和包括该半导体器件的数据存储系统。半导体器件包括:第一衬底;电路元件;下互连线;第二衬底;栅电极,堆叠在第二衬底上以在第一方向上彼此间隔开并且形成第一堆叠结构和第二堆叠结构;沟道结构,穿透栅电极;以及第一接触插塞和第二接触插塞,分别穿透第一堆叠结构和第二堆叠结构,并且连接到栅电极。第一堆叠结构具有第一焊盘区域,在第一焊盘区域中栅电极分别比上栅电极延伸得更远,并且分别连接到第一接触插塞。第二堆叠结构具有第二焊盘区域,在第二焊盘区域中栅电极分别比上栅电极延伸得更远,并且分别连接到第二接触插塞。第一焊盘区域和第二焊盘区域相对于彼此偏移以便在第一方向上彼此不交叠。此偏移以便在第一方向上彼此不交叠。此偏移以便在第一方向上彼此不交叠。

技术研发人员:白石千 权美览 徐晟准 孙荣晥

受保护的技术使用者:三星电子株式会社

技术研发日:2022.05.27

技术公布日:2022/12/5

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。