技术特征:

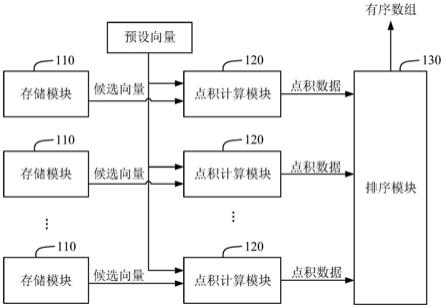

1.一种用于数据召回的fpga芯片,其特征在于,包括:多个存储模块,用于存储多个候选向量,每个候选向量对应一个待处理数据;多个点积计算模块,用于在每p个时钟周期,并行从对应的存储模块中读取候选向量,计算所述候选向量与预设向量的点积,得到对应的点积数据,其中p是根据读取一个所述候选向量需要消耗的时间确定的,p为正整数;排序模块,用于在每个时钟周期读取所述点积数据,并根据读取的所述点积数据进行排序操作,在经过多个时钟周期后,输出相应的有序数组,所述有序数组包括降序排列的多个点积数据,且所述有序数组中每个点积数据对应一个被召回的待处理数据。2.根据权利要求1所述的fpga芯片,其特征在于,所述排序模块包括依次连接的s 1个比较器模块,s为正整数;第i个比较器模块用于,在每至少2

i

个时钟周期,对连续输入到该比较器模块的2

i

个点积数据进行一轮排序,以有序向下一个比较器模块输出所述2

i

个点积数据,i为整数,且1≤i≤s;第s 1个比较器模块用于,在每至少k个时钟周期,将连续输入到该比较器模块的2

s

个点积数据与当前的参考缓存队列中的k个点积数据进行一轮排序,以有序向当前的输出缓存队列中写入排在前列的k个点积数据,k=2

s

;第s 1个比较器模块还用于,在完成对所有点积数据的排序后,输出包含排序完成时输出缓存队列中的k个点积数据的有序数组;其中,所述参考缓存队列用于存储所述第s 1个比较器模块前一轮排序得到的排在前列的k个点积数据,所述输出缓存队列用于存储所述第s 1个比较器模块本轮排序得到的排在前列的k个点积数据。3.根据权利要求2所述的fpga芯片,其特征在于,在前s个比较器模块中,每个比较器模块各对应两个缓存队列;所述第i个比较器模块用于通过如下方式对连续输入的2

i

个点积数据进行一轮排序:在每个时钟周期读取输入到该比较器模块的一个点积数据,并将所述点积数据写入到对应的两个缓存队列中的相应队列;其中,每连续输入的2

i-1

个点积数据被写入到同一个队列中;在每个时钟周期比较所述两个缓存队列中位于队头的两个点积数据,并向下一个比较器模块输出位于队头的两个点积数据中的较大者;将本轮排序的2

i

个点积数据作为目标点积数据,当本轮排序已输出其中一个缓存队列中的2

i-1

个目标点积数据时,在之后的每个时钟周期依次向下一个比较器模块输出一个另一缓存队列中剩余的目标点积数据,直至所述两个缓存队列中的共2

i

个目标点积数据均已输出,本轮排序完成。4.根据权利要求3所述的fpga芯片,其特征在于,所述第s 1个比较器模块用于通过如下方式将连续输入的2

s

个点积数据与当前的参考缓存队列中的k个点积数据进行一轮排序:在每个时钟周期读取输入到该比较器模块的一个点积数据,并将所述点积数据写入到输入缓存队列中;其中,所述输入缓存队列在所述第s 1个比较器模块每完成一轮排序后被清空;

在每个时钟周期比较所述输入缓存队列与当前的参考缓存队列中位于队头的两个点积数据,并向当前的输出缓存队列中写入位于队头的两个点积数据中的较大者,直至本轮排序已向所述输出缓存队列中连续写入k个点积数据后,本轮排序完成。5.根据权利要求4所述的fpga芯片,其特征在于,所述排序模块还包括逻辑处理模块;所述逻辑处理模块用于,每当所述第s 1个比较器模块完成一轮排序后,将所述输入缓存队列和当前的参考缓存队列中剩余的点积数据清空,然后将当前的输出缓存队列切换为新的参考缓存队列,将当前的参考缓存队列切换为新的输出缓存队列。6.根据权利要求5所述的fpga芯片,其特征在于,所述fpga芯片还包括多路选择器以及多个过滤模块,在每个所述点积计算模块与对应的所述过滤模块之间设有第一缓存队列,在每个所述过滤模块与所述多路选择器之间设有第二缓存队列;所述逻辑处理模块还用于,每当所述第s 1个比较器模块完成一轮排序后,在将当前的输出缓存队列切换为新的参考缓存队列之前,将当前的输出缓存队列中位于队尾的最小点积数据分别输出给每个所述过滤模块;每个所述点积计算模块用于,在计算所述候选向量与预设向量的点积,得到对应的点积数据后,将所述点积数据写入到对应的第一缓存队列中;每个所述过滤模块用于,在每个时钟周期从对应的第一缓存队列中读取一个点积数据,并比较所述点积数据和所述最小点积数据,在所述点积数据大于所述最小点积数据时,将所述点积数据写入到对应的第二缓存队列中;所述多路选择器用于,在每个时钟周期从多个第二缓存队列中读取一个点积数据,并将读取的所述点积数据输出到所述排序模块。7.根据权利要求6所述的fpga芯片,其特征在于,所述多个存储模块、所述多个点积计算模块和所述多个过滤模块的数量均为m,m为正整数;每个所述点积计算模块还用于,在从对应的所述存储模块中读取到该存储模块中存储的最后一个候选向量后,且在将所述最后一个候选向量对应的最后一个点积数据写入到对应的第一缓存队列后,在下一个时钟周期,向对应的所述第一缓存队列写入一个初始结束标志;每个所述过滤模块还用于,在从对应的所述第一缓存队列中读取到所述初始结束标志后,将所述初始结束标志写入到对应的所述第二缓存队列中;所述多路选择器还用于,在从m个第二缓存队列中读取到第m个初始结束标志时,确定已向所述排序模块输出的点积数据的总量n,在所述总量n不为k的整数倍时,在之后的每个时钟周期继续向所述排序模块输出一个用于补齐的点积数据,直至所述总量n为k的整数倍,在输出最后一个用于补齐的点积数据后,在下一个时钟周期,向所述排序模块输出一个最终结束标志,n为正整数;在所述排序模块中,所述第i个比较器模块还用于,在读取到输入到该比较器模块的最终结束标志后,将所述最终结束标志写入到对应的两个缓存队列中的其中一个队列,并在当前轮次的排序完成后,向下一个比较器模块输出所述最终结束标志;所述第s 1个比较器模块用于,在读取到输入到该比较器模块的最终结束标志后,在当前轮次的排序完成后,输出包括所述输出缓存队列中k个点积数据的所述有序数组。8.根据权利要求1-7任一项所述的fpga芯片,其特征在于,所述多个存储模块的数量为

m,m为正整数;其中,所述多个候选向量是通过如下方式存储在m个存储模块中:按照m个存储模块之间的预设顺序,依次将m个候选向量存储到对应的存储模块中,并循环上述过程,直至所述多个候选向量均被存储;其中,同一存储模块存储的各候选向量中,相邻候选向量之间的存储地址连续;其中,每个所述点积计算模块用于,在每p个时钟周期,根据连续的存储地址从对应的存储模块中顺序读取该存储模块中存储的一个候选向量。9.一种数据召回方法,其特征在于,应用于fpga芯片,所述fpga芯片包括多个存储模块、多个点积计算模块以及排序模块,每个存储模块中分别存储多个候选向量,且每个候选向量对应一个待处理数据;所述方法包括:在每p个时钟周期,所述多个点积计算模块并行从对应的存储模块中读取候选向量,计算所述候选向量与预设向量的点积,得到对应的点积数据,其中p是根据读取一个所述候选向量需要消耗的时间确定的,p为正整数;在每个时钟周期,所述排序模块读取所述点积数据,并根据读取的所述点积数据进行排序操作,在经过多个时钟周期后,输出相应的有序数组,所述有序数组包括降序排列的多个点积数据,且所述有序数组中每个点积数据对应一个被召回的待处理数据。10.根据权利要求9所述的方法,其特征在于,所述排序模块包括依次连接的s 1个比较器模块,且每个比较器模块并行工作,s为正整数;所述排序模块读取所述点积数据,并根据读取的所述点积数据进行排序操作,在经过多个时钟周期后,输出相应的有序数组,包括:在每至少2

i

个时钟周期,第i个比较器模块对连续输入到该比较器模块的2

i

个点积数据进行一轮排序,以有序向下一个比较器模块输出所述2

i

个点积数据,i为整数,且1≤i≤s;在每至少k个时钟周期,第s 1个比较器模块将连续输入到该比较器模块的2

s

个点积数据与当前的参考缓存队列中的k个点积数据进行一轮排序,以有序向当前的输出缓存队列中写入排在前列的k个点积数据,k=2

s

;在完成对所有点积数据的排序后,第s 1个比较器模块输出包含排序完成时输出缓存队列中的k个点积数据的有序数组;其中,所述参考缓存队列用于存储所述第s 1个比较器模块前一轮排序得到的排在前列的k个点积数据,所述输出缓存队列用于存储所述第s 1个比较器模块本轮排序得到的排在前列的k个点积数据。11.根据权利要求10所述的方法,其特征在于,在前s个比较器模块中,每个比较器模块各对应两个缓存队列;所述在每至少2

i

个时钟周期,第i个比较器模块对连续输入到该比较器模块的2

i

个点积数据进行一轮排序,以有序向下一个比较器模块输出所述2

i

个点积数据,包括:在每个时钟周期,第i个比较器模块读取输入到该比较器模块的一个点积数据,并将所述点积数据写入到对应的两个缓存队列中的相应队列;其中,每连续输入的2

i-1

个点积数据被写入到同一个队列中;在每个时钟周期,第i个比较器模块比较所述两个缓存队列中位于队头的两个点积数据,并向下一个比较器模块输出位于队头的两个点积数据中的较大者;将本轮排序的2

i

个点积数据作为目标点积数据,当本轮排序已输出其中一个缓存队列中的2

i-1

个目标点积数据时,第i个比较器模块在之后的每个时钟周期依次向下一个比较器

模块输出一个另一缓存队列中剩余的目标点积数据,直至所述两个缓存队列中的共2

i

个目标点积数据均已输出,本轮排序完成。12.根据权利要求11所述的方法,其特征在于,所述在每至少k个时钟周期,第s 1个比较器模块将连续输入到该比较器模块的2

s

个点积数据与当前的参考缓存队列中的k个点积数据进行一轮排序,以有序向当前的输出缓存队列中写入排在前列的k个点积数据,包括:在每个时钟周期,第s 1个比较器模块读取输入到该比较器模块的一个点积数据,并将所述点积数据写入到输入缓存队列中;其中,所述输入缓存队列在所述第s 1个比较器模块每完成一轮排序后被清空;在每个时钟周期,第s 1个比较器模块比较所述输入缓存队列与当前的参考缓存队列中位于队头的两个点积数据,并向当前的输出缓存队列中写入位于队头的两个点积数据中的较大者,直至本轮排序已向所述输出缓存队列中连续写入k个点积数据后,本轮排序完成。13.根据权利要求12所述的方法,其特征在于,所述排序模块还包括逻辑处理模块;所述方法还包括:每当所述第s 1个比较器模块完成一轮排序后,所述逻辑处理模块将所述输入缓存队列和当前的参考缓存队列中剩余的点积数据清空,然后将当前的输出缓存队列切换为新的参考缓存队列,将当前的参考缓存队列切换为新的输出缓存队列。14.根据权利要求13所述的方法,其特征在于,所述fpga芯片还包括多路选择器以及多个过滤模块,在每个所述点积计算模块与对应的所述过滤模块之间设有第一缓存队列,在每个所述过滤模块与所述多路选择器之间设有第二缓存队列;所述方法还包括:每当所述第s 1个比较器模块完成一轮排序后,在将当前的输出缓存队列切换为新的参考缓存队列之前,所述逻辑处理模块将当前的输出缓存队列中位于队尾的最小点积数据分别输出给每个所述过滤模块;在计算所述候选向量与预设向量的点积,得到对应的点积数据后,所述点积计算模块将所述点积数据写入到对应的第一缓存队列中;在每个时钟周期,每个所述过滤模块从对应的第一缓存队列中读取一个点积数据,并比较所述点积数据和所述最小点积数据,在所述点积数据大于所述最小点积数据时,将所述点积数据写入到对应的第二缓存队列中;在每个时钟周期,所述多路选择器从多个第二缓存队列中读取一个点积数据,并将读取的所述点积数据输出到所述排序模块。15.根据权利要求14所述的方法,其特征在于,所述多个存储模块、所述多个点积计算模块和所述多个过滤模块的数量均为m,m为正整数;所述方法还包括:每个所述点积计算模块在从对应的所述存储模块中读取到该存储模块中存储的最后一个候选向量后,且在将所述最后一个候选向量对应的最后一个点积数据写入到对应的第一缓存队列后,等待下一个时钟周期,并在下一个时钟周期,向对应的所述第一缓存队列写入一个初始结束标志;每个所述过滤模块在从对应的所述第一缓存队列中读取到所述初始结束标志后,将所述初始结束标志写入到对应的所述第二缓存队列中;所述多路选择器在从m个第二缓存队列中读取到第m个初始结束标志时,确定已向所述

排序模块输出的点积数据的总量n,在所述总量n不为k的整数倍时,在之后的每个时钟周期继续向所述排序模块输出一个用于补齐的点积数据,直至所述总量n为k的整数倍,在输出最后一个用于补齐的点积数据后,等待下一个时钟周期,并在下一个时钟周期,向所述排序模块输出一个最终结束标志,n为正整数;所述排序模块的第i个比较器模块,在读取到输入到该比较器模块的最终结束标志后,将所述最终结束标志写入到对应的两个缓存队列中的其中一个队列,并在当前轮次的排序完成后,向下一个比较器模块输出所述最终结束标志;所述在完成对所有点积数据的排序后,第s 1个比较器模块输出包含排序完成时输出缓存队列中的k个点积数据的有序数组,包括:所述第s 1个比较器模块在读取到输入到该比较器模块的最终结束标志后,在当前轮次的排序完成后,输出包括所述输出缓存队列中k个点积数据的有序数组。16.根据权利要求9-15任一项所述的方法,其特征在于,所述多个存储模块的数量为m,m为正整数;所述方法还包括:按照m个存储模块之间的预设顺序,依次将m个候选向量存储到对应的存储模块中,并循环上述过程,直至所述多个候选向量均被存储;其中,同一存储模块存储的各候选向量中,相邻候选向量之间的存储地址连续;所述在每p个时钟周期,所述多个点积计算模块并行从对应的存储模块中读取候选向量,包括:在每p个时钟周期,每个所述点积计算模块根据连续的存储地址从对应的存储模块中顺序读取该存储模块中存储的一个候选向量。

技术总结

本公开涉及一种用于数据召回的FPGA芯片和数据召回方法,FPGA芯片包括:多个存储模块,用于存储多个候选向量;多个点积计算模块,用于在每p个时钟周期,并行从对应的存储模块中读取候选向量,计算候选向量与预设向量的点积,得到对应的点积数据;排序模块,用于在每个时钟周期读取点积数据,并根据读取的点积数据进行排序操作,在经过多个时钟周期后,输出相应的有序数组,有序数组包括降序排列的多个点积数据。在本公开中,点积计算过程与排序过程可以完全流水式地执行起来,每个时钟周期,每个模块都在并行工作,当点积计算完成时,排序过程也基本上完成,可以极大提升召回效率。可以极大提升召回效率。可以极大提升召回效率。

技术研发人员:甯青松 韩耀东 蒋宇航 曾朝亮 罗腊咏 王剑

受保护的技术使用者:北京有竹居网络技术有限公司

技术研发日:2022.02.17

技术公布日:2022/5/25

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。