技术特征:

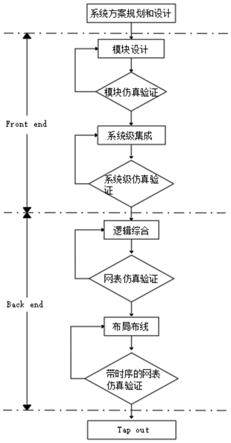

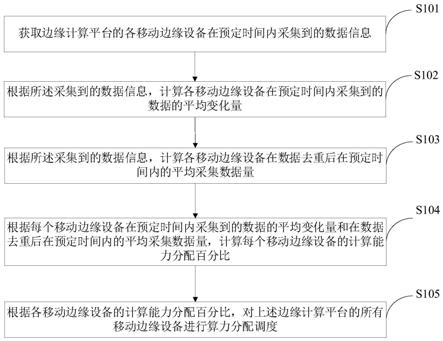

1.一种支持soc设计全流程开发的软件和硬件协同仿真系统,包括testbench,testcase和result,其特征在于:所述testbench的内部包括有software和hardware,所述testcase的内部包括有software、hardware和uvm,所述result的内部包括有wave、log和coverage;testbench:该testbench中存放的是仿真和验证系统用到的一些公用的内容,这一部分内容由本系统专职维护人员来负责,团队中的其他验证工程师不需要关注,这一部分中又可以分为两个部分按照对软硬件的支持划分为software(软件)和hardware(硬件),分别负责对系统中软件环境和硬件环境的处理;testcase:该testcase和testbench同属于仿真验证系统的一部分共同构建成仿真环境,不同的地方在于testcase可以由系统使用者自由构建激励,由于testbench已经准备好了完善的hardware和software环境,此处验证工程师具有很高的灵活性,可以充分利用软件和硬件的方式来产生激励,并且testcase中预留了uvm的部分给验证工程师灵活的构建sequence,作为对testbench中hardware的uvm sequence的补充,所以本系统的激励有三种类型可选,验证工程师可以根据需要决定选择其中的一种、两种或者全部类型去构建并实现各种复杂场景的仿真;result:该部分用于存放仿真中产生的各种结果,wave里面存放本系统运行后生成的各种波形文件,支持主流的fsdb、vpd等格式,方便验证工程师利用自己熟悉的波形文件和debug工具定位问题,log目录存放系统编译和仿真阶段产生的打印报告,coverage目录存放仿真的覆盖率相关的文件用于cdv(覆盖率驱动验证)仿真使用,验证工程师可以使用代码覆盖率、断言覆盖率以及coverage group任意的方式去检查所关注的覆盖率类型,灵活地采用各种方式去保证验证的收敛。2.根据权利要求1所述的一种支持soc设计全流程开发的软件和硬件协同仿真系统,其特征在于,本发明使用步骤如下:步骤

①

:需要使用者准备好各种所需的激励,如:software里放置使用c代码和汇编代码编写的激励,hardware里放置verilog类型代码激励,uvm内则放置使用uvm的sequence,然后启动开始命令指定需要仿真的testcase,运行本系统;步骤

②

:系统会自动判断仿真的类型,判断依据是根据激励中是否有软件类型的激励来进行分类,这里根据soc仿真的流程可以分为模块级仿真和系统级仿真两类:情况1当需要的做的是模块级仿真时,由于这种仿真是不需要软件激励的所以当系统判断步骤

①

的输入文件中没有软件激励的时候,系统都会自动判断为需要进行的是模块级仿真或者不带处理器的子系统仿真,如图5的

②

所示此时的激励可以是hardware和uvm中的一种或者两种时。系统进行判断后会自动跳过步骤

③

和

④

进入到步骤

⑤

,情况2如果在步骤

①

判断激励中含有c代码等软件激励则会向下执行,进入步骤

③

;步骤

③

:系统此时识别到要需要处理软件激励,会自动调用testbench的software(如图5所示

①

)内的文件对软件代码进行编译处理,产生可以用于软件和硬件协同仿真的二进制文件,整个过程如图3所示,此阶段可以看作是software的处理阶段没有硬件参与;步骤

④

:这个阶段系统已经完成了软件代码的处理,系统会自动把软件编译好的二进制文件进行放在result中对应testcase名字的目录下,其中也会包括编译的过程文件如汇编文件等,如图3所示,这个阶段系统会把处理后的软件和硬件准备好形成一套可以使用软

件激励驱动的系统级的仿真环境;步骤

⑤

:系统会根据使用者的需要添加仿真需要的硬件模型,可选的模型存放在图5中

④

所示的model当中,不管是模块级仿真还是系统级在这步都有模型可以进行选择,唯一不同的是如果流程是从步骤

②

跳转到步骤

⑤

,此时想仿真处理器的操作就只能选择处理器的行为级模型,而对于经历了步骤

③④

再到

⑤

的流程是不需要选择处理器的行为级模型,因为软件仿真的流程和步骤

③④

的准备工作都是针对处理器的仿真来做的,经过

③④

的处理平台中已经具备了处理器仿真所需要的硬件和软件不再需要处理器的模型,对于处理器模型以外的外设模型无论是模块级仿真还是系统级仿真都可以根据自己的情况选择或者不选择;步骤

⑥

:这个阶段系统会把使用者选择添加的硬件模型加入到硬件环境当中,使所选模型和soc芯片的代码结合起来形成一个整体成为可以被仿真的dut如图9所示,图中所有的内容都被称作dut(design under test),是系统仿真的直接对象,其中bfm代表一个处理器的功能模型,下面的model1则可以代表任意一个外设的模型,由于本系统testbench中的hardware部分(见图5的

④

)对各种硬件模型具有良好的支持,因此这里可选的模型覆盖soc开发各阶段工作的需要,可提供verilog和systemverilog等各种类型的模型供仿真使用;步骤

⑦

:系统会自动对dut进行编译操作,这个过程中还会包括对硬件环境的代码规则检查,产生的结果会存在result下对应仿真的testcase名字的log目录(如图5的

③

所示)方便查询相关的信息,一般来说没有错误提示的结果不影响后续的操作,所以本系统的自动化流程会继续执行下一步的操作,如果这个阶段发生了错误本系统会自动停止后续的操作,使用者需要去result中查看log中错误信息,解决后重新开始仿真,如果没有任何错误发生系统会自动向下进入步骤

⑧

;步骤

⑧

:系统在这个阶段会对之前构建的软件和硬件协同仿真环境(完成步骤

③④⑤⑥⑦

操作后形成)或者单独的硬件仿真环境(完成步骤

⑤⑥⑦

操作后形成)进行仿真(simulation),本系统会根据使用者在步骤

①

输入的命令选择对应的仿真器(simulator),也会根据命令来选择进行前仿真(front

‑

end simulation)或者后仿真(back

‑

end simulation),所以不管是模块级仿真还是系统级仿真,不管是rtl仿真还是netlist仿真此处都能完成,本系统因此支持对soc全流程开发的仿真需求;步骤

⑨

:这个阶段是判断仿真结果是否正常的阶段,主要是手段通过log中打印信息给出相关错误信息的提示供工程师分析,打印信息的手段可以是硬件通过$display函数打印的信息的信息也可以是通过systemverilog assert方式打印的信息,在有软件激励参与的系统仿真中还可以使用软件的打印信息作为补充,使用者可以根据激励中预先设置的信息来判断仿真结果,这部分的内容和结果文件保存在result(如图5的

③

所示)当中,除了log外系统还给使用者提供wave和coverage等文件帮助分析仿真结果,使用者通过对result中仿真结果文件分析准确判断仿真是否通过,并可以通过debug工具定位问题后重新返回步骤

①

再次进行仿真直到获得正确的结果;步骤

⑩

:这个阶段表示单个testcase仿真流程的结束,但是并不意味着模块级仿真或者系统级仿真的结束,所以这是一个必不可少的阶段,见图5的

③

,这个阶段根据系统运行的不同的testcase会在result目录下产生不同的testcase名称的目录,每个testcase的目录下又包含各自wave、log和coverage的目录用于存放仿真后的分类结果,对于cdv(覆盖率

驱动的验证)来说单独的用例一般无法满足code coverage(代码覆盖率)或者function coverage(功能覆盖率)的要求,因此这里专门设置了coverage的目录存放相关的仿真结果,随着testcase仿真场景的增加可以使覆盖率不断得到完善,最终完成对功能覆盖率和代码覆盖率的要求。3.根据权利要求1所述的一种支持soc设计全流程开发的软件和硬件协同仿真系统,其特征在于:所述hardware是硬件的公共部分包括了对传统的verilog语言编写的硬件激励的支持,同时也包括对uvm方法学搭建的仿真环境的支持。当仿真需要软件或者硬件相关的文件时,系统会自动在testbench下的software和hardware中调取相关的文件。4.根据权利要求1所述的一种支持soc设计全流程开发的软件和硬件协同仿真系统,其特征在于:所述testbench中的hardware部分把通用接口和协议的模型包含了进来存放在专门的model目录下,所述testbench的hardware目录下专门设置了uvm的下级目录用于存放相关文件。5.根据权利要求1所述的一种支持soc设计全流程开发的软件和硬件协同仿真系统,其特征在于:所述software的目录会发生变化,里面不仅保留了之前项目对risc

‑ⅴ

的支持也增加对arm的支持。

技术总结

本发明公开了一种支持SOC设计全流程开发的软件和硬件协同仿真系统,包括testbench,testcase和Result,所述testbench的内部包括有software和hardware,所述testcase的内部包括有software、hardware和UVM。该支持SOC设计全流程开发的软件和硬件协同仿真系统提供了一套通用的仿真系统支持SOC的全流程的仿真和验证工作,具有简单的结构和使用方法,可以有效的避免SOC模块级平台开发过程中由于工程师个人经验的问题所引入的错误,缩减了了模块级平台搭建的时间,以及实现了模块级和系统级平台的统一。台的统一。台的统一。

技术研发人员:李宗昂

受保护的技术使用者:芯河半导体科技(无锡)有限公司

技术研发日:2021.10.13

技术公布日:2021/12/17

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。