由单晶硅制成的半导体晶片及其生产方法

1.本发明涉及一种由包含氧和氮的单晶硅制成的半导体晶片,其中该半导体晶片的正面覆盖有由硅制成的外延层。具有沉积的外延层的半导体晶片也称为外延半导体晶片。

2.当根据切克劳斯基法(cz法)从石英坩埚中所含的熔体中提拉用于生产半导体晶片的单晶时,坩埚材料形成掺入单晶以及由单晶所衍生的半导体晶片中的氧源。例如可以借助于控制通过提拉装置的氩气的压力和流量,或者借助于在提拉单晶期间调节坩埚和晶种的旋转,或者借助于施加到熔体上的磁场,或者通过这些措施的组合而十分精确地控制掺入的氧的浓度。

3.氧在bmd缺陷(bmd,块体微缺陷)的形成中起着重要作用。bmd是在热处理过程中bmd晶种生长到其中的氧沉淀物。它们充当内部吸除剂,即充当杂质的能量槽(energy sink),因此从根本上来说它们是有利的。一个例外是它们存在于计划用于容纳电子部件的位置。为了避免在这样的位置处形成bmd,可以在半导体晶片上沉积外延层,并设置为将电子部件容纳在外延层中。

4.wo 2019/011638a1公开了一种外延硅晶片及该外延硅晶片的包含外延后热处理的制造方法。该外延硅晶片包含八面体形状的bmd,通过ir断层成像确定,bmd的平均尺寸为13-35nm,平均密度不低于3x 108cm-3

且不高于4x 109cm-3

。该晶片的镍吸除效率为至少90%。

5.尽管所公开的晶片就镍吸除效率而言满足了器件工业的当前规范,但是外延后热处理实质上增加了表面缺陷的数量。

6.根据us 2006 0 150 894a1,可以通过将外延层沉积在从经受了预退火的单晶块上切割的衬底晶片上,来制造覆盖有外延层的半导体晶片。尽管这种外延晶片在表面缺陷的数量方面表现出相当好的性能,但其镍吸除效率仍然相对较差。

7.因此,本发明要解决的问题是提供一种外延硅晶片,该外延硅晶片显示出镍的有效吸除,以及外延层上相对较低数量的表面缺陷。

8.该问题通过由单晶硅制成的半导体晶片来解决,该半导体晶片具有根据新astm的氧浓度不小于5.0x 10

17

原子/cm3且不大于6.5x 10

17

原子/cm3,根据新astm的氮浓度不低于1.0x 10

13

原子/cm3且不大于1.0x 10

14

原子/cm3,其中该半导体晶片的正面覆盖有由硅制成的外延层,其中在对该覆盖有外延层的晶片在780℃的温度下进行3小时时段的热处理并在600℃的温度下进行10小时时段的热处理之后,该半导体晶片包含bmd,通过透射电子显微镜确定,bmd的平均尺寸不超过10nm,并且通过反应离子刻蚀确定,bmd在邻近外延层的区域中的平均密度不低于1.0x 10

11

cm-3

。

9.发明人发现,为了使表面缺陷的数量保持在相对较低的水准,bmd的平均尺寸需要严格限制为不超过10nm。特别地,在沉积外延层之后存在的表面缺陷的数量不应该通过外延前热处理(pre-epitaxial heat treatment)而显著增加。此外,为了确保相对高的镍吸除效率,需要存在相对较高的bmd密度。为了获得足够的活性作为内部吸除剂,bmd的密度必须不小于1.0x10

11

cm-3

。根据一个实施方案,镍吸除效率至少为95%。镍吸除效率定义为:ni的总有意污染量与两个晶片表面区域上的ni量之差与ni的总有意污染量的比。

10.根据一个实施方案,该半导体晶片具有根据新astm的间隙氧浓度不低于5.0x 10

17

原子/cm3且不高于6.5x 10

17

原子/cm3。

11.根据一个实施方案,该半导体晶片具有根据新astm的氮浓度不低于1.0x 10

13

原子/cm3且不高于1.0x 10

14

原子/cm3。通过使用ftir光谱仪测定红外吸收在波长为1107cm-1

的间隙氧浓度。该方法根据semi mf1188来执行。该方法根据国际可追溯标准进行校准。

12.通过使用ftir光谱仪测定红外吸收在波长为240cm-1

、250cm-1

和267cm-1

的氮浓度。测量前,将被测试材料加热至600℃,保持6小时。在测量期间,将样品冷却至10k。该方法通过具有已知氮浓度的标准品进行校正。

13.与sims的相关性如下:氮浓度ftir(原子/cm3)=0.6*氮浓度sims(原子/cm3)。

14.从半导体晶片的中心到边缘来确定bmd的尺寸和密度,并分别通过透射电子显微镜(tem)和反应离子刻蚀(rie)来进行评估。例如,在jp 2007123 543a2中公开的rie的原理。

15.bmd的平均尺寸定义为平均对角线尺寸。

16.表面缺陷可以作为lls(局部光散射缺陷)被检测。基于光散射操作的检测工具是可商购的。

17.根据一个实施方案,bmd的平均密度在邻近外延层的区域中沿深度方向逐渐降低。根据一个实施方案,在半导体晶片的与外延层和半导体晶片的正面之间的界面间隔不小于2μm且不大于7微米以及深度至少为35μm的区域中存在位错环。

18.本发明还涉及一种用于生产半导体晶片的方法,该半导体晶片是由单晶硅制成的,该方法包括:

19.在含有氢气的气氛中根据切克劳斯基法从包含氮的熔体中提拉单晶,该气氛中氢气的分压不小于5pa且不大于30pa,使得在具有均匀直径的单晶段中,氧浓度不低于5.0x 10

17

原子/cm3且不高于6.5x 10

17

原子/cm3,氮浓度不低于不低于1.0x 10

13

原子/cm3且不高于1.0x 10

14

原子/cm3;

20.控制提拉速度v,使得具有均匀直径的段中的单晶在pv区域中生长;

21.从具有均匀直径的单晶段分离半导体晶片;

22.以不低于0.5℃/min且不高于2℃/min的速率,将半导体晶片从不低于600℃的温度热处理至不高于900℃的目标温度;

23.以不低于0.5℃/min且不高于2℃/min的速率,将半导体晶片从目标温度冷却至不高于600℃的温度;

24.并且在经过热处理的半导体晶片的正面沉积硅的外延层,以形成外延半导体晶片。

25.pv区域是空位占主导地位的区域,但它被归类为无缺陷区域,因为在单晶的结晶过程中,晶体原生颗粒(cop)和氧化诱导的层错(osf)不会在其中形成。通过控制v/g、提拉速度v以及单晶与熔体间界面处的温度梯度g,单晶在pv区域生长。

26.根据本发明的方法包含在外延层的沉积之前,将半导体晶片从600℃热处理至不高于900℃,优选从600℃至850℃。优选地,热处理步骤在氮气或氩气或二者混合物的环境中实现。半导体晶片从600℃加热至目标温度的速率不低于0.5℃/min且不高于2℃/min,优选为1℃/min。半导体晶片从目标温度冷却至600℃的速率不低于0.5℃/min且不高于2℃/

min,优选为1℃/min。优选地,在半导体晶片达到目标温度后立即进行冷却。或者,可将半导体晶片保持在目标温度不长于180分钟的时段。为了防止bmd尺寸变大导致表面缺陷,目标温度应不高于900℃,并且升温速率应不低于0.5℃/min且不高于2℃/min。

27.根据一个实施方案,以这样的方式控制在具有均匀直径的单晶段中的氧的掺入,即氧的浓度不小于5.0x 10

17

原子/cm3且不大于6.5x 10

17

原子/cm3。

28.根据一个实施方案,以这样的方式控制在具有均匀直径的单晶段中的氧的掺入,即氧的浓度不小于5.0x 10

17

原子/cm3且不大于6.5x 10

17

原子/cm3。根据一个实施方案,在含有氢气的气氛中提拉用于从其中分离半导体晶片的硅单晶,其中氢气的分压不低于5pa且不高于30pa。

29.在单晶的提拉过程中,比率v/g必须保持在窄的范围内,在该范围内,单晶在pv区域中结晶时具有适当过量的空位。这是通过控制提拉速度v来控制比率v/g而实现的。特别地,选择提拉速度v,使得具有均匀直径的段中的单晶在pv区域中生长。

30.优选地,在具有均匀直径的整个单晶段,以所述方式控制提拉速度v,使得从该段切下的全部半导体晶片都是在pv区域中生长的。该段内单晶的直径和所得的半导体晶片的直径优选为不小于200mm,特别优选为不小于300mm。

31.随后对从具有均匀直径的单晶段切下的半导体晶片的上侧表面和下侧表面以及边缘进行一个或多个机械处理步骤以及至少一个抛光步骤。

32.在对半导体晶片进行如上所述的热处理后,以本身已知的方式将外延层沉积在半导体晶片的已抛光的上侧表面(正面)上。

33.外延层优选由单晶硅构成,且优选地具有2μm至7μm的厚度。

34.外延层沉积过程中的温度优选为1100℃至1150℃。

35.外延沉积后,由于向外扩散,半导体晶片不含任何可测量浓度的氢。

36.半导体晶片和外延层掺杂有电活性掺杂剂,例如硼,优选地类似于pp-掺杂的外延半导体晶片的掺杂。

37.在另一个实施方案中,晶片是nn-掺杂的外延晶片。

38.外延半导体晶片在邻近外延层的区域中形成bmd,bmd的平均尺寸不大于10nm,并且bmd的密度不小于1.0x 10

11

cm-3

,前提是该外延晶片已经在780℃的温度下进行了3小时的热处理,并且随后在600℃的温度下进行了10小时的热处理。热处理模拟用于生产电子器件的低热预算工艺步骤。tem用于确定bmd的平均尺寸,rie用于确定bmd的密度。

39.本发明的外延半导体晶片适用于客户的低热预算器件周期。

实施例

40.利用水平磁场,以高于0.45mm/min的提拉速率提拉300mm的单晶硅晶锭,使得具有均匀直径的晶锭段在pv区域内生长。向熔体中添加氮,并在包含分压为10pa的氢气的气氛中提拉晶体。热区的正确设计可确保径向v/g足够小,从而获得无团聚空位缺陷的硅晶片。

41.采用rt-ftir测量的晶锭氮浓度为1.2cm-3

至9x 10

13

cm-3

。采用rt-ftir测量的间隙氧浓度为5.8x 10

17

cm-3

至6.0x 10

17

cm-3

。

42.将晶锭切成段,单独切成300mm的硅晶片,研磨、清洁、双侧及镜面抛光。

43.测试晶片用于热处理和外延沉积。在每个测试晶片上施涂2.8μm厚度的典型外延

层的外延沉积步骤,并对所得的半导体晶片进行最终清洁。

44.施涂两种不同类型的外延前热处理:

45.实施例1:

46.从600℃开始,以 1℃/min的速率升温至850℃的目标温度,之后无需保持,立即以1℃/min的速率降温至600℃。

47.实施例2:

48.从600℃开始,以 1℃/min的速率升温至893℃的目标温度,之后无需保持,立即以1℃/min的速率降温至600℃。

49.比较实施例:

50.从600℃开始,以10℃/min的速率升温至700℃的温度,之后以1℃/min的速率升温至1000℃,之后无需保持,立即以10℃/min的速率降温至700℃。

51.外延半导体晶片在780℃的温度下进行3小时的热处理,并在600℃的温度下进行10小时的热处理之后,通过rie确定平均bmd密度。

52.通过tem确定,bmd的平均尺寸不超过20nm。

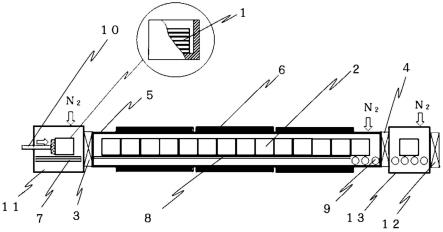

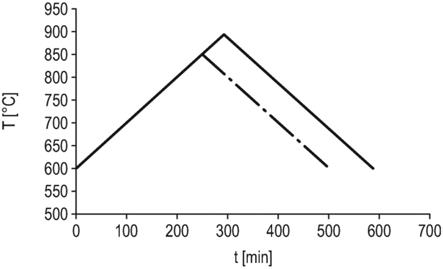

附图说明

53.图1示出了根据实施例1和实施例2的外延前热处理的温度变化速率。

54.图2示出了由热处理的目标温度所示的实施例1和实施例2的平均bmd密度。外延半导体晶片在780℃的温度下进行3小时的热处理,并在600℃的温度下进行10小时的热处理之后,通过rie确定平均bmd密度。

55.通过tem测定,bmd的平均尺寸不超过10nm。

56.图3示出了实施例1和实施例2的镍吸除效率(ge)。

57.吸除测试包括用镍对晶片进行可再现的旋涂污染,然后在氩气下,于600℃进行10小时金属驱入,最终冷却速率为3℃/min。然后,通过使用氢氟酸和硝酸的混合物逐步刻蚀,随后通过感应耦合等离子体质谱仪(icpms)分析相应的刻蚀溶液,来评估晶片表面上和晶片表面附近的金属分布。

58.图4显示了50个测试外延半导体晶片的lls测量结果,这些晶片在根据实施例1的外延沉积之前已经进行了热处理。尺寸大于50nm的lls的结果与图5所示的结果类似。

59.图5显示了50个测试外延半导体晶片的lls测量结果,这些晶片在外延沉积之前没有进行热处理。对于lls测量,在斜入射模式下使用kla-tencortechnologies corporation制造的sp3检测工具。

60.图6示出了bmd在深度方向上至约150μm的深度d的分布(正方形:

61.实施例1,菱形:实施例2)。

62.图7示出了实施例1的在深度方向上根据刻蚀尺寸(任意单位,a.u.)存在的位错环。位错环的存在对吸除效率至关重要。在外延层与半导体晶片之间的界面附近存在无位错环区域对于防止外延层中的缺陷至关重要。

63.图8示出了根据比较例的外延前热处理的温度变化速率。

64.图9是示出了根据比较例生产的外延半导体晶片上lls位置的图。本发明人认为,lls增加的数量与bmd平均尺寸的增加有关。

65.以上对优选实施方案的描述仅作为示例给出。根据所给出的公开,本领域技术人员不仅将理解本发明及其伴随的优点,而且还将发现对所公开的结构和方法的明显的各种变化和修改。因此,申请人寻求涵盖落入所附权利要求及其等同物所定义的本发明的精神和范围内的所有此类变化和修改。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。